# Микроконтроллер К1874ВЕ96Т. Первый отечественный 16-разрядный микроконвертер

В.А. Смерек, В.Н. Ачкасов, И.П. Потапов

ФГУП НИИЭТ, smerek@niiet.ru, niiet@vmail.ru, pip@niiet.ru

Аннотация — В статье описывается опыт разработки микроконтроллерной архитектуры, которая легла в основу нового микроконвертера разработки ФГУП НИИЭТ. Рассказывается о проблемах конструирования данного типа изделий и способах повышения вычислительных возможностей с учетом современных достижений в области САПР и технологий.

Ключевые слова — Микроконтроллер, микроконвертер, архитектура, ядро, энергопотребление, аналогоцифровое преобразование, цифро-аналоговое преобразование.

### І. Введение

Первый контроллер семейства MCS-96 появился в линейке фирмы Intel® в восьмидесятых годах прошлого столетия. Новая и высокопроизводительная для того времени архитектура предназначалась для построения схем, которые могли бы найти свое применение в различных областях: от изделий бытовой техники, периферийных устройств ЭВМ до автомобильной и авиационной электроники. Семейство полнилось контроллерами, было выпущено порядка 30 разновидностей частотой от 16 до 50 МГц. Все схемы принадлежали одному из классов: с блоком высокоскоростного ввода/вывода или со встроенным процессором событий. К моменту снятия с производства этого семейства в 2007 году, специалисты фирмы Intel® смогли увеличить адресное пространство с 64 Кбайт до 6 Мбайт, увеличить производительность более чем в 4 раза, увеличить объем ОЗУ в 4 раза, выпустить модификации, поддерживающие современные типы памяти и протоколы обмена информацией. Микроконтроллеры 80С196 фактически стали стандартом для встроенных систем управления, обеспечивая сочетание высоких технических показателей и экономической эффективности.

# II. Выбор базовой архитектуры

Когда в 2008 году инженеры ФГУП «НИИЭТ» инициативно приступили к разработке микроконвертера - контроллера, предназначенного для работы с аналоговыми сигналами, первым вопросом стал выбор ар-

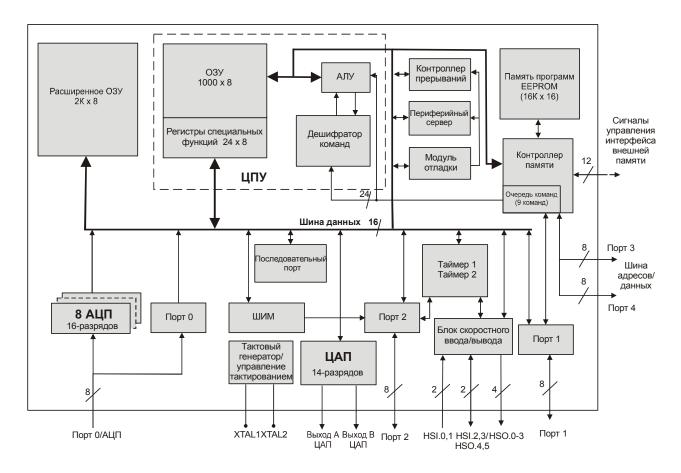

хитектуры, которая позволила бы сочетать высокую производительность с минимальными помехами, вносимыми в цепи аналоговых блоков. В номенклатуре предприятия уже были два 16-разрядных семейства, которые могли бы подойти для этих целей. Первое базировалось на ядре современной архитектуры С166. Оно хорошо подходило с точки зрения обеспечиваемой производительности, но большая занимаемая площадь, потребление и излишняя функциональность сделали его применение невозможным. Лицензирование стороннего ядра (например, ARM) делало разработку экономически невыгодной, особенно с учетом того, что работы проводились на собственные средства. Так как предприятие успешно выпускает и реализует контроллеры семейства MCS-96, давно нуждающиеся в модернизации, то было принято решение создать новое ядро, которое поддерживало бы систему команд контроллеров серии 1874, и было бы технологически независимым. Это позволило бы заменить старые схемы в современной аппаратуре, а также в последующем создать радиационно-стойкий вариант с расширенными функциональными возможностями сравнению с серийно выпускаемой ИС 1874ВЕ05Т). В качестве ориентира для всей системы на первом этапе была выбрана структура контроллера разработки ФГУП НИИЭТ 1874ВЕ76Т (аналог Intel® 8X196KC [1]).

## III. МЕТОДЫ ПОВЫШЕНИЯ ПРОИЗВОДИТЕЛЬНОСТИ

Основным требованием к разрабатываемому ядру стало увеличение производительности относительно референсной архитектуры при уменьшении общего энергопотребления цифровыми частями схемы. Последний вопрос предполагалось решить переходом на 0,35 мкм 3,3В технологию и использованием поддерживаемой современными САПР Low-Power методологии [2]. К сожалению, выбранная кремниевая фабрика не имела полного набора элементов для создания сверхнизкопотребляющей микросхемы. Основными способами уменьшения потребления и, как следствие, минимизации воздействия на работу аналоговых блоков, оставались следующие: введение

Рис. 1. Структурная схема микроконвертера К1874ВЕ96Т

элементов, блокирующих ветви дерева тактовых сигналов в моменты, когда не осуществляется перезапись, и изоляция операндов, позволяющая исключить излишние переключения комбинационных элементов схемы [3]. Эти способы автоматически поддерживаются современными средствами автоматизированного проектирования как при синтезе электрической схемы, так и при последующих операциях по разработке топологии. Проведенные расчеты показали, что применение только этих нехитрых для инженера методов, позволяет уменьшить потребление более чем в 3 раза. Так как некоторые функции контроллеров отдельными разработчиками систем не используются, то была введена возможность отключения от тактовых сигналов периферийных блоков полностью (в том числе и аналоговых), позволяющая использовать оптимальную схему энергопотребления в каждый момент функционирования системы. Этому способствует и введенный режим SLOW, позволяющий переводить конвертер в режим медленного внутреннего тактирования.

Основой для увеличения производительности нового ядра должен был стать полностью переработанный механизм выборки команд. Архитектура MCS-96

имеет потенциально высокую скорость работы с внутренней, а особенно с внешней памятью команд, при выборке из которой протокол предполагает всего 2 такта внутреннего синхросигнала на весь цикл обращения. Слабым местом оригинальных схем разработки фирмы Intel® являлось наличие относительно большого времени простоя как шины обращения к памяти команд, так и самого СРО. Причина этого видится в локальном рассогласовании между временем выборки и временем выполнения инструкций. Реализованная в оригинальных контроллерах очередь команд в 4 байта не всегда позволяет компенсировать эту разницу, а у разработчиков микроконвертера были идеи оптимизировать последовательность микрокоманд в каждой инструкции, по возможности уменьшив их время выполнения в циклах. Это привело бы к еще большему рассогласованию. Очередь команд была увеличена до 9 команд по 7 байт каждая. Непрерывность выборки и выполнения команд была обеспечена реализованной независимостью этих процессов на уровне блоков ядра. Механизм выборки извлекает программу из внутренней или внешней памяти, определяет начало и конец команд и выстраивает необходимую последовательность из инструкций.

Процесс прерывается только на обращения к данным из внешней памяти или в момент переполнения. СРU выбирает команды одну за одной из очереди, приостанавливая свою работу только тогда, когда полностью ее опустошит. Исследования показали, что для данной архитектуры такой подход позволяет почти полностью избежать простоев, увеличив тем самым эффективность использования как ресурсов ядра, так и памяти.

Следующим шагом было увеличение вычислительных возможностей будущей схемы. В последнее время идут процессы по стиранию грани между микроконтроллерами и цифровыми сигнальными процессорами - современные МК обычно имеют в своем составе специальные математические блоки, позволяющие существенно расширить их область применения. Входящие в пакет Cadence® ChipWare компоненты реализуют все наиболее востребованные математические операции, причем большинство из них на современных библиотеках стандартных элементов удается выполнять за 1 такт [4]. С помощью данных блоков было построено арифметически-логическое устройство микроконвертера, содержащее 1-тактные сдвигатели, 1-тактный умножитель (16х16), 2-тактный делитель (32х16) и другие блоки. Реализация быстрых умножения и деления, именно в рамках основного АЛУ, а не дополнительного вычислительного блока, было обусловлено желанием сделать доступными новые вычислительные возможности и для программ, использующих стандартные команды MCS-96 архитектуры.

Увеличившиеся вычислительные мощности обнажили другую проблему оригинальных контроллеров, а именно, недостаточный объем оперативного запоминающего устройства. Разработчиками была выбрана схема, достаточно распространенная в контроллерных архитектурах. Основной объем ОЗУ был установлен максимально возможным с учетом обеспечения программной совместимости с другими изделиями МСS-96 архитектуры (1000 байт). В дополнение к этому было введено отключаемое расширенное ОЗУ объемом 2 Кбайт. К этому ОЗУ возможно адресоваться только косвенными методами адресации, что немного дольше по времени, чем к основному ОЗУ, но намного быстрее, чем если использовать внешние запоминающие устройства.

Еще одним способом повышения эффективности использования внутренних ресурсов является использование специального блока для пересылки данных без прерывания работы основной программы. Для этого в архитектуре MCS-96 присутствует сервер периферийных транзакций (PTS). Блок оригинальных микроконтроллеров фирмы Intel® позволяет осуществлять транзакции по прерываниям периферийных устройств. Разработанный для микроконвертера блок позволяет осуществлять пересылку слов или байтов

исключительно в момент простоя внутренней шины адресов и данных, тем самым не приводя к изменению времени выполнения основного кода, доводя эффективность использования внутренних шин до 90-95 процентов. Это особенно актуально с учетом возросшего объема ОЗУ.

Проведенные тесты показали, что новое ядро выполняет тестовые программы на 30-40% быстрее по сравнению с оригинальной архитектурой при одинаковой частоте. При этом использование новых объемов памяти и функций позволит еще увеличить общую производительность системы. В принципе, можно говорить о появлении новой архитектуры, только базирующейся на системе команд МСS-96, так как структура блоков, входящих в состав ядра, их функционирование и характеристики полностью изменились.

#### IV. ОСОБЕННОСТИ ПЕРИФЕРИИ МИКРОКОНВЕРТЕРА

Так как основное назначение микроконвертера это работа с аналоговыми сигналами, то особое внимание уделялось разработке высокоточных аналогоцифровых и цифро-аналоговых преобразователей. В схему встроен блок из восьми 16-разрядных АЦП, представляющий собой ІР блок собственной разработки ФГУП НИИЭТ. Аналого-цифровые преобразователи построены на основе методики сигма-дельта преобразования, реализующей алгоритм сверхвыборки, когда норма осуществления выборки во много раз превышает требуемую частоту. Такая реализация позволяет значительно уменьшить шумы и гарантирует стабильно высокие динамические параметры преобразователя. Особое внимание при интеграции блока уделялось обеспечению программной совместимости с предыдущими контроллерами разработки института, что потребовало введение резервных сигналов управления. Блок 14-разрядного цифро-аналогового преобразователя реализован в виде ІР и отличается малым временем установки токовых выходов (11 нс). Аналоговые блоки были проверены в кремнии как отдельные устройства, что позволяет оценить степень влияния цифровой части схемы на качество и точность преобразований. При проектировании топологии микроконвертера особое внимание уделялось разводке аналоговых сигналов и шин аналогового питания. Они проложены вдалеке от сильношумящих, часто переключающихся сигналов, и имеют минимально возможную длину. Для этого использовались ручные методы трассировки, позволяющие хорошо контролировать весь процесс.

Оптимизации поверглись и периферийные устройства микроконвертера. Блок высокоскоростного ввода-вывода лишился ряда ограничений по скорости ввода и вывода цифровых сигналов, связанных с использованием ассоциативной памяти, уменьшилось

время реакции на прерывания. Этот модуль предназначен для фиксации времени происхождения событий и генераций событий по времени, и теперь разрешающая способность его стала равной одному машинному циклу. Для отладочных целей и контроля выполнения программ был введен модуль отладки, вырабатывающий новый тип прерывания. Использование этого блока позволяет реализовать режим защищенного микроконтроллера, запретив исполнение команд из внешней памяти. Все периферийные блоки подключаются к ядру по АМВА-подобной шине, протокол работы которой модифицировался специально для данной архитектуры. Это в последствии может обеспечить легкое подключение других периферийных IP блоков, ускорив разработку новых модификаций схемы.

#### V. Внутрикристальная память

Микроконвертер имеет в своем составе три типа памяти, предназначенных как для хранения данных в ходе выполнения программы, так и команд. Общий объем блоков составляет 35 Кбайт. Он делится между двумя типами ОЗУ (1000 байт и 2048 байт), доступ к которым осуществляется как пословно, так и побайтно, и памятью типа EEPROM (16Кх16). Хоть архитектура МСS-96 и является фон-неймановской, но выполнение команд из оперативных областей памяти запрещено. Память EEPROM может содержать как инструкции, так и данные, и может быть защищена установкой специальных битов, считывающихся каждый раз после перезагрузки микросхемы.

## VI. ТЕКУЩИЕ РЕЗУЛЬТАТЫ И ПЕРСПЕКТИВЫ РАЗВИТИЯ СЕМЕЙСТВА

В первом квартале 2010 года были получены первые образцы микроконвертеров. Это схемы, созданные по 0,35 мкм технологии фирмы X-FAB, и функционирующие на частотах до 33 МГц. Особенностью их является отсутствие аналого-цифровых преобразователей и расширенного ОЗУ. Они предназначены для первоначального ознакомления заинтересованными предприятиями и оценки возможности использования ИС в аппаратуре. Исследования показали, что разработчикам удалось добиться требуемых характеристик — максимальной частоты работы, величины потребляемого тока цифровой частью схемы и функциональности. Цифровая часть ИС потребляет менее 10 мА на частоте 33 МГц и работает при напряжении от 2 до 5 В.

По результатам измерений была проведена коррекция схемы, появление новых образцов микроконвертеров планируется на октябрь 2010 года.

Микроконвертер ФГУП НИИЭТ может начать новую линейку высокопроизводительных 16-разрядных контроллеров. Возможно появление изделий и с увеличенной тактовой частотой, объемом ОЗУ и ПЗУ, с новыми периферийными блоками, реализующими самые современные интерфейсы, многовыводных версий с расширенным адресным пространством и других. Основной принцип, положенный в разработку - технологическая независимость, позволит выпускать изделия на любой подходящей кремниевой фабрике, в том числе и отечественной. Проблема в том, что «контроллерные» технологии, отличаются от «процессорных», активно развивающихся в последнее время в России. Субмикронные технологии не пригодны к использованию там, где нужны повышенные напряжения питания (до 5В), широкие диапазоны функционирования, в том числе и периферийных блоков. Кремниевые фабрики должны предлагать не только библиотеки стандартных элементов (нескольких типов по потреблению и быстродействию), но и различные типы памяти, стандартные аналоговые блоки. Для современных изделий это доступно только на зарубежных производствах. Вся контроллерная тематика в России уходит на задний план, а между тем, это и есть самый потребляемый класс изделий, который и определяет технологическую развитость, как промышленности, так и жизни конкретного человека. О микроконтроллерах не любят вспоминать, так как здесь нет заоблачных частот, громадных объемов памяти и огромных производительностей. Между тем, даже западные производители электроники не боятся использовать простые 8-ми разрядные решения, встраивая их в самые современные и продаваемые системы. При этом сократить техническое отставание в этой области гораздо легче, чем в любой другой, а результаты могут быть куда заметней.

#### Литература

- [1] 8XC196KC/8XC196KD User's Manual, 1992, Order Number: 272238-001.

- [2] Low Power in Encounter RTL Compiler, March 2006.

- [3] Рабаи, Жан М., Чандракасан, Ананта, Николич, Боривож. Цифровые интегральные схемы, 2-е издание. : Пер. с англ. М. : ООО " И.Д. ВИЛЬЯМС ", 2007. 912 с. : ил. Парал. тит. англ.

- [4] Е.Д. Алперин, В.П. Крюков, В.А. Смерек Арифметикологические устройства и их синтез // Вестник Воронежского государственного технического университета. – 2009. – Т. 5. –№4.