# Особенности и результаты проектирования семейства LVDS КМОП 0,25/0,18/0,13 мкм передатчиков и приемников

В.Д. Байков $^1$ , Ю.М. Герасимов $^1$ , С.В. Кондратенко $^1$ , Т.В. Солохина $^2$   $^1$ Национальный исследовательский ядерный университет "МИФИ", kondsv@kaf3.mephi.ru  $^2$ ГУП НПЦ "ЭЛВИС"

Аннотация — В докладе обсуждаются особенности проектирования LVDS передатчиков и приемников, предназначены для использования последовательных линиях передачи данных типа SpaceWire и RapidIO со скоростью до 1 Гбит/с и по КМОП-технологии с 0,25/0,18/0,13 мкм. Представлена инвариантная к технологии методика проектирования передатчиков и приемников. Отмечена актуальность проблемы расширения диапазона рабочих частот LVDS трактов не только в сторону высоких, но и относительно низких частот, а также проблемы обеспечения предопределенного прикладными стандартами состояния тракта в особых ситуациях (обрыв или короткое замыкание на входе приемника). Рассмотрены различные варианты разрешения указанных проблем на практике. Приведены результаты моделирования и измеренные характеристики разработанных изготовленных LVDS передатчиков и приемников.

Ключевые слова — LVDS передатчики и приемники, RapidIO, SpaceWire, линия передачи, особые ситуации, IP блоки.

### І. Введение

Высокая скорость последовательной передачи данных, заложенная в стандарте LVDS (теоретически - до 1, 923 Гбит/с), благодаря самому принципу работы LVDS передатчиков и приемников сочетается с относительно малой потребляемой мощностью, малой чувствительностью к внешним помехам и низким уровнем собственных излучаемых помех, а также возможностью организации связи относительно больших расстояниях - до нескольких десятков или даже сотен метров, в зависимости от качества среды передачи и допустимого уровня снижения скорости передачи [1,2]. Поэтому универсальный (не привязанный к конкретным областям применения) стандарт LVDS используется в качестве основы для реализации физического уровня прикладных стандартов типа SpaceWire или RapidIO. В п.2 показано, как отдельные положения стандартов SpaceWire и RapidIO уточняют требования к LVDS передатчикам и приемникам, используемым в составе прикладных систем.

**LVDS** Проектирование высокоскоростных передатчиков и приемников представляет собой достаточно сложную техническую задачу, как и проектирование любых других приемно-передающих трактов с жесткими требованиями к характеристикам передачи данных и со значительной долей операций над аналоговыми сигналами. При этом нет такой уровнем прямой связи между используемой субмикронной технологии достижимым быстродействием (скоростью передачи), как это наблюдается в случае проектирования цифровых устройств. В результате для реализации LVDS передатчиков и приемников могут быть с успехом использованы различные варианты субмикронной КМОП-технологии, каждый из которых может иметь свои преимущества с точки зрения реализации систем на кристалле. Однако, в известной литературе преобладают частные подходы, а инвариантные к технологии методики проектирования LVDS передатчиков и приемников отсутствуют (или недоступны). Общие принципы такой методики, сформулированные процессе проектирования В семейства LVDS КМОП 0,25/0,18/0,13 передатчиков и приемников, изложены в п. 3 данной работы.

Основные усилия разработчиков LVDS передатчиков и приемников обычно направлены на компромисса между максимально достижение достижимой скоростью передачи и потребляемой при этом мощностью, в то время как в прикладных интерфейсах требуется обеспечение возможности нормальной работы LVDS тракта в широком диапазоне скоростей (от 2 Мбит/с до 400 Мбит/с для стандарта SpaceWire [3]). Кроме того, недостаточное внимание уделяться также

обеспечения предопределенного прикладными стандартами состояния тракта в особых ситуациях (обрыв или короткое замыкание на входе приемника и др. [1]). Указанные проблемы и способы их разрешения обсуждаются в п.п. 4 и 5.

В п. 6 данной работы представлен анализ соответствия характеристик разработанных и изготовленных IP-блоков LVDS передатчиков и приемников требованиям стандартов. Здесь же приведены общие выводы.

### II. LVDS и прикладные стандарты

LVDS интерфейс начал широко применяться с середины 90-x годов прошлого Соответствующий стандарт ANSI/TIA/EIA-644-A принят в 2001 г. Он определяет только электрические параметры сигналов (причем временные параметры гораздо менее жестко, чем амплитуды и уровни сигналов), не содержит требований к среде передачи (кабелю) и оставляет на усмотрение разработчиков прикладных систем способы обработки особых ситуаций в тракте передатчик-приемник [1,2]. Все это позволяет приспособить LVDS интерфейс к разным приложениям.

RapidIO развивается с 1997 г. как один из вариантов коммутационных структур последовательного типа (КСПТ). Первая версия стандарта, разработанного международной ассоциацией RapidIO Association, появилась уже в 1999 г. В отличие от LVDS, который фактически описывает только часть физического уровня, RapidIO - полноценный трехуровневый стандарт со своими протоколами и топологиями. RapidIO изначально рассматривался в перспективной системы связи встраиваемых компьютерных систем и сейчас проник на все наиболее важные рынки встраиваемой техники: военный, систем связи, хранения данных и обработки изображений [4]. Предусмотренные скорости передачи – от 500 до 2000 Мбит/с (до 5 Гбит/с и более при параллельном варианте соединений) обычно в пределах одной или нескольких соседних печатных плат (несколько десятков см). Таким образом. "теоретический предел" LVDS пο скорости оказывается превышенным. Существенно отличается от LVDS также организация передатчиков и приемников RapidIO, которые уже не образуют токовую петлю, а должны иметь близкие в номинальному значению 100 Ом выходное (для передатчика) входное (для приемника) дифференциальные сопротивления, причем между передатчиком и приемником могут опционально включаться разделительные конденсаторы [5].

SpaceWire – это перспективная технология построения распределенных гетерогенных бортовых

систем, прежде всего аэрокосмического назначения [6]. Имеет предшественника в виде стандарта МІС-Std-1553B (1973 г.), а в современном виде отражен в стандарте ECSS-E-50-12A (2003 г.), разработанном одним из комитетов Европейской ассоциации по стандартизации космических систем ECSS. Так же, RapidIO, SpaceWire полноценный многоуровневый стандарт (всего предусмотрено 6 уровней, соответствующих нижним пяти уровням модели ISO/OSI). Скорости передачи, как уже отмечалось во Введении, от 2 до 400 Мбит/с, расстояния – до 10 м. От стандарта LVDS позаимствованы не только параметры сигналов, но и сам принцип организации передачи этих сигналов от передатчика к приемнику (токовая петля). Проблему, как ни странно, создает необходимость реализации низкой скорости передачи из-за склонности к генерации приемника, нормально работающего в динамическом, но не в квазистатическом режиме. В стандарте SpaceWire [3] определено, что в особых ситуациях (обрыв или короткое замыкание на входе приемника) на его выходе должен устанавливаться высокий электрический уровень. Кроме того, при отсутствии питания передатчика его выход должен находиться в высокоимпедансном состоянии; в таком же состоянии в отсутствии питания должен находиться и вход приемника. Эти требования, очевидно, непосредственно влияют на реализации LVDS передатчиков и приемников в составе прикладных систем.

## III. ИНВАРИАНТНАЯ К ТЕХНОЛОГИИ МЕТОДИКА ПРОЕКТИРОВАНИЯ

Хотя типовой размах дифференциальных сигналов на выходе LVDS передатчика составляет только 0,35 В, их средний (синфазный) уровень достаточно высокий (1,25 В). Кроме того, тракт передатчикприемник должен нормально работать при синфазном напряжении в линии передачи ±1 В. Поэтому минимальное напряжение питания элементов, работающих непосредственно на линии, должно быть не ниже 2,5 В. Для решения задачи проектирования семейства LVDS передатчиков и приемников, изготавливаемых ПО одному из вариантов субмикронной КМОП-технологии, необходимо, чтобы каждый из этих вариантов имел опциональную транзисторов использования возможность повышенным (по сравнению c основным) напряжением питания не менее 2,5 В. Для доступных в рамках текущих разработок КМОП-технологий с нормами 0,25/0,18/0,13 мкм таким повышенным напряжением является напряжение 3,3 В. Таким образом, разрабатываемые LVDS передатчики и приемники независимо от конкретного варианта

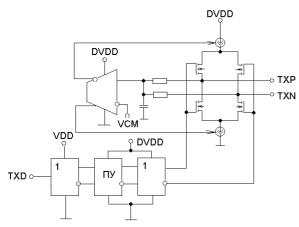

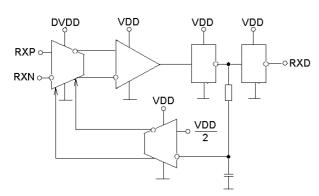

технологии должны иметь ядро с повышенным напряжением питания 3,3 В и периферийные блоки с различными напряжениями питания (2,5/1,8/1,2 В, соответственно, для технологий с нормами 0,25/0,18/0,13 мкм). Обобщенные функциональные схемы LVDS передатчика и приемника показаны на рис. 1 и 2. На этих схемах VDD=2,5/1,8/1,2 В, DVDD=3,3 В, VCM=1,25 В. ПУ – преобразователь логических уровней. Цепи обеспечения работы в режиме пониженного энергопотребления не показаны.

Рис. 1. Обобщенная функциональная схема LVDS передатчика

Рис. 2. Обобщенная функциональная схема LVDS приемника

Как передатчик, так и приемник используют цепи отрицательной обратной связи (ОС). В передатчике ОС поддерживает средний (синфазный) уровень выходных сигналов вблизи номинального значения VCM. приемнике цепь OC обеспечивает поддержание среднего значения сигнала на входе второго из инверторов вблизи половины напряжения питания VDD/2, что позволяет улучшить скважность сигнала на выходе RXD (при передаче меандра приблизить ее к двум). Как показали результаты расчетов И измерений, благодаря действию описанных приемник OC. передатчик

автоматически подстраивают свои параметры под требования стандарта LVDS, однако, при низких скоростях передачи данных может возникнуть проблема обеспечения устойчивости приемника (см. п. 4).

## IV. ОБЕСПЕЧЕНИЕ НОРМАЛЬНОЙ РАБОТЫ LVDS ТРАКТОВ ПРИ НИЗКИХ СКОРОСТЯХ ПЕРЕДАЧИ ДАННЫХ

Генерация LVDS приемника при низких скоростях передачи данных является непосредственным следствием задержки сигнала ОС. Основной вклад в задержку вносит RC-цепь (см. рис. 2). В исходном варианте приемника, изготовленного по технологии  $0.18\,$  мкм,  $\tau = RC \approx 0.36\,$  мкс, что соизмеримо с периодом Т передаваемого сигнала (меандра) с частотой 3 МГц. Измерения показали генерацию на выходе приемника при частоте передаваемого сигнала 2,2 МГц и ниже, что близко к оценочному значению. Увеличение целью низкочастотной генерации приемника нежелательно по двум причинам. Во-первых, при этом требуется использовать резистор R и/или конденсатор С достаточно больших номиналов, которые занимают заметное место на кристалле. Во-вторых, при  $\tau >> T$ ухудшается форма воспроизводимого на выходе приемника реального сигнала RXD, который может заметно отличаться от меандра (содержать длинные цепочки из логических 0 и 1). Более того, на таких участках передаваемого сигнала с пониженной частотой снова может возникнуть генерация. В стандартах, использующих LVDS прикладных интерфейс, длинные цепочки из логических 0 и 1, как известно, исключаются на системном уровне для обеспечения свойства самосинхронизируемости принимаемых сигналов. Тем не менее, проблема низкочастотной генерации требует кардинального решения, так как генерация может возникнуть в том числе в особых ситуациях.

Были опробованы разные доступные способы изменения схемы приемника. Контролировалось поведение тракта передатчик-приемник при низкочастотном сигнале TXD (меандр с периодом 20 контроль отсутствия генерации), мкс. высокочастотном сигнале ТХD (меандр с периодом 5 нс, контроль скважности) и поведение сигнала на выходе приемника при разрыве связи с передатчиком (100 Ом на входе, контроль отсутствия генерации и уровня выходного сигнала RXD – должен быть равен 1). По результатам расчетов в схему приемника внесены следующие изменения:

1. Уменьшена глубина ОС – снижена крутизна транзисторов в составе ОУ, усиливающих сигнал ОС. Это позволило повысить устойчивость схемы.

- 2. Изменена структура ОС используется парафазный сигнал ОС вместо однофазного (см. рис. 2). Это повысило эффективность действия ОС (то есть реализацию ее основной функции) даже с учетом снижения глубины ОС.

- 3. Организован "перекос" размеров транзисторов в дифференциальном каскаде на входе первого ОУ в тракте обработки сигналов в схеме приемника (см. рис. 2). Общая ширина каналов этих транзисторов W составляет 140 и 64 мкм (при минимально-возможной в данном случае длине канала L=0,18 мкм). Этот способ оказался наиболее эффективным, так как он позволил не только устранить низкочастотную генерацию, но и обеспечить нужное состояние выхода приемника в особых ситуациях.

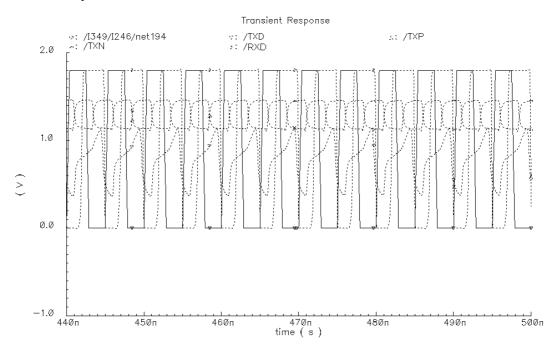

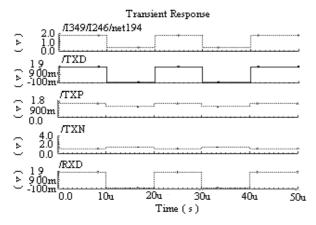

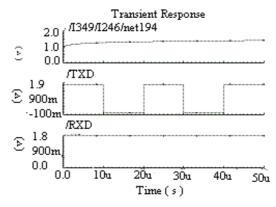

Результаты моделирования измененного передатчик-приемник приведены на рис. Контроль при высокочастотном сигнале (рис. 3) показал снижение размаха сигнала в узле net194 на входе первого инвертора и небольшое ухудшение изза этого скважности сигнала RXD. Контроль при сигнале низкочастотном (рис. 4) подтвердил отсутствие генерации на выходе RXD. Исследование поведения сигнала на выходе приемника при разрыве связи с передатчиком (рис. 5) показало отсутствие генерации и правильный уровень выходного сигнала RXD, а также далекое от напряжения переключения значение сигнала net194 на входе первого инвертора.

Рис. 3. Контроль при высокочастотном сигнале TXD

Рис. 4. Контроль при низкочастотном сигнале TXD

Рис. 5. Поведение сигнала на выходе приемника при разрыве связи с передатчиком

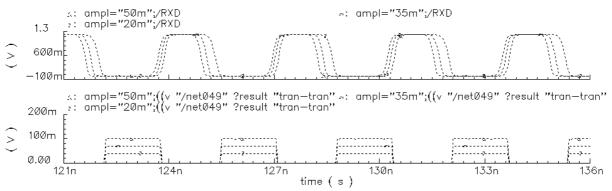

Потенциальным следствием "перекоса" размеров транзисторов в дифференциальном каскаде является снижение чувствительности приемника. На рис. 6 примера приведены в качестве результаты исследования чувствительности приемника, изготавливаемого по технологии 0,13 мкм, после внесения указанных изменений. Из анализа рис. 6 следует, что чувствительность приемника отвечает требованию стандарта LVDS - при разностном входном сигнале с амплитудой 100 мВ приемник нормально работает. Он работает также и при меньших амплитудах входного сигнала (по-крайней мере, начиная с 20 мВ), однако, при этом заметно ухудшается (увеличивается) скважность выходного сигнала RXD.

## V. Обработка особых ситуаций

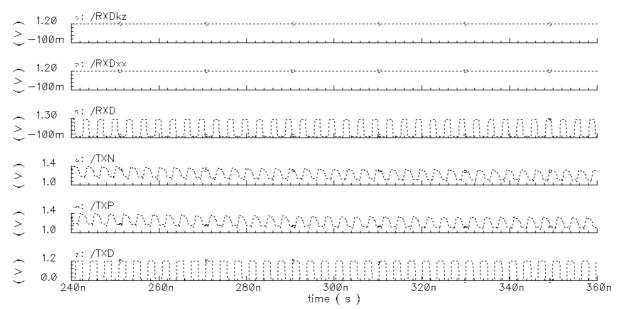

Были выполнены более детальные исследования поведения тракта передатчик-приемник в особых ситуациях и в рабочем режиме при высокочастотном входном сигнале TXD (уже после внесения описанных ранее изменений в схеме приемника). Как следует из анализа рис. 7, на выходе приемника устанавливается, как это и требуется в стандарте SpaceWire, сигнал высокого уровня как в случае короткого замыкания на входе приемника (на выходе RXDkz), так и в случае холостого хода (на выходе RXDxx). Анализ рис. 7 показывает также сохранение хорошей скважности сигнала RXD даже при предельно высоких скоростях передачи (около 1,2 Гбит/с в данном случае).

Рис. 6. Результаты исследования чувствительности приемника, изготавливаемого по технологии 0,13 мкм, после внесения изменений в схему (снизу показан разностный входной сигнал приемника)

Рис. 7. Результаты исследования поведения тракта передатчик-приемник в особых ситуациях и в рабочем режиме при высокочастотном входном сигнале TXD

## VI. Результаты экспериментальных исследований и выводы

Разработанные и изготовленные IP-блоки LVDS передатчиков и приемников по КМОП технологиям с нормами 0,25/0,18/0,13 мкм имеют основные соответствующие требованиям параметры, стандартов LVDS и SpaceWire, и могут быть, при необходимости, доработаны для удовлетворения также и требований стандарта RapidIO (см табл. 1). проблему представляет Основную vвеличение достижимой скорости передачи в паре передатчикприемник до уровня 2000 Мбит/с и выше. Результаты исследований показывают [7], что такое увеличение скорости возможно при использовании стандартной 0,18 мкм КМОП-технологии, причем оно проще достигается для приемника, чем для передатчика.

Таким образом, подтверждена возможность реализации IP-блоков LVDS передатчиков и приемников, удовлетворяющих жестким требованиям прикладных стандартов, в которых применяется высокоскоростная последовательная передача данных.

### Литература

- [1] Electrical characteristics of Low Voltage Differential Signaling (LVDS) interface circuits // TIA PN-4584, Revision 1.2, May 2000, 37 p.

- [2] Булыгин Л., Оганов В. Построение скоростного последовательного межблочного канала обмена данными // Электронные компоненты. 2005. №2. С. 1-3.

- [3] SpaceWire: serial point-to-point links. Draft // ECSS-E-50-12 Space Engineering, May 2000, 100 p.

- [4] Слепов Н. RapidIO коммутационная структура последовательного типа // ЭЛЕКТРОНИКА: Наука. Технология. Бизнес. 2006. №5. С. 76-89.

- Технология. Бизнес. 2006. №5. С. 76-89.

[5] RapidIO<sup>TM</sup> Interconnect Specification. Part 6: LP-Serial Physical Layer Specification // RapidIO Trade Association, Rev.2.1,08/2009, 362 p.

- [6] Шейнин Ю., Солохина Т., Петричкович Я. Технология SpaceWire для параллельных систем и бортовых распределенных комплексов // ЭЛЕКТРОНИКА: Наука. Технология. Бизнес. 2006. №5. С. 64-75.

- [7] Xihu W., Longsheng W., Youbao L. Low-power LVDS I/O interface for above 2 Gb/s-per-pin operation // Journal of Electronics (China). − 2009. V. 26. №4. P.525-531.

Таблица 1 Анализ соответствия параметров разработанных и изготовленных IP-блоков требованиям стандартов

|                                                                                         |                                                         |          |      |                        | Отметка о реализации |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------|----------|------|------------------------|----------------------|

| Параметр                                                                                | Обозначение и                                           | Диапазон |      |                        | требований в IP-     |

|                                                                                         | размерность                                             | Мин.     | Тип. | Макс.                  | блоках               |

| Дифференциальное выходное напряжение                                                    | V <sub>OD,</sub> мВ                                     | 247      | 350  | 454                    | +                    |

| Опорное напряжение                                                                      | V <sub>OS</sub> , B                                     | 1,125    | 1,25 | 1,375                  | +                    |

| Нестабильность дифференциального выходного напряжения                                   | $\Delta V_{\mathrm{OD,}}$ мВ                            |          |      | 50                     | +                    |

| Нестабильность опорного напряжения                                                      | $\Delta V_{OS,}$ мВ                                     |          |      | 50                     | +                    |

| Ток короткого замыкания                                                                 | $I_{SA}$ , $I_{SB}$ , $MA$                              |          |      | 24                     | +                    |

| Время фронта/спада                                                                      | t <sub>R</sub> /t <sub>F,</sub> HC                      | 0,26     |      | 1,5                    | +                    |

| Требования стандарта ANSI/TIA/EIA-644 для LVDS приемника                                |                                                         |          |      |                        |                      |

| Диапазон входного напряжения                                                            | $V_{IN, B}$                                             | 0        |      | 2,4                    | +                    |

| Входной ток                                                                             | I <sub>IN,</sub> мкА                                    |          |      | 20                     | +                    |

| Пороговое напряжение                                                                    | V <sub>тн,</sub> мВ                                     |          |      | ±100                   | +                    |

| Требования стандарта RapidIO на физическом уровне (отличия и дополнения стандарта LVDS) |                                                         |          |      |                        |                      |

| Скорость передачи                                                                       | 500 - <b>2000</b> Мбит/с                                |          |      | ± (до 1Гбит/c)         |                      |

| Реализация передатчика и приемника                                                      | отличается от LVDS                                      |          |      | ± (требуется коррекция |                      |

|                                                                                         |                                                         |          |      | схемы передатчика)     |                      |

| Требования/рекомендации стандарта SpaceWire на физическом уровне (отличия и дополнения  |                                                         |          |      |                        |                      |

| стандарта LVDS)                                                                         |                                                         |          |      |                        |                      |

| Скорость передачи                                                                       | 2 - 400 Мбит/с                                          |          |      | +                      |                      |

| Предопределенное состояние на выходе                                                    | на выходе приемника должен                              |          |      | +                      |                      |

| приемника в особых ситуациях (обрыв или                                                 | устанавливаться высокий                                 |          |      |                        |                      |

| короткое замыкание на его входе)                                                        | электрический уровень                                   |          |      |                        |                      |

| Потребляемая мощность передатчика и приемника при максимальной скорости передачи        | не более 50 мВт (рассматривается как типичное значение) |          |      |                        | +                    |