# Особенности методов проектирования систем питания высокопроизводительных микропроцессоров на этапе физического проектирования кристалла

### Я.Н. Мороз

ОАО "Институт электронных управляющих машин им. И.С. Брука"

### ЗАО «МЦСТ», moroz@mail.ru

Аннотация — В данной статье представлены методы создания универсальных надёжных систем питания для современных сложно-функциональных цифровых СБИС на уровне кристалла. Отмечены особенности физического проектирования систем питания микропроцессоров с архитектурой "ELBRUS" или "SPARC".

Ключевые слова — системы питания для современных цифровых СБИС, методы разработки СБИС, физическое проектирование сложно-функциональных СБИС, микропроцессоры.

### І. Введение

Современное проектирование сложнофункциональных высокопроизводительных цифровых СБИС включает в себя несколько стадий. Одной из таких стадий является физическое проектирование СБИС, которое включает в себя несколько этапов, составляющих называемый так маршрут проектирования ("Design Flow"). В маршруте строго определена последовательность действий и их взаимосвязь. Если говорить 0 полузаказном физическом проектировании, то есть проектировании на основе библиотек готовых ІР-блоков и логических элементов, маршрут будет состоять из следующих основных этапов:

- синтез перевод СБИС с уровня регистровых передач ("Register transfer level RTL" на языках Verilog/VHDL) на уровень описания СБИС на основе реальных логических элементов и их взаимодействия ("gate-level").

- Планирование топологии СБИС.

- Проектирование системы питания.

- Размещение всех логических элементов СБИС, оптимизация по ключевым параметрам.

- Проектирование системы синхронизации.

- Трассирование всех связей СБИС, оптимизация по ключевым параметрам.

Физическая «верификация» - проверки "DRC", "ERC/ARC", "LVS" и другие проверки проектируемой интегральной схемой перед этапом изготовления.

Из маршрута видна строгая последовательность этапов, которой невозможно пренебречь. Проектирование системы питания, как и планирование топологии СБИС, имеет основополагающее значение. От организации системы питания так или иначе будут ключевые параметры энергопотребление, площадь и даже быстродействие. В настоящее время проектирование СБИС происходит на основе технологий «глубокого субмикрона», с характеристическими нормами 90 нанометров и ниже. На первый план, помимо быстродействия, выходят такие параметры как целостность сигнала, устранение шумов и помех [1], устранение нежелательных эффектов электромиграции, снижение активного омического падения напряжения (далее "IR-drop" или Vir). Неправильная организация системы питания может вообще привести к неработоспособности всей СБИС или отдельных её частей. Согласно последним данным, полученным в процессе проектирования, производства эксплуатации современных И интегральных высокопроизводительных сложных схем, проблеме организации и оптимизации систем питания на уровне кристалла уделяется все большее внимание[2]-[4].

## II. ОСНОВНЫЕ МЕТОДЫ ПОСТРОЕНИЯ СИСТЕМ ПИТАНИЯ НА УРОВНЕ ФИЗИЧЕСКОГО ПРОЕКТИРОВАНИЯ МИКРОПРОЦЕССОРА

Строго говоря, современный микропроцессор - это структура, образованная кристаллом микропроцессора и подложкой, обеспечивающей его соединение с печатной платой [5]. Поэтому, помимо системы питания внутри кристалла, существует много важных факторов, влияющих на отказоустойчивость микропроцессора. Например, стабильность питания: как только уровень помех по питанию превышает допустимый предел, приходится либо снижать тактовую частоту, что уменьшает

производительность, либо повышать напряжение питания, что негативно влияет на надежность, так как флуктуации в напряжении питания схемы ухудшают помехозащищенность элементов и вносят помехи в схему, увеличивая вероятность сбоев. Основными источниками помех являются высокочастотные микросхемы, такие как микропроцессоры, память, чипсет. Свою долю в падение напряжения вносит и корпус микропроцессора за счет индуктивности проводов, соединяющих корпус и контактные площадки микросхемы. Конечное напряжение на элементах в результате рассчитывается по формуле:

$$V = Vdd - L\frac{dI}{dt} - Vir, \qquad (1)$$

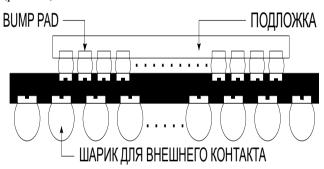

где Vdd - номинальное напряжение питания процессора, Vir - активное омическое падение напряжения, L(dI/dt) - падение напряжения на контактных индуктивности плошалок. Олнако "МЦСТ" применяемая в разработках компании технология корпусирования "Flip-chip" всех своих достоинств, минимизировать оба негативных параметра (L\*(dI/d) и Vir). Падение напряжения на элементах по сравнению с номинальным приводит к различным негативным последствиям. Например, может увеличиваться время переключения элементов [6]: для технологии 90 нм. и номинального напряжения 1 В, уменьшение напряжения питания на 0.1 В приводит к увеличению задержек на 25%.

Структура системы питания внутри кристалла зависит от многих параметров. Существенное влияние оказывает методология планирования топологии кристалла.

Для планирования топологии микросхемы, как правило, используется два основных метода: с использованием иерархии и без использования иерархии. У каждого из методов есть достоинства и недостатки и это тема достойна отдельного доклада [7]. Общий план построения системы питания внутри кристалла можно представить следующим образом:

- построение системы питания на верхнем уровне иерархии кристалла микропроцессора, подключение к контактным площадкам ("Bump Pad"), идущим на корпус микросхемы.

- Построение системы питания на уровне отдельных устройств кристалла микропроцессора.

Подключение стандартных логических элементов и элементов памяти.

- Согласование и связь систем питания на разных уровнях кристалла микропроцессора.

Выбор и организация оптимальной системы распределения питания являются ключевым моментом в достижении оптимальной мощности, как отдельных устройств, так и всей микросхемы в целом.

Для некоторых специализированных микросхем, например микросхем, используемых для мобильных приложений, минимизация мощности выходит на первый план, наряду с быстродействием. Мощность, потребляемая микросхемой, изготовленной на основе CMOS технологии, разделяется на статическую и динамическую:

$$Ptot = Pdyn + Pstat, (2)$$

где Ptot — общая, потребляемая мощность; Pdyn — динамическая; Pstat — статическая. Pdyn рассеивается при переключении логических элементов микросхемы в различные состояния. Pstat, в отличие от Pdyn, потребляется всегда, когда на микросхему подано питание и не зависит от активности внутренней логики. Величина Pdyn, как правило, существенно выше Pstat, поэтому снижению динамической составляющей уделяется наибольшее внимание.

Существует несколько различных вариантов реализации систем распределения питания. Наиболее распространены две структуры: кольцо («ring») и сетка («mesh»). В сложных интегральных системах на кристалле с большой площадью, одновременно используются оба метода [5], [2].

Структура типа кольцо, как правило, используется для связи контактов на верхнем уровне иерархии микропроцессора. кристалла Сетка питания используется для того, чтобы сделать систему распределения питания более надежной, снизить плотности токов и падение напряжения на шинах. ШИН земли и питания, Сетка состоит из расположенных в нескольких слоях металлизации. В каждом слое металлизации выбирается направление шин питания и земли (вертикальное или горизонтальное), с помощью моделирования теоретических расчётов выбираются ширина шин и шаг сетки. Наилучшие результаты показывает система распределения питания в виде сетки, в сочетании с расположением контактных площадок по площади кристалла и с использованием технологии корпусирования "Flip-chip". Для современных СБИС с технологическими нормами 90нм и ниже, работающих на частотах свыше 1Ггц, приходится постоянно учитывать все большее количество параметров, которые не так важны на меньших частотах или технологиях с большими размерами.

### III. СИСТЕМА ПИТАНИЯ МИКРОПРОЦЕССОРОВ С APXИТЕКТУРОЙ "ELBRUS" ИЛИ "SPARC" НА УРОВНЕ ФИЗИЧЕСКОГО ПРОЕКТИРОВАНИЯ КРИСТАЛЛА

Рассмотрим конкретную реализацию системы питания внутри кристалла на примере микропроцессора «Эльбрус-S» с архитектурой "ELBRUS" и 4-х ядерный МЦСТ R1000 (МЦСТ-4R) с архитектурой "SPARC v9" на технологии 90нм.

Помимо всех вышеперечисленных параметров, проектируемая система питания кристалла должна была быть универсальна по отношению к архитектуре

и к разным условиям дальнейшей эксплуатации. Кроме того, необходимо было существенно снизить время проектирования до нескольких месяцев и снизить риски выхода микросхемы из строя в связи с возможными нарушениями в системе питания [5], [3], при этом обеспечить достаточную трассировочную способность для сигнальных проводов.

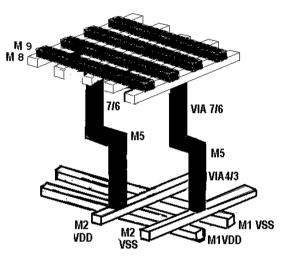

Перед тем, как приступить к описанию реализации системы распределения питания, введем некоторые обозначения и определения. Первый слой металлизации, самый нижний, - М1, последний, девятый — М9. Нумерация слоев начинается «снизу», от кремниевой основы микропроцессора. При этом соблюдается строгая направленность в пределах каждого слоя: четные слои имеют вертикальное направление трассировки, нечетные - горизонтальное.

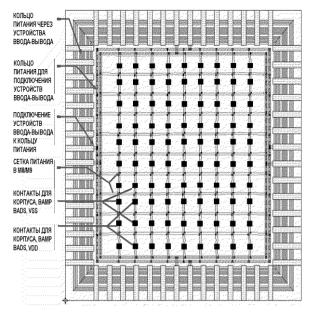

Шины земли и питания в М9 чередуются и расположены горизонтально. В М8 также чередуются и расположены вертикально. В свою очередь шины в М9 подключаются к корпусу микросхемы через контактные площадки «Витр Pad's», расположенные по всей площади кристалла для реализации технологии корпусирования "Flip-chip", см. рис. 1.1 и рис. 1.1a. Через массив межслойных контактов питание и земля из М8 подключаются к вертикальным шинам в М2 с помощью контактов в М5. Из М2, также через межслойные контакты, происходит подключение с М1, где в виде горизонтальных шин земля и питание равномерно распределяются между стандартными логическими элементами микросхемы (рис. 1.2).

Рис. 1.1. Технология Flip-chip

Рис. 1.1a. Структура основной сетки питания и расположение в шахматном порядке контактных площадок («Bamp Pads»)(8-9 слои металлизации), вид

Рис. 1.2. Структура сетки питания в разрезе всего кристалла, цифрами обозначены слои металлизации. Стандартные логические элементы будут располагаться между двумя нижними шинами земли и питания в М1

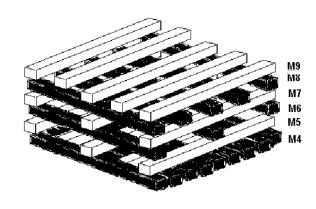

Рис. 1.2a. Структура сетки питания над элементами памяти. Внутренняя система питания находится в М4

Для организации системы питания в областях расположения элементов памяти был реализован другой тип сетки. Внутренняя система питания элементов памяти представляет из себя большой набор последовательных шин земли и питания в слое М4. Прямое подключение всех этих шин к верхними слоям М8/М9 приводило к невозможности трассировки сигнальных проводов в промежуточных слоях М5-М7. Поэтому над элементами памяти достраивалась некоторая промежуточная разреженная сетка в М5-М7 (рис. 1.2а). Благодаря такому подходу обеспечивалось надёжное распределение питания, а трассировочная способность в этих областях в соответствующих слоях металлизации уменьшалась всего на 15-20% по сравнению с сеткой в областях размещения стандартных логических элементов, показанной на рис. 1.2.

На параметры сетки (шаг и ширина шин, используемые слои металлизации) влияет множество факторов. Наибольшее влияние на общую площадь металла, отводимую под сетку, оказывают требования норм и правил проектирования, и требования по трассировочной способности сигнальных проводов. Разреженная сетка оставляет достаточно места для проведения сигнальных трасс, но увеличивает IR-drop и электромиграцию. Для наилучшего распределения питания от корпуса микропроцессора внутрь кристалла было принято решение использовать трассировочную способность верхних слоев М8/М9, не нарушая при этом требование по плотности заполнения. Для технологии 90нм. ширина шин составила 6мкм., а расстояние между соседними шинами - 2мкм. В результате моделирования и руководствуясь требованиями поставщиков элементов памятей, для шин в слоях М5-М7 ширина шин составила 3мкм, расстояние между соседними шинами - 11мкм, рис. 1.2а. Промежуточные шины в М5 и М2, для распределения питания между стандартными элементами также были получены в результате моделирования и исходя из обеспечения максимальной трассировочной способности. Ширина шин в М2

составила 3мкм, расстояние между разноименными шинами 0.5мкм, между одноименными – 80мкм.

### IV. РЕЗУЛЬТАТЫ ИССЛЕДОВАНИЙ И РЕКОМЕНДАЦИИ ПРОЕКТИРОВАНИЯ

Моделирование и проектирование сетки питания осуществлялось с помощью САПР компании "Synopsys". Исследование падения напряжения, потребляемой динамической мощности и нарушений по электромиграции в системе питания на уровне кристалла для технологии 90нм при средней температуре 125°С, номинальном напряжении Vdd = 1В приводятся в таблицах 1 и 2. Исходя из опытов предыдущих разработок, во время моделирования средняя частота переключения элементов предполагалась один раз в 5 тактов.

Тип сетки питания на уровне кристалла микропроцессора, реализованного в вышеперечисленных проектах, соответствует всем нормам физического проектирования, удовлетворяет технологическим нормам проектирования и позволяет получить технические характеристики проектируемых микропроцессорным системам согласно техническому заланию.

Таблица 1

«Эльбрус-S»

| Моделирование. Средняя частота     |

|------------------------------------|

| переключения элементов 100 Мгц ( 1 |

| переключение в 5 тактов)           |

| Vir, по   | Vir, по  | Pdyn, Вт | Нарушения,  |

|-----------|----------|----------|-------------|

| земле, мВ | питанию, |          | электромигр |

|           | мВ       |          | ация        |

| 14,5      | 14,3     | 20       | 0           |

| Измерения |          |          |             |

| после изг |          |          |             |

| Мгц       |          |          |             |

| Vir, по   | Vir, по  | Pdyn, Вт |             |

| земле, мВ | питанию, |          |             |

|           | мВ       |          |             |

| ~20       | ~20      | 17.6     | 0           |

Таблица 2

Одно ядро «МЦСТ R1000» (МЦСТ-4R)

| Модели                             |            |          |            |

|------------------------------------|------------|----------|------------|

| переключения элементов 200 Мгц ( 1 |            |          |            |

| переключение в 5 тактов)           |            |          |            |

| Vir, по                            | Vir, по    | Pdyn, Вт | Нарушения, |

| земле,                             | питанию,   |          | электромиг |

| мВ                                 | мВ         |          | рация      |

| 19                                 | 17,3       | 9        | 0          |

| Измерения на рабочем кристалле     |            |          |            |

| после изго                         |            |          |            |

| Vir, по                            | Vir, по    | Pdyn, Вт |            |

| земле,мВ                           | питанию,мВ |          |            |

| ~20                                | ~20        | 11.6     | 0          |

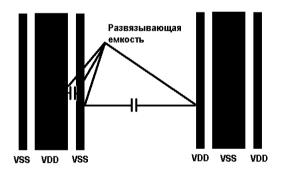

Падение напряжение Vir, приведённое в таблице, соответствует среднему значению из определённого множества значений. Обеспечивая системы питания, помимо среднего значения необходимо учитывать пиковые значения и по возможности их снижать. Согласно современным исследованиям в области снижения падения напряжения [3-8] активно используется метод развязывающей емкости. Причём можно использовать явную емкость в виде конденсаторов [5], [9] а можно использовать емкость шин в системе питания [8].

Исследования различных вариантов организации сетки питания на уровне кристалла микросхемы показали, что с целью снижения как среднего так и пикового значения Vir, необходимо применять сетку, в которой посредством рядом стоящих шин земли и развязывающая образуется питания ("decoupling capacitance"). Из-за ограничений по трассировочной способности в вышеописанных проектах эффект развязывающей емкости, получаемый между разноимёнными шинами питания, наиболее хорошо реализован в верхних слоях М8/М9. Но и в слое М2 шины земли и питания размещались парой с минимально допустимым расстоянием между собой -0.5мкм (рис. 1.2). Следующая пара шин располагалась через 80мкм. Такой подход обеспечивал хорошую трассировочную способность сигнальных ДЛЯ проводов и уменьшение как средних, так и пиковых значений Vir.

Пο данным использование статьи [8] развязывающей емкости между шинами земли и питания как в пределах одного слоя, так и между слоями, снижает шумы по питанию в 3 раза по сравнению с обычной системой питания чередующихся шин. Для следующих проектов рекомендуется использовать систему питания в виде сетки, которая помимо частых шин в верхних трассировочных слоях имеет в более низких слоях структуру, показанную на рис. 2 для вертикальной направленности. Аналогичную структуру следует создавать И для горизонтальных слоев.

Рис. 2. Структура сетки в пределах одного слоя металлизации для вертикальной направленности

таблице представлены результаты моделирования устройства проектируемого 65нм. Средние значения технологии напряжения (Vir\_avg) уменьшаются на 15-20%, а пиковые значения (Vir\_max) падают более, чем на 30%. При этом трассировочная способность ухудшается не более, чем на 10-15%.

Исходя из результатов моделирования, для следующих проектов с целью уменьшения Vir рекомендуется использовать структуру сетки питания, представленную на рис.2.

Таблица 3

Моделирование кэша второго уровня из состава микропроцессора проектируемого на технологии 65нм. Средняя частота переключения элементов 200 Мгц (1 переключение в 5 тактов)

| Полученные парам  |             |            |

|-------------------|-------------|------------|

| для сетки п       |             |            |

| дополнительных, « |             |            |

| ши                |             |            |

| Vir_avg/ Vir_max, | Vir_avg/    | Нарушения, |

| по земле, мВ      | Vir_max, по | электромиг |

| ·                 | питанию, мВ | рация      |

| 7 / 96            | 12 / 58     | 0          |

| Полученные парам  |             |            |

| для сетки         | питания с   |            |

| дополнительными   |             |            |

| «развязывающими»  |             |            |

| Vir_avg/ Vir_max, | Vir_avg/    | Нарушения, |

| по земле, мВ      | Vir_max, по | электромиг |

|                   | питанию, мВ | рация      |

| 6 / 49            | 10 / 46     | 0          |

Кроме вышеописанных методов организации систем питания внутри кристалла, существуют проблемы организации питания на верхнем уровне. На рисунке 1.1а видно, что питание нужно как для ядра микросхемы, основной логики, так и для периферии, устройств ввода вывода. Из анализа систем питания микросхем компании ЗАО «МЦСТ» следует, что для обеспечения большей надёжности и уменьшения энергопотребления необходимо разделять питание периферии и ядра на уровне разработки кристалла, выделяя для этих целей разные контактные площадки («Bamp Pads»). Далее на этапе корпусирования и во время монтажа микросхемы на печатную плату необходимо обеспечить соответствующее разделение по питанию и удовлетворить всем технологическим нормам проектирования. Это весьма трудоемкая и ответственная задача [9].

Во 2-м разделе было обращено внимание на особенности проектирования системы питания, учитывая топологию кристалла [7]. Основная трудность возникала при согласовании питания между блоками и верхним уровнем иерархии, а также при

равномерном распределении контактных площадок («Ватр Pads») по всей площади кристалла.

В вышеописанных проектах все блоки микросхемы выполнялись как готовые IP-решения, то есть содержали в себе полный набор компонент, от логики и проводов до собственных контактных площадок («Ватр Рады»), которые должны были соответствовать площадкам на верхнем уровне. При таком подходе нельзя было размещать контактные площадки, попадающие на границы блоков. Это приводило к неравномерному распределению питания по всему кристаллу. Кроме этого, приходилось согласовывать общую сетку в верхних слоях металлизации М8/М9 между уровнем блоков и верхнем уровне микросхемы.

Для следующих проектов рекомендуется выполнять блоки с незаконченной сеткой питания в верхних слоях и не спускать на уровень блоков контактные площадки для корпуса. Сетку в верхних слоях и подключение её к контактам («Ватр Pads») выполнять на верхнем уровне иерархии микросхемы, а блоки подключать посредством сквозных контактов, как элементы памяти в разделе 3. Такой метод обеспечит лучшее распределение питания по всей площади кристалла.

#### V. ЗАКЛЮЧЕНИЕ

В данной работе представлены только некоторые проблемы и методы их решений во время разработки систем питания высокопроизводительных микропроцессоров. Представленные методы хорошо подходят для проектов со строгими ограничениями по срокам проектирования и высокими требованиями по надежности в условиях дальнейшей эксплуатации. Исследования, проводимые в рамках ряда проектов выполненных на разных технологиях, показывают, что при переходе к новым технологиям, при уменьшении технологических размеров и увеличении сложности проектируемых вычислительных устройств, возникают новые проблемы и особенности, которые требуют специального подхода для их решения.

### Литература

- Vijay Janapa Reddi, Svilen Kanev, Wonyoung Kim. Voltage Noise in Production // Computer Architecture Conferences. Harvard University, 2011.

- [2] Chiprout E. Fast flip-chip power grid analysis via locality and grid shells // Proceedings of the 2004 IEEE/ACM International conference on Computer-aided design. November 07-11, 2004. P. 485-488.

- [3] Berridge R., Averill R.M., Barish A.E. IBM POWER6 microprocessor physical design and design methodology // IBM Journal of Research and Development. Nov., 2007. V. 51, I.:6. P. 685-714.

- [4] Chawla Vipul. Power Line Communications in Microprocessors - System Level Study and Circuit Design // Master's Thesis. Blacksburg, VA. Sep. 23, 2009.

- [5] Воробушков В.В., Рябцев Ю.С. Методы конструирования помехозащищенной системы питания для подложки современных микропроцессоров // Вопросы радиоэлектроники. Сер. ЭВТ. 2010. Вып. 3. С. 20-25.

- [6] Sachin S. Sapatnekar, Haihua Su. Analysis and Optimization of Power Grids // IEEE Design & Test. May 2003. V. 20. № 3. P. 7-15.

- [7] Мороз Я.Н. Оптимальное планирование топологии кристалла на этапе физического проектирования // Тр. 54-й научной конференции МФТИ «Проблемы фундаментальных и прикладных естественных и технических наук в современном информационном обществе». М.: МФТИ, 2011. С. 30-32.

- [8] Chetan Verma, Piyush Mishra and Pankaj Jha. Freescale Semiconductors India "Leveraging decoupling capacitance of regular power grids" URL:http://eetimes.com/design/smart-energy-design/4217717/Leveraging-decoupling-capacitance-of-regular-power-grids?pageNumber=0 (дата обращения: 07.11.2011).

- [9] Воробушков В.В. Обеспечение целостности сигналов при разработке современных вычислительных устройств : диссертация / В.В. Воробушкова. URL:http://www.ineum.ru/downloads/aref15.pdf (дата обращения: 8.06.2011).