# Автоматический синтез топологии стандартных КМОП ячеек, основанный на повторном использовании размещения транзисторов и фрагментов трассировки

В.П. Розенфельд $^1$ , Ю.Г Смирнов $^1$ , Р.Л. Мазиас $^2$ , А.В. Журавлёв $^3$

<sup>1</sup>ООО «Фрискейл Семикондактор», v.rozenfeld@freescale.com, <sup>2</sup>Freescale Semiconductor Inc, <sup>3</sup>ООО «Дойче Банк»

Аннотация — В статье рассмотрен метод автоматического синтеза топологии стандартных КМОП ячеек, основанный на полном или частичном копировании фрагментов топологии уже существующих библиотечных элементов, реализующих такие же или похожие функции. Подход позволяет существенно уменьшить количество используемых топологических решений, а также сократить время, затрачиваемое на синтез топологии библиотечных ячеек.

Ключевые слова — стандартная КМОП ячейка, топология, синтез, повторное использование, согласованное размещение, согласованная трассировка.

#### І. Введение

При проектировании СБИС широко применяется подход, основанный на использовании библиотек стандартных ячеек, реализующих основные логические функции. Как правило, такие библиотеки состоят из так называемых «семейств» ячеек, при этом элементы семейства отличаются, как правило, размерами транзисторов (нагрузочной способностью).

Создание топологии стандартных ячеек может проводиться как вручную, так и с использованием систем САПР [1]. При этом можно выделить следующие различия.

При проектировании топологии вручную для ячеек внутри одного семейства, как правило, используются подобные топологические решения, т.е. делаются согласованное размещение транзисторов, может быть скопировано положение проводников. Таким образом, ячейки в семействе получаются согласованными друг с другом по топологии, и, как следствие, по электрическим характеристикам.

При автоматическом синтезе ячейки создаются независимо, т.е. для каждой из них заново решаются задачи размещения транзисторов, проведения межсоединений и сжатия [1]. При этом критерии согласованности топологии с «соседями» по семейству не рассматриваются. Как следствие, увеличивается время синтеза (за счет перебора вариантов размещения и трассировки) и время выбора наилучшего варианта

ячейки из числа синтезированных. Кроме того, недостатки используемых алгоритмов могут привести к тому, что оптимальное решение, найденное при синтезе одной ячейки в семействе, не будет найдено в другой. Также невозможно гарантировать согласованность топологии при задаче дополнения уже существующей библиотеки новыми ячейками.

В данной статье предложен метод синтеза топологии стандартной ячейки по уже имеющемуся образцу, который реализует такую же или «родственную» логическую функцию.

В разделе II рассмотрены преобразования фрагментов электрических схем и топологии стандартных КМОП ячеек, позволяющие получать согласованные размещения транзисторов. В разделе III предлагается метод синтеза согласованной топологии ячеек. Раздел IV содержит экспериментальные данные. Выводы приведены в разделе V.

## II. СОГЛАСОВАННЫЕ ПРЕОБРАЗОВАНИЯ ЭЛЕКТРИЧЕСКИХ СХЕМ И ТОПОЛОГИИ СТАНДАРТНЫХ КМОП ЯЧЕЕК

Здесь и далее используются следующие определения:

базовая (исходная, существующая) ячейка — стандартная ячейка, для которой известна электрическая схема и топология. Топология исходной ячейки может быть создана вручную или синтезирована автоматически.

Целевая (синтезируемая, новая) ячейка — стандартная ячейка, для которой известна только электрическая схема, а топологию необходимо создать.

Синтез топологии целевой ячейки из уже существующей удобно рассматривать как некоторое преобразование исходной топологии. Оно основано на изменениях исходной электрической схемы, которые переводят её в целевую.

В следующих подразделах (A-D) рассмотрены модификации схемы базовой ячейки, позволяющие получить схему целевой ячейки. Также приведены

эскизы соответствующих изменений, позволяющих получить согласованную топологию новой ячейки.

#### А. Локальное изменение размеров транзисторов

Рис. 1. Локальное изменение размеров транзисторов

1 показан пример простейшего преобразования исходной стандартной ячейки в При таком преобразовании между целевую. электрическими схемами базовой и синтезируемой ячеек можно установить взаимно однозначное соответствие на уровне транзисторов. Один или несколько соответствующих транзисторов в целевой и базовой ячейках отличаются только размерами, причём это отличие не требует добавления новых «пальцев» (т.е. расщепления [1]). Такое преобразование описано в литературе [2] и может быть реализовано, например, сжатия базовой топологии [3] дополнительными ограничениями на размер транзисторов.

#### В. Добавление пальцев транзисторов

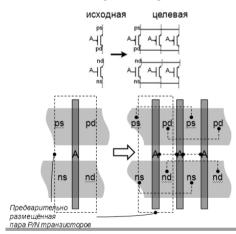

Рис. 2. Добавление «пальцев» транзисторов

На рис. 2 приведён пример преобразования, позволяющего вставлять дополнительные комплементарные P-N пары «пальцев» транзисторов в топологию стандартной ячейки. Преобразование основано на использовании предварительно размещённых P-N пар, к которым пристыковываются дополнительные расщеплённые транзисторы. При этом

возникает задача выбора стороны стыковки для оптимизации количества возникающих разрывов диффузии (ширины ячейки).

Рис. 3. Добавление series-parallel подсхем

На рис. 3 приведён пример похожего преобразования, где вместо расщеплённой КМОП-пары вставляется более сложная последовательно-параллельная (series-parallel) КМОП-подсхема.

Необходимо отметить, что указанные преобразования можно применять и в обратную сторону, т.е. для удаления избыточных P-N подсхем.

#### С. Перестановка Р- и N- частей схемы

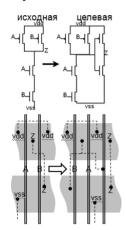

Рис. 4. Перестановка Р- и N- частей схемы

Рис.4 иллюстрирует перестановку Р- и N-частей схемы. Такое преобразование позволяет получить, например, топологию элемента ИЛИ-НЕ из имеющейся топологии элемента И-НЕ. Так же, как и преобразование на рис. 1, оно не требует добавления новых пальцев транзисторов. Это преобразование позволяет существенно расширить возможности повторного использования фрагментов топологии исходных ячеек.

#### D. Добавление инвертора ко входам/выходам ячейки

На рис. 5 проиллюстрировано добавление инвертирующего каскада к выходу схемы. Поскольку транзисторы выходного инвертора отсутствуют в

схеме исходной ячейки, в новой топологии требуется произвести выбор позиции вставки и «ориентации» транзисторов выходного каскада с целью оптимизации размера ячейки, и, возможно, локальной плотности трассировки. Так же, как и в преобразованиях из пункта B, возможно удаление избыточных каскадов.

Рис. 5. Добавление инвертора в схему

#### Е. Использование преобразований схемы

Перечисленные в подразделах *A-D* преобразования электрической схемы и соответствующие им изменения топологии позволяют построить алгоритм синтеза топологии целевой ячейки, согласованной с уже имеющейся топологией базовой ячейки. При этом гарантируется согласованное размещение транзисторов.

Например, имея схему и топологию одного элемента U-HE в качестве базового, можно получить схему и согласованную топологию для всего семейства U-HE (преобразования A, B), а также для следующих семейств элементов: UЛU-HE (преобразование C), U(D), UЛU(C, затем D), а также семейств с инверсией входов.

#### III. МЕТОД СИНТЕЗА СОГЛАСОВАННОЙ ТОПОЛОГИИ ЯЧЕЕК

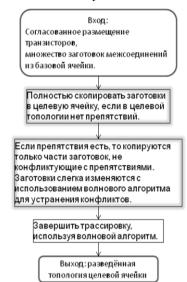

Блок-схема метода приведена на рис.6.

### А. Построение зависимостей между схемами исходных и иелевых ячеек

Для синтеза согласованной топологии необходимо провести анализ исходных и целевых электрических схем на предмет выявления их совпадающих частей. Такой анализ проводится в терминах преобразований, описанных выше, т.е. наличие зависимости между исходной и целевой ячейками означает, что из топологии исходной ячейки можно получить как минимум согласованное размещение транзисторов, используя комбинацию преобразований *A-D* из раздела II.

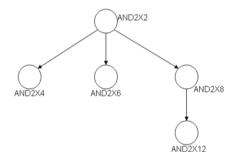

В результате выполнения этого этапа создаётся граф зависимостей между схемами. При этом важно

отметить, что одна и та же схема может быть использована как в качестве целевой, так и в качестве базовой, а граф зависимостей определяет порядок синтеза ячеек (см. пример на рис. 7).

Рис. 6. Метод синтеза согласованной топологии ячеек

Также факт наличия зависимости между ячейками означает, что установлено соответствие между транзисторами базовой и целевой ячеек, что необходимо для получения согласованного размещения.

Рис. 7. Пример графа зависимостей между схемами ячеек

#### В. Получение согласованного размещения транзисторов в целевой ячейке

На этом этапе применяются преобразования A-D, описанные в разделе II. При этом преобразования В и *D* могут быть выполнены разными способами. Например, добавление пальцев транзистора (рис.2), может быть выполнено как в левую, так и в правую сторону, что порождает разные варианты согласованного размещения транзисторов. Поэтому, для получения наилучшего решения, используется алгоритм полного перебора. Варианты оцениваются с векторного критерия помошью качества. компонентами которого являются оценка ширины ячейки, оценка локальной плотности межсоединиений и другие.

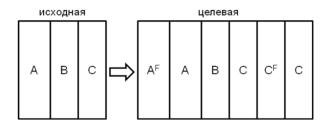

Рис. 8. План топологии исходной и целевой ячеек

В результате выполнения этого шага алгоритма получается так называемый план ячейки, показанный на рис.8. Он представляет собой упорядоченный список фрагментов топологии, каждый из которых содержит информацию о своём «происхождении» (скопирован из базовой ячейки, получен путём репликации, и т.д.), ориентации (отражение по X и/или по Y). В качестве фрагментов могут использоваться, например, комплементарные пары P-N-транзисторов, series-parallel подсхемы, и более сложные фрагменты.

Этот план используется при построении согласованной трассировки.

#### С. Построение согласованной трассировки

Цель этого этапа - получение межсоединений в целевой ячейке, построенных на основании трассировки исходной топологии.

Вначале происходит формирование множества заготовок межсоединений. При этом межсоединения фрагмента базовой ячейки копируются во множество заготовок, если «окружение» фрагмента в исходной и целевой топологии совпадает. Так, в примере из рисунка 8 в набор заготовок войдут межсоединения только из фрагмента В. Проводники из фрагмента А не будут использованы, поскольку в исходной топологии он стоит на левом краю, а в целевой — слева от фрагмента А присутствует его отраженная копия  $\mathbf{A}^{\mathbf{F}}$ , поэтому окружение  $\mathbf{A}$  в базовой и в новой топологии не совпадают. По той же причине не будут использованы проводники из фрагмента  $\mathbf{C}$ .

Множество заготовок межсоединений используется в соответствии с алгоритмом на рис. 9. Заготовки могут использоваться в топологии целевой ячейки несколько раз, по количеству копий соответствующего фрагмента.

#### IV. Экспериментальные данные

Предложенная методология была опробована при создании библиотек стандартных ячеек в компании Freescale Semiconductor. Было проведено сравнение результатов прямого синтеза и согласованного синтеза по критериям времени работы системы, ширины ячеек и согласованности топологии ячеек в семействе. Основные результаты следующие:

отмечено существенное (до 10 раз) сокращение времени синтеза ячеек. Это связано с уменьшением количества вариантов размещения и трассировки.

Ширина ячеек осталась практически без изменений (на наборе из 130 ячеек 7 ячеек получились лучше с использованием согласованного синтеза, 3 — с использованием прямого).

Было получено согласованное размещение транзисторов и положение проводников.

Рис. 9. Построение согласованной трассировки ячеек с использованием заготовок

#### V. Выводы

Предложен метод согласованного синтеза топологии стандартных КМОП ячеек, позволяющий существенно сократить набор используемых конструкций, топологических a также время, затрачиваемое на синтез. Метод можно использовать как для создания целых библиотек ячеек «с чистого листа», так и для добавления новых ячеек к уже существующим библиотекам. Проведённые эксперименты показали его высокую эффективность.

#### Литература

- [1] Зинченко Л.А., Мазиас Р.Л., Розенфельд В.П., Смирнов Ю.Г., Сотников М.А., Стоянов С.В., Топузов И.Г., Фалковски К.Д. СЕLLERITY: Система автоматического синтеза топологии стандартных ячеек // Проблемы разработки перспективных микроэлектронных систем 2005. Сборник научных трудов. М.: ИППМ РАН, 2005. С. 113-120.

- [2] Basaran B., Ganesh K., Lau R., Levin A., McCoo M., Rangarajan S., Sehgal N. GeneSys: a leaf-cell layout synthesis system for Ghz VLSI designs // Proc. XII International conference on VLSI Design. 1999. P. 448-452.

- [3] Розенфельд В.П., Сотников М.А., Топузов И.Г., Улуханов Э.А., Широ Е.Г. Система сжатия и миграции топологии стандартных ячеек // Проблемы разработки перспективных микроэлектронных систем – 2005. Сборник научных трудов. М.: ИППМ РАН, 2005. С. 121-127.