# Исследование стойкости к воздействию отдельных ядерных частиц ячеек КНИ КМОП ОЗУ методами смешанного 3D TCAD-SPICE моделирования

К.О. Петросянц $^1$ , И. А. Харитонов $^1$ , Е.В. Орехов $^2$ , Л.М. Самбурский $^2$ , А.П. Ятманов $^3$ , А.В. Воеводин $^3$

<sup>1</sup> Московский государственный институт электроники и математики (технический университет), <u>eande@miem.edu.ru</u>,

<sup>2</sup> Институт проблем проектирования в микроэлектронике РАН,

<sup>3</sup> ФГУП ФНПЦ «НИИИС»

Аннотация — В статье приведены результаты смешанного 3D приборно-схемотехнического моделирования воздействия ОЯЧ на различные области КНИ МОП транзисторов в составе ячейки памяти при масштабировании транзисторов от 0,5 до 0,1 мкм. Показано, что на устойчивость ячейки памяти к воздействию ОЯЧ существенно влияет не только величина критического заряда, но также и место попадания частицы и форма возникающего при этом импульса тока.

Ключевые слова — ячейки ОЗУ, КНИ КМОП, ОЯЧ, TCAD-SPICE моделирование, масштабирование

### I. Введение

Оценка стойкости КМОП схем к воздействию одиночных ядерных частиц (ОЯЧ) важна для их использования в аэрокосмической аппаратуре, экспериментальных установках ядерной физики и др.

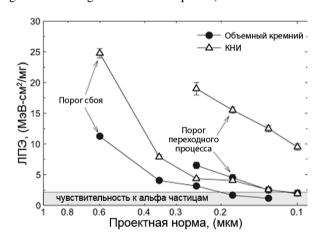

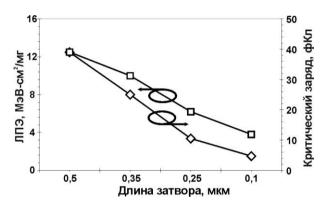

Известно, что наиболее чувствительными к воздействию ОЯЧ являются схемы памяти. С уменьшением топологических проектных норм стойкость ячеек памяти к воздействию ОЯЧ уменьшается (см. рис. 1) [1]. При этом устойчивость ячейки зависит в значительной степени от динамических характеристик всплеска тока, обусловленного прохождением частицы через структуру прибора. В работе [2] показано, что в глубоко субмикронных (L=65 нм) КМОП схемах памяти длительность всплеска тока вследствие прохождения частицы и момент удара частицы по отношению к времени записи-считывания в ячейке существенно влияют на устойчивость этих схем к сбоям.

Следует отметить, что экспериментальное исследование процессов воздействия отдельных частиц на полупроводниковые приборы и микросхемы весьма затруднительно.

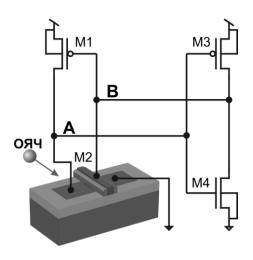

Для исследования воздействия ОЯЧ на КМОП ячейки памяти широко используется метод смешанного приборно-схемотехнического моделирования в TCAD (Technology Computer Aided Design) [3] (рис. 2). Транзистор, в который попадает частица, моделируется в TCAD (в 2-х или 3-х мерном приближении), а остальная часть схемы рассчитывается в программе схемотехнического моделирования SPICE (Simulation Program with Integrated Circuit Emphasis).

Рис. 1. Линейные потери энергии (ЛПЭ) частицы в структуре МОП транзистора, вызывающие сбой в ячейке памяти, для различных проектных норм [1]

При использовании данного подхода величины всплеска тока и просадки напряжения на стоке (узел В на рис. 2) вычисляются при совместном расчете физических процессов в структуре транзистора и переходных процессов в схеме.

Рис. 2. Метод смешанного приборно-схемотехнического моделирования воздействия тяжелых частиц на ячейки памяти

Смешанное TCAD-SPICE моделирование позволяет оценить влияние конструктивно-технологических факторов структуры транзистора и, кроме того, дает возможность определить параметры схемотехнической модели воздействия ОЯЧ.

Оценки стойкости ячеек памяти к воздействию ОЯЧ в большинстве работ проводятся по величине критического заряда  $Q_{\text{крит}}$ . Это заряд в чувствительном узле (В на рис. 2), который вызывает переключение ячейки в другое логическое состояние. Однако, работы ряда авторов [4] показали, что для оценки стойкости ячеек необходимо учитывать не только величину критического заряда, но и форму возникающих всплесков тока. К сожалению, этот эффект детально не исследован ни для «объемной» технологии, ни для технологии «кремний на изоляторе» (КНИ). Кроме того, в этих же работах отмечалось, что существенное значение для устойчивости ячеек памяти к воздействию ОЯЧ имеют геометрия затвора транзистора и координаты области попадания частицы в структуру прибора.

Рядом авторов отмечалось [5], что в субмикронных транзисторах при попадании частицы в область около истока возникает канал утечки между истоком и стоком, существенно увеличивающий величину собранного заряда и влияющий на стойкость ячейки памяти. В указанной работе анализировались только транзисторы, выполненные по «объемной» технологии и не приведены данные по проявлению этого эффекта при масштабировании транзисторов.

В данной работе ставится задача исследования устойчивости ячеек памяти статических ОЗУ, изготовленных по КМОП КНИ-технологии с различными проектными топологическими нормами от 0,5 до 0,1 мкм. При этом впервые детально рассмотрен эффект влияния места попадания частицы в структуру МОП транзистора на величину и форму всплеска тока, обусловленного воздействием ОЯЧ.

# II. ПАРАМЕТРЫ КНИ МОП-ТРАНЗИСТОРОВ МОДЕЛИРУЕМОЙ ЯЧЕЙКИ ПАМЯТИ

Воздействие ОЯЧ на МОП транзистор М2 моделировалось в 3-х мерном приближении в ТСАD. Остальные транзисторы ячейки памяти статического ОЗУ на рис. 2 моделировались в программе SPICE. Рассчитывались три варианта ячейки: на транзисторах с длинами канала 0,5 и 0,35 мкм с частичным обеднением и длиной канала 0,1 мкм с полным обеднением.

Структуры транзисторов в TCAD и параметры их SPICE моделей масштабировались в соответствии с известными правилами (см. табл.1).

Таблица 1 Параметры моделируемых КНИ МОП-транзисторов

| Длина затвора, мкм     | 0.5  | 0.35 | 0.25 | 0.1 |

|------------------------|------|------|------|-----|

| Толщина подзатворного  | 11,5 | 6,8  | 4    | 3   |

| диэлектрика, нм        |      |      |      |     |

| Толщина активного слоя | 200  | 190  | 150  | 40  |

| кремния, нм            |      |      |      |     |

| Толщина скрытого ди-   | 150  | 190  | 150  | 100 |

| электрика, нм          |      |      |      |     |

| Ширина канала          | 1,4  | 1    | 0,7  | 0,4 |

| n-МОПТ, мкм            |      |      |      |     |

| Ширина канала          | 2,8  | 2    | 1,4  | 0,8 |

| р-МОПТ, мкм            |      |      |      |     |

| Напряжение питания, В  | 3,3  | 2,5  | 1,8  | 1,2 |

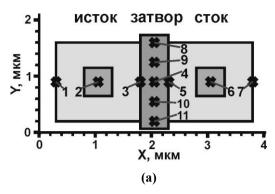

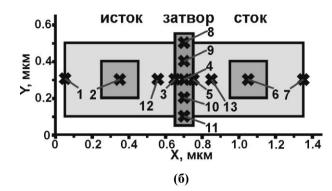

Транзисторы М1, М3 и М4 моделировались в SPICE с использованием модели BSIMSOI версии 3. Учитывая, что величина собранного из трека частицы заряда существенно зависит от области транзистора, в которую попадает частица, расчеты проводились для различных областей транзисторной структуры, помеченных на рис. 3(а, б) крестиками.

Трек частицы моделировался с пространственным гауссовым распределением с постоянным характеристическим радиусом 20 нм (расстояние от центра трека, на котором происходит спад концентрации в е раз) и с гауссовым временным распределением с характеристическим временем 2 пс, что согласуется с данными работ [6-7]. Моделировалось попадание частицы в структуру транзистора под прямым углом.

## III. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ

### А. Расчет реакции ячейки памяти на попадание ОЯЧ в точки вдоль затвора МОП-транзистора

Для моделирования было выбрано 5 точек, расположенных на одной линии вдоль затвора по оси Y (рис. 3). Расчеты проводились для иона Fe с энергией 16 МэВ и линейными потерями энергии (ЛПЭ) 21 МэВ-см<sup>2</sup>/мг, т.к. при этом значении ЛПЭ осажденный частицей заряд близок к критическому для ячейки памяти с проектными нормами 0,5 мкм [8].

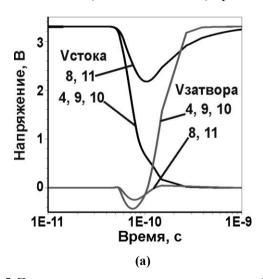

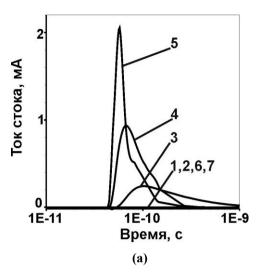

Из приведенных на рис. 4 и 5 результатов моделирования видно, что при попадании ОЯЧ в крайние

Рис. 3. Топология N-МОПТ с длиной канала 0,5 мкм (а) и 0,1 мкм (б) с пронумерованными местами попадания ОЯЧ с  $_{

m JII}$ Э=21 МэВ-см $_{

m ^2/m}$ Г

Рис. 4. Всплески тока стока N-МОПТ с длиной канала 0,5 мкм (а) и 0,1 мкм (б) при попадании ОЯЧ (ЛПЭ=21 МэВ-см²/мг) в различные точки вдоль затвора транзистора (рис. 3)

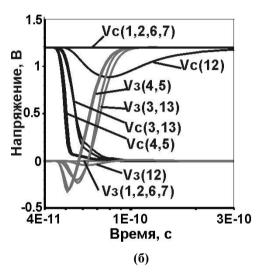

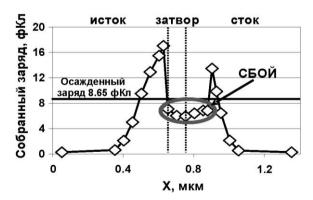

Рис. 5. Переходные процессы напряжения на стоке (узел A рис. 2) и на затворе (узел B рис. 2) в N-МОПТ с длиной канала 0.5 мкм (а) и 0.1 мкм (б) при попадании ОЯЧ (ЛПЭ=21 МэВ-см²/мг) в различные точки вдоль затвора транзистора (рис. 3)

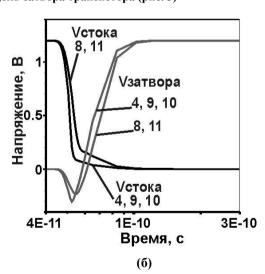

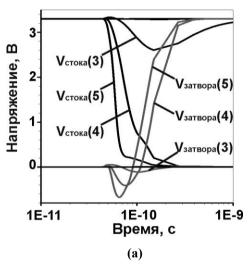

Рис. 6. Смоделированные импульсы тока стока N-MOПТ с длиной канала 0,5 мкм (а) и 0,1 мкм (б) при попадании ОЯЧ (ЛПЭ=21 МэВ-см²/мг) в различные точки структуры транзистора вдоль оси X (рис. 3)

Рис. 7. Смоделированные переходные процессы напряжения на стоке (узел A рис. 2) и на затворе (узел В рис. 2) в N-MOПТ с длиной канала 0,5 мкм (а) и 0,1 мкм (б) при попадании ОЯЧ (ЛПЭ=21 МэВ-см2/мг) в различные точки структуры транзистора вдоль оси X (рис. 3)

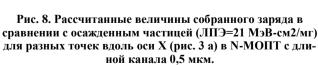

Рис. 9. Рассчитанные величины собранного заряда в сравнении с осажденным частицей (ЛПЭ=21 МэВ-см2/мг) для разных точек вдоль оси X (рис. 3 б) в N-МОПТ с длиной канала 0,1 мкм.

точки затвора (8 и 11, рис. 3) ячейка нечувствительна к воздействию ОЯЧ с ЛПЭ 21 МэВ-см²/мг при длине канала МОП транзистора 0,5 мкм, и становится чувствительной к этой же частице при длине канала 0,1 мкм. Это объясняется более близким расположением точек 8 и 11 к стоковому переходу в транзисторе с длиной канала 0,1 мкм и более эффективным собиранием заряда из трека из-за резкого всплеска тока стока.

В. Расчет реакции ячейки памяти при попадании ОЯЧ в точки структуры МОПТ, расположенные вдоль оси X на рис. 3

Результаты моделирования переходных процессов при попадании частицы в разные области МОПТ показали, что наиболее чувствительными точками транзистора являются точки вблизи стокового перехода (точки 4, 5 для 0,5 мкм МОПТ и точки 4, 5, 13 для 0,1 мкм МОПТ). При попадании в эти точки ОЯЧ с ЛПЭ=21 МэВ-см²/мг возникает биполярный эффект (открытие перехода исток-подложка), в результате которого увеличивается собранный заряд.

Возникающий при этом всплеск тока стока обладает малой длительностью с резким спадом и большой амплитудой (рис. 6), что приводит к перебросу ячейки. Наиболее чувствительная точка расположена в переходе сток-рабочая область под краем затвора (точка 5 на рис. 3).

Области истока и стока (точки 1, 2, 6, 7 рис. 3) являются наименее чувствительными к воздействию ОЯЧ, поскольку при этом не возникает паразитного биполярного транзистора. Эффективность собирания заряда трека мала и величины всплесков тока стока малы.

При попадании ОЯЧ в приграничную с затвором область истока (точка 3) транзистора с длиной канала 0,5 мкм возникает импульс тока с большой длительностью и малой амплитудой (рис. 6, а). Несмотря на большую величину собранного заряда (за счет большой длительности), сбоя не происходит (см. рис. 7, а) вследствие малой амплитуды всплеска тока стока. При попадании в аналогичную точку 0,1 мкм транзистора длительность импульса тока существенно короче, амплитуда импульса достаточно велика (см. рис. 6, б), что приводит к сбою (рис. 7, б).

С. Сравнение стойкости ячеек памяти к воздействию ОЯЧ при масштабировании длины канала транзистора от 0,5 до 0,1 мкм

Сравнение переходных процессов рис. 4-7 показывает, что в ячейке на транзисторах с длиной канала 0.1 мкм длительности переходных процессов, вызванных попаданием иона, примерно в 6 раз короче по сравнению с вариантом 0,5 мкм. Края области затвора (точки 8 и 11) и граница истока и активной области (точка 3), устойчивые к удару иона для технологии 0,5 мкм становятся чувствительными для технологии 0,1 мкм (рис. 6, 7).

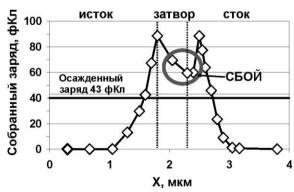

На рисунках 8 и 9 приведены рассчитанные в TCAD зависимости собранного заряда (интеграл от тока стока по времени за длительность импульса) от продольной координаты X для МОПТ с длиной канала 0,5 мкм и 0,1 мкм, соответственно. Из рисунков видно, что чем ближе место попадания частицы к обратносмещенному p-n-переходу сток-рабочая область, тем более вероятно переключение ячейки ОЗУ, т. е. случайный сбой.

Для ячеек с длинами каналов 0,5 и 0,1 мкм к сбою приводило попадание ОЯЧ в область стокового перехода и в середину области затвора. При этом в ячейке с длиной канала 0,5 мкм собранный заряд оказался больше осажденного из-за усиления биполярного транзистора. В ячейке на полностью обедненных МОПТ с длиной канала 0,1 мкм собранный заряд оказался меньше осажденного и паразитный биполярный транзистор не включался. Быстрое собирание заряда из трека в этом случае можно объяснить преобладанием дрейфового механизма собирания заряда из трека над диффузионным вследствие близости трека к обратно смещенному переходу.

С увеличением расстояния от трека до обратно смещенного р-п-перехода «сток-активная область» скорость собирания снижается из-за того, что преобладает диффузионный механизм переноса заряда. Форма импульса тока стока становится более пологой и меньшей по величине. Скачок напряжения на затворах транзисторов МЗ и М4 не превышает их пороговых напряжений, транзисторы не открываются и переключения ячейки не происходит, хотя собранный заряд в некоторых областях транзисторов превышает осажденный более чем в 2 раза.

D. Оценка критического для ячейки заряда и пороговых ЛПЭ при уменьшении проектных норм до

Традиционно считается, что критический заряд  $Q_{\text{крит}}$  – это минимальный собранный выводом стока заряд, необходимый для переключения ячейки ОЗУ [1-3].

В ряде работ [4, 10] показано, что величина собранного заряда не всегда является однозначным критерием стойкости ячейки, необходимо учитывать форму возникающего импульса тока стока, т. е. превышение напряжением на затворе транзистора другого плеча ячейки (М3 на рис. 2) величины его порогового напряжения.

Наши расчеты показали, что при попадании ОЯЧ в точку 3 (рис. 3) для транзисторов с длинами каналов 0.5 мкм импульс тока растянут во времени (рис. 7) и мал по амплитуде. В результате спад напряжения на стоке М2 недостаточен для нарастания напряжения на затворе М3 выше порогового, М3 не открывается и сбоя не происходит, хотя полный собранный стоком заряд имеет самое большое значение (см. рис. 8).

С учетом сказанного, критический заряд определялся как заряд, собранный на выводе стока M2 в интервале времени от 0 до t1, когда на затворе транзистора M4 напряжение больше порогового:

$$Q_{KPHT} = \int_{0}^{t_1} Ic(t)dt.$$

(1)

$Q_{\mbox{\tiny крит}}$  оказывается меньше полного собранного стоком заряда.

На рис. 10 приведены рассчитанные пороговые значения линейных потерь энергии (ЛПЭ) и критические заряды для МОПТ с длинами затвора 0,5; 0,35; 0,25 и 0,1 мкм. Пороговые ЛПЭ определялись следующим образом: последовательно уменьшалось значение ЛПЭ в ТСАD модели воздействия ОЯЧ на указанные выше области структуры и бралось минимальное значение ЛПЭ, при котором происходило переключение ячейки. Видно существенное уменьшение критических значений ЛПЭ (в 3 раза) и заряда (в 8 раз), вызывающих переброс ячейки при уменьшении размеров транзисторов, что хорошо согласуется с данными [9-10].

Рис. 10. Смоделированные пороговые значения линейных потерь энергии ионов (квадраты) и критический заряд ячейки статического ОЗУ (ромбы) для различных длин затвора

#### IV. Выводы

Результаты смешанного 3D приборносхемотехнического моделирования воздействия ОЯЧ на структуру КНИ МОП транзисторов в составе ячейки памяти при масштабировании транзисторов от 0,5 до 0,1 мкм показали, что:

- наименее чувствительными к сбою точками КНИ МОПТ являются области истока и стока, удаленные от истокового и стокового переходов, соответственно;

- наиболее чувствительными точками транзистора являются точки затвора и стока, прилегающие к стоковому переходу;

- амплитуда и форма всплеска тока стока при ударе частицы играет решающую роль в оценке стойкости

ячейки: резкие скачки наиболее опасны с точки зрения сбоя;

- при масштабировании КНИ МОПТ от 0,5 до 0,1 мкм критический заряд уменьшается в 8 раз, длительность всплеска тока уменьшается в 6 раз, что подтверждает существенное снижение стойкости к ОЯЧ при уменьшении длины канала.

Работа выполнена во исполнение Федеральной целевой программы «Научные и научно-педагогические кадры инновационной России» на 2009-2013 г.г. (Направление «Микроэлектроника», мероприятие 1.2.2., НК-728П).

#### Литература

- [1] Digital single event transient trends with technology node scaling / J.M. Benedetto, P.H. Eaton, D.G. Mavis, M. Gadlage, T. Turflinger // IEEE Transactions on Nuclear Science. December 2006. Vol. 53. № 6. P. 3462–3465.

- [2] Катунин Ю.В., Стенин В.Я. Моделирование 65 нм КМОП триггерных ячеек с повышенной сбоеустойчивостью к воздействию отдельных ядерных частиц // Сб. научных тр. 13-ой Российской научно-технической конференции «Электроника, микро- и наноэлектроника 2011». 27 июня—1 июля 2011. М:. МИФИ, 2011. С. 24-33.

- [3] Turowski M., Raman A., and Jablonski G. Mixed-mode simulation and analysis of digital single event transients in fast CMOS ICs // Proc. 14th Int. Conf. MIXDES, 2007. Jun. 2007. P. 433-439.

- [4] Dasgupta S. Trends in Single Event Pulse Widths and Pulse Shapes in Deep Submicron CMOS // M. S. thesis, Dept. Elect. Eng. and Comp. Science. Vanderbilt University. Dec. 2007.

- [5] Velacheri S., Massengill L.W., Kerns Sh.E. Single Event Induced Charge Collection and Direct Channel Conduction in Submicron MOSFETS // IEEE Transactions on Nuclear Science. 1994. Vol. 41. № 6. P. 2103-2111.

- [6] Investigation of 30 nm Gate-All-Around MOSFET Sensitivity to Heavy Ions: A 3-D Simulation Study / K. Castellani-Coulié, D. Munteanu, J.L. Autran, V. Ferlet-Cavrois, P. Paillet, J. Baggio // IEEE Transactions on Nuclear Science. Aug. 2006. Vol. 53. № 4. P. 950-1958.

- [7] Device-Physics-Based Analytical Model for Single-Event Transients in SOI CMOS Logic / D. Kobayashi, K. Hirose, V. Ferlet-Cavrois, D. McMorrow, T. Makino, H. Ikeda, Y. Arai, M. Ohno // IEEE Transactions on Nuclear Science. Dec. 2009. Vol. 56. № 6. P. 3043-3049.

- [8] Петросянц К.О., Харитонов И.А., Орехов Е.В. Моделирование воздействия одиночных заряженных частиц на субмикронные КНИ КМОП ячейки ПЗУ // Сб. научных тр. 9-ой Российской научно-технической конференции «Электроника, микро- и наноэлектроника 2007». 24-28 июня 2007. М.: МИФИ, 2007. С. 38-41.

- [9] Srinivasan G.R. Modeling the cosmic-ray-induced softerror rate in integrated circuits: An overview // IBM Journal of Research and Development. Jan. 1996. Vol. 40. Issue 1. P. 77-89.

- [10] SEU Critical Charge and Sensitive Area in a Submicron CMOS Technology / C. Detcheverry, C. Dachs, E. Lorfevre, C. Sudre, G. Bruguier, J.M. Palau, J. Gasiot, R. Ecoffet // IEEE Transactions on Nuclear Science. Dec. 1997. Vol. 44. № 6. P. 2266-2273.