# Мобильное сопряжение средств диагностирования и цифровых систем, конфигурируемых на кристалле

В.Г. Рябцев, А.А. Шубович, А.С. Феклистов

Волгоградский государственный аграрный университет,

akim.onoke@mail.ru

Аннотация — Рассматривается проблема мобильного сопряжения автоматизированных средств тестового диагностирования и цифровых систем, конфигурируемых на кристалле. Предложена структура мультипроцессорного векторного преобразователя, обладающего высоким быстродействием и обеспечивающего выполнение операций произвольного сдвига разрядов тестовых воздействий или ответных реакций за один период сигнала синхронизации.

*Ключевые слова* — мобильное сопряжение, тестовое диагностирование, цифровая система, конфигурируемая на кристалле.

## I. Введение

Создание систем-на-кристалле (System-on-a-Chip, SoC), в состав которых входят микропроцессоры, память, контроллеры памяти и другие компоненты, является важным направлением развития цифровой электроники. Данные системы позволяют решать задачи сложной цифровой обработки данных и коммуникаций, промышленной автоматизации и мультимедийных технологий. При этом возрастает сложность тестового диагностирования, которое состоит в подаче на входы SoC тестовых наборов, снятия выходных откликов и сравнения их с эталонными значениями [4-7].

Набор аппаратных средств, применяемых для тестового диагностирования SoC, очень широк: от специализированных технологических тестеров и измерительных приборов до встроенных в аппаратуру средств периферийного сканирования (Boundary-scan) и встроенного самотестирования (Built-in Self-test, BIST) [2, 5].

Для выполнения периферийного сканирования транспортный механизм применяется интерфейса, который обеспечивает последовательное перемещение тестовых воздействий диагностирующего устройства через последовательно соединенных ячеек сканирования (Boundary Scan Cells, BSC) на входы SoC, которые в это время отключены от внешних контактов. Реакция SoC, поступающая от внутренних контрольных точек и выходных элементов, фиксируется в ячейках BSC и последовательным кодом передается диагностирующего устройства [8].

При выборе средств тестирования необходимо учитывать, что число BSC-ячеек превышает число внешних контактов SoC (500 и более) и может достигать несколько тысяч. Если использовать концепцию построения диагностирующего устройства, обеспечивающую соответствие длины регистра приема/передачи и количества BSC-ячеек, то это приведет к увеличению стоимости, энергопотребления и габаритов данного устройства.

Кроме того, средства периферийного сканирования (Boundary-scan) и технологии JTAG-тестирования позволяют проверить соединения компонентами SoC. Однако. динамические возможности регистра периферийного сканирования не позволяют протестировать компоненты на высоких рабочих частотах. А для запоминающих устройств, встроенных в SoC, нельзя применить периферийное сканирование, так как при этом тестирование будет статическим и продолжительным, а диагностические способности его будут низкими [11, 13].

Для реализации встроенного самотестирования применяют генераторы псевдослучайных тестовых наборов и сигнатурные анализаторы, выполненные на базе регистров сдвига с линейной обратной связью (LFSR — Linear feedback shift register) [10, 12]. Но псевдослучайные последовательности тестов не обеспечивают достижения высокого уровня выявления возможных отказов компонентов SoC.

выполнения самотестирования SoC встраивают генератор тестовых векторов, регистратор и анализатор реакций выходов на поданные тестовые последовательности. Стандартный механизм BIST предназначен для генерации тест-векторов на основе заранее заданного алгоритма тестирования и для повышения диагностических возможностей изделие необходимо проектировать заново [9, 13]. Размещение же дополнительных компонентов внутри SoC снижает площадь кристалла для размещения основных компонентов и приводит к появлению новых типов дефектов, механизм возникновения которых плохо предсказуем и, соответственно, тестирование таких дефектов усложнено.

Большую достоверность тестового диагностирования SoC обеспечивают формирователи детерминированных тестов, алгоритмические

генераторы и другие средства, при этом формируемые ими тестовые воздействия упорядочены в виде векторов, в которых отдельные разряды расположены в строго определенной последовательности и в таком же виде они должны быть поданы на краевые контакты объекта диагностирования (ОД). Однако конструктивных особенностей кристаллов SoC расположение контактов физическое упорядочено, и они располагаются в произвольном Считанные реакции с порядке. произвольно расположенных краевых контактов SoC, которые соответствуют входным и/или выходным шинам ОД, необходимо также преобразовать в упорядоченную последовательность для обеспечения сравнения их с заранее подготовленными эталонными значениями.

Для сопряжения диагностируемых объектов и автоматизированных средств тестового диагностирования обычно применяются дополнительные коммутирующие средства, что сокращает частоту диагностирования. Кроме того увеличивается номенклатура таких средств при большом количестве типов диагностируемых изделий.

Для более доступного изложения дальнейшего материала введем основные определения.

Определение 1. Логическое сечение — это такое представление модели объекта диагностирования, когда его выводы упорядочены по каким-либо признакам (например, по функциональному назначению), объединены в группы и пронумерованы от 1 до  $N_i$ , где  $N_i$  — число выводов в j-ой группе.

**Определение 2.** Физическое сечение – представление модели ОД на уровне физических контактов его внешних разъемов.

Определение 3. Таблица соответствия – данные специального запоминающего устройства, которые каждому элементу логического сечения ставят в соответствие контакты физического сечения.

**Определение 4.** Идентификация логического и физического сечений моделей ОД — нахождение соответствия между данными сечениями.

Для хранения таблицы соответствия сечений ОД можно использовать область главной памяти компьютера, в которой для каждого контакта выделяется ячейка памяти. Полный вектор воздействия сначала формируется в памяти компьютера, а затем несколькими операциями передачи данных загружается в память тестера.

Программный метод идентификации координат векторов воздействий и физических контактов краевых контактов SoC требует значительных затрат времени и при этом, в основном, теряется производительность диагностирования.

Известен метод решения задачи идентификации логических и физических сечений SoC при помощи таблицы соответствия, занесенной во вспомогательное запоминающее устройство [1]. При этом операции

распаковки векторов воздействий осуществляются побитно и их продолжительность пропорциональна длине вектора, что снижает производительность диагностической системы, т.к. из-за большого объема тестов происходит многократная загрузка сегментов тестов в память тестера для выдачи их на SoC на реальной рабочей частоте.

**Цель данной работы** – разработка метода и структуры быстродействующего мультипроцессорного векторного преобразователя, обеспечивающего мобильное сопряжение автоматизированных средств тестового диагностирования и цифровых систем, конфигурируемых на кристалле.

# II. МАТЕМАТИЧЕСКИЕ ОПЕРАЦИИ ПРЕОБРАЗОВАНИЯ КООРДИНАТ ВЕКТОРОВ

Для исследования процессов, возникающих при выполнении операций идентификации координат векторов воздействий и выводов ОД, необходимо создать математическую модель, которая будет воспроизводить подходящим образом выбранные стороны физической ситуации. Необходимо также установить правила, связывающие специфические физические объекты и отношения с определенными математическими объектами И отношениями. Математическая модель с её объектами произвольной природы, отношениями и операциями определяется непротиворечивым набором правил (теорем), вводящих операции, которыми можно пользоваться для достижения результатов.

Рассмотрим линейное векторное пространство  $L_n$  с системой координат, определяемой базисными векторами  $\vec{\mathbf{e}}_1,\ \vec{\mathbf{e}}_2,...,\ \vec{\mathbf{e}}_n$ . Тогда любой вектор  $\vec{a}\in L_n$  может быть представлен в виде [3]

$$a=a_1\vec{e}_1+a_2\vec{e}_2+...+a_n\vec{e}_n=\sum_{i=1}^n a_i\vec{e}_i, \eqno(1)$$

где  $a_1,a_2,...,a_n$  — координаты вектора  $\vec{a}$  в базисе  $\vec{e}_1,\ \vec{e}_2,...,\vec{e}_n$  .

Линейные однородные преобразования позволяют сформировать вектор  $\vec{u} \in L_n$ , координаты которого могут быть определены следующим образом [3]:

$$\begin{pmatrix} u_1 \\ u_2 \\ \dots \\ u_n \end{pmatrix} = \begin{pmatrix} e_{11} & e_{12} & \dots & e_{1n} \\ e_{21} & e_{22} & \dots & e_{2n} \\ \dots & \dots & \dots & \dots \\ e_{n1} & e_{n2} & \dots & e_{nn} \end{pmatrix} \begin{pmatrix} a_1 \\ a_2 \\ \dots \\ a_n \end{pmatrix}, \text{ или } U = eA \,. \tag{2}$$

Рассмотрим и докажем следующее утверждение.

**Теорема 1.** Пусть двоичный вектор  $\vec{a}$  с базисными координатами, определяемыми вектор-столбцом D, представлен в n-мерном векторном пространстве  $L_n$  упорядоченными по возрастанию координатами  $A=(a_0,a_1,...,a_{n-1})^T$ ,  $a_i=2^i$ , где  $i=\overline{0,n-1}$ . Тогда его можно преобразовать в n-мерный вектор тестовых

воздействий с базисными координатами, определяемыми вектор-столбцом  $D^*$  и координатами  $A^*$ , распределенными в произвольном порядке, следующим образом:

$$D^* = MD^*; A^* = MA^*, (3)$$

где M — мономиальная матрица n-го порядка.

Доказательство. От противного. Предположим, что в указанной матрице M имеется больше одного элемента, отличного от нуля хотя бы в одной из ее строк. Однако координаты двоичного вектора определяются выражением  $a_i=2^i$ , где  $i=\overline{0,n-1}$ . Все данные числа имеют только одну единицу в двоичной системе счисления, а для вычисления всех новых координат применяется аналогичная формула  $a_i^*=2^i$ . Получено противоречие. Таким образом, для однозначного соответствия координат векторов и физических контактов ОД требуется использовать мономиальную матрицу n-го порядка.

**Пример расчета 1.** Вектор воздействий, заданный в векторном пространстве  $L_8$ , преобразуется по схеме, изображенной на рис. 1.

| 8                 | 7  | 6  | 5  | 4 | 3 | 2   | 1  | Номера        |

|-------------------|----|----|----|---|---|-----|----|---------------|

|                   |    |    |    |   |   |     |    | координат     |

| 1                 | 0  | 1  | 1  | 0 | 0 | 0   | 1  | Исходные      |

|                   |    |    |    |   |   |     |    | значения      |

|                   |    |    |    |   |   |     |    | вектора       |

| 128               | 64 | 32 | 16 | 8 | 4 | 2   | 1  | Исходные      |

|                   |    |    |    |   |   |     |    | координаты    |

|                   |    |    |    |   |   |     |    | $a_{\dot{i}}$ |

| ↓ по формулам (3) |    |    |    |   |   |     |    |               |

| 8                 | 7  | 6  | 5  | 4 | 3 | 2   | 1  | Номера        |

|                   |    |    |    |   |   |     |    | выводов       |

|                   |    |    |    |   |   |     |    | ОД            |

| 1                 | 0  | 0  | 1  | 0 | 0 | 1   | 1  | Новые         |

|                   |    |    |    |   |   |     |    | значения      |

|                   |    |    |    |   |   |     |    | вектора       |

| 32                | 64 | 4  | 1  | 8 | 2 | 128 | 16 | Новые         |

|                   |    |    |    |   |   |     |    | координаты    |

|                   |    |    |    |   |   |     |    | $a_i^*$       |

Рис. 1. Схема преобразования вектора

Из теоремы 1 можно сформулировать следствия.

Следствие 1.1. Для того чтобы два или более двоичных вектора, суммарная размерность которых равна n, объединённые операцией конкатенации, были правильно переданы на выводы ОД, достаточно, чтобы векторное пространство тестовых воздействий, поступающих на выводы ОД, имело размерность  $m \ge n$ , а его базисные векторы не соответствовали бы одной и той же координате.

Следствие 1.2. Если векторы из векторного пространства P размерностью n преобразовать при помощи операций, указанных в теореме 1, и по два вектора, взятых из векторных пространств R и S с суммарной размерностью n преобразовать при помощи операций, указанных в следствии 1.1, то можно получить матрицу тестовых воздействий, в которой первая строка состоит из базисных векторов первого вектора пространства P, вторая — из базисных векторов первых векторов, взятых из пространств R и S, третья из базисных векторов второго преобразованного вектора пространства P и т.д.

Следствие 1.3. Двоичные векторы размерностью s меньше, чем число выводов ОД можно преобразовать с помощью операций, указанных в теореме 1, и его элементы занести в память тестовых воздействий, но тогда сигналы на остальных r-s выводах ОД будут неопределены, или им будет присвоено текущее значение соответствующих разрядов буферного блока памяти. Во избежание нежелательных последствий следует перед занесением векторов в память тестовых наборов записать во все разряды буферного блока памяти код нуля.

Для описания операции обратной идентификации, можно сформулировать и доказать следующее утверждение.

Теорема 2. Пусть базисные векторы реакций ОД представлены в n-мерном векторном пространстве  $L_n$ с произвольным порядком распределения координат  $\boldsymbol{A}^*$  задаются вектор-столбцом  $\boldsymbol{D}^*$  . Тогда часть или все ответные реакции ОД можно преобразовать в m-мерное векторное пространство при  $m \le n$  с упорядоченным ПО возрастанию порядком базисными распределения координат  $\boldsymbol{A}$ И вектор-столбцом координатами, заданными следующим образом:

$$D = C_m D^*; A = C_m A^*, (5)$$

где  $C_m$  — матрица, состоящая из m первых строк матрицы  $M^{-1}$ ;

$M^{-1}$  – матрица, обратная матрице n;

$$C_m = M^{-1}$$

при  $m = n$ .

Доказательство. Для определения m-мерного векторного пространства достаточно m координат, которые определяются из координат векторного пространства  $L_n$  с помощью мономиальной матрицы m-го порядка, следовательно, остальные элементы (n-m) столбцов матрицы  $C_m$  могут принимать только значение 0. Для обеспечения однозначности преобразований векторов из m-мерного векторного пространства в n-мерное пространство и обратно для n=m, необходимо обеспечить соблюдение условия,

при котором произведение матриц  $M \cdot C_m$  является единичной матрицей [3].

Из теоремы 2 можно получить следствие.

Следствие 2.1. При n=m все координаты векторного пространства  $L_n$  преобразуются в упорядоченные координаты A и образуется вектор реакций со всех контактов ОД.

**Пример расчета 2.** Сформировать упорядоченный вектор реакции, зафиксированный на всех контактах ОД, приведенных на рис. 1.

Создадим матрицу  $M^{-1}$ , обратную матрице M по схеме приведенной на рис. 2. Для этого к матрице M справа присоединяется единичная матрица того же порядка. Далее, элементарными преобразованиями матрица слева приводится к единичной. Аналогичные преобразования одновременно проводятся с правой матрицей, тогда на месте единичной матрицы получается матрица  $M^{-1}$ .

Рис. 2. Схема определения обратной матрицы

Исходные координаты для приведенного выше примера образуются в результате умножения матрицы  $M^{-1}$  на вектор-столбец новых координат:

Значения базисных векторов определяются следующим равенством:

Полученные координаты и базисные векторы соответствуют исходным данным на рис. 1.

В качестве основного теоретического результата как важный частный случай можно записать следующее утверждение, а также следствия для практического применения.

**Теорема 3.** Однозначная идентификация двоичных векторов n-мерного векторного пространства  $L_n$  с упорядоченным по возрастанию порядком

распределения координат  $a_i = 2^i$ , где  $i = \overline{0, n-1}$  и соответствующих им n терминальных выводов ОД, расположенных в произвольном порядке, возможна тогда и только тогда, когда координаты и базисные векторы преобразуются следующим образом:

$D^* = MD \Leftrightarrow D = M^{-1}D^*$ ;  $A^* = MA \Leftrightarrow A = M^{-1}A^*$ , (8) где M — мономиальная матрица n-го порядка, которая применяется для преобразования векторов из одного пространства в другое, D — вектор-столбец координат.

Доказательство очевидно, так как это частный случай теорем 1 и 2.

Следствие 3.1. После выполнения поразрядного сравнения ответных реакций ОД и эталонных значений и полученных результатов диагностирования в векторном пространстве  $L_m$  можно преобразовать в векторное пространство  $L_n$  и в упорядоченном виде передать в компьютер или на экран монитора в удобной для восприятия форме для последующей обработки.

Следствие 3.2. Векторы воздействий, искаженные неисправностями константного типа, возникшими на входных контактах ОД (замыкания контактов на общую шину или шину питания), можно зафиксировать в векторном пространстве  $L_m$ , преобразовать в векторное пространство  $L_n$  и использовать для формирования соответствующих диагностических сообщений.

Полученные из теоремы 1 следствия позволяют сформулировать правила для записи в память каналов тестовые воздействия от различных источников в сформированном виде, предназначенном

непосредственно для передачи на объект диагностирования.

Следствие из теоремы 2 является правилом для формирования ответных реакций в виде, предназначенном непосредственно для поразрядного сравнения с предварительно сформированными эталонными значениями.

Следствие 3.1 обеспечивает формирование правил выдачи зафиксированных неисправностей в упорядоченном виде на экран монитора для их дальнейшего анализа.

Следствие 3.2 позволяет сформировать правило локализации неисправностей на краевых входных разъемах диагностируемых SoC, что в некоторых случаях затруднительно.

# III. СТРУКТУРА ВЕКТОРНОГО МУЛЬТИПРОЦЕССОРНОГО ПРЕОБРАЗОВАТЕЛЯ

Результаты данного теоретического исследования применены для построения высокопроизводительного мультипроцессорного векторного преобразователя, выполняющего операции произвольного сдвига разрядов тестовых воздействий или выходных реакций за один период сигнала синхронизации.

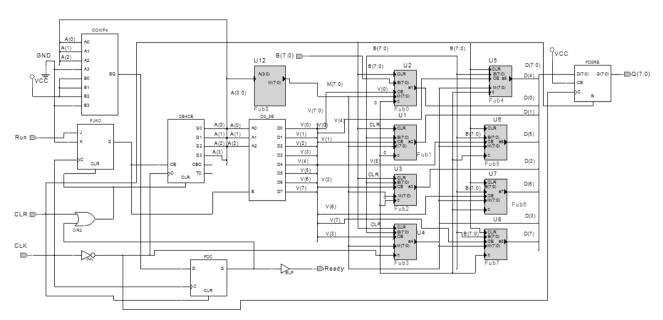

Структурная схема мультипроцессорного векторного преобразователя приведена на рис. 3. Данный преобразователь предназначен для преобразования восьмиразрядных векторов. Но предлагаемый принцип построения может быть использован для построения преобразователя, предназначенного для обработки векторов любого заданного размера.

Рис. 3. Структурная схема мультипроцессорного векторного преобразователя

По данной структурной схеме необходимо собрать два преобразователя: один для распаковки векторов воздействий, а второй для упаковки векторов ответных реакций.

Преобразователь содержит триггеры пуска и формирования сигнала готовности к работе, двоичный счетчик, дешифратор разрядов вектора, память конфигурации, 8 операционных процессоров, в состав которых входят регистры для хранения кодов соответствия разрядов вектора в логическом сечении разряду векторам в физическом сечении. Кроме того в составах операционных процессоров имеются арифметические устройства, выполняющие действия по формулам (5) или (8) в зависимости от назначения мультипроцессорного векторного преобразователя.

Различие мультипроцессорных векторных преобразователей заключается в том, что в регистрах преобразователя векторов воздействий хранятся коды матрицы M, а в преобразователе ответных реакций – коды матрицы  $M^{-1}$ .

Высокое быстродействие обработки векторов достигается за счет одновременного выполнения операций несколькими арифметическими устройствами и по сравнению с известной системой увеличено n раз, где n — длина обрабатываемых векторов [1].

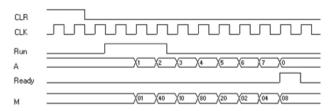

При подготовке к диагностированию нового типа SoC происходит инициализация мультипроцессорных преобразователей. Инициализация осуществляется следующим образом: на входы преобразователя поступают импульсы синхронизации СLК и сигнал CLR, который переводит компоненты в исходное состояние (рис. 3). Затем поступает сигнал пуска Run, осуществляющий запуск преобразователя. Коды строк матрицы M или  $M^{-1}$  из конфигурации заносятся регистры операционных процессоров. После заполнения кодами регистров данных процессоров, число которых равно количеству разрядов диагностируемого устройства, формируется сигнал готовности преобразователя к работе.

Рис. 3. Инициализация векторного преобразователя

В регистры преобразователя векторов воздействий при помощи дешифратора разрядов вектора заносятся коды матрицы M, составленной для нового ОД, а в регистры преобразователя ответных реакций заносятся коды матрицы  $M^{-1}$ .

Коды векторов воздействий и ответных реакций поступают на входы соответствующих мультипроцессорных векторных преобразователей, в которых, согласно уравнениям (5) и (8), за один период сигнала синхронизации выполняются преобразования векторов аппаратными средствами.

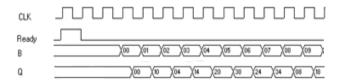

Если после подготовки преобразователя к работе на вектор воздействия, его входы В подать сформированный в виде двоичного счетчика, то через каждые полтакта синхронизирующего сигнала после подачи кодов вектора В на выходах получаются коды преобразованных векторов. Код 08 на рис. 4 не изменяется потому, что позиция разряда, соответствующая данному коду, по условию задачи не изменяется.

Рис. 4. Результаты моделирования

воздействия Тестовые без дополнительных коммутационных устройств поступают на входы диагностируемой SoC. Ответные реакции, обработанные вторым мультипроцессорным векторным преобразователем, подаются на входы диагностирующей системе в виде, удобном для поразрядного сравнения.

#### IV. Выводы

Результаты выполненного теоретического исследования позволяют проектировать мультипроцессорные преобразователи, векторные обладающие высоким быстродействием, ограниченным только быстродействием применяемых микросхем и обеспечивающих мобильное сопряжение автоматизированных средств тестового диагностирования цифровых И систем. конфигурируемых на кристалле за один период сигнала синхронизации. При этом не требуются коммутирующие дополнительные средства, необходимые при большой номенклатуре диагностируемых объектов.

Операция адаптации автоматизированных диагностических систем при смене типа SoC будет выполняться изменением содержимого памяти конфигурации преобразователей.

## Поддержка

Работа выполнена при финансовой поддержке гранта РФФИ (проект 16-08-00393).

#### ЛИТЕРАТУРА

[1] Борисенко А.А., Рябцев В.Г., Чернышев В.А., Шамарин А.Ф. Метод повышения производительности системы диагностирования цифровых блоков // Опыт разработки и внедрения технических и программных

- средств СМ ЭВМ и АСВТПС. Северодонецк: НПО «Импульс», 1986. С. 142-143.

- [2] Иванов А. Инструменты для периферийного сканирования: тестирование плат и отладка функциональных узлов // Компоненты и технологии. 2010. № 9. С. 162-166.

- [3] Основы векторного и тензорного анализа для физиков. Малышев А.И., Максимова Г.М. Электронное учебнометодическое пособие. – Нижний Новгород: Нижегородский госуниверситет. 2012. – 101 с.

- [4] Проектирование и тестирование цифровых систем на кристаллах / В.И. Хаханов, Е.И. Литвинова, О.А. Гузь. Харьков: ХНУРЭ. 2009. 484 с.

- [5] Хаханов В.И. Сервисное обслуживание современных цифровых систем на кристаллах/ В.И. Хаханов, Е.И. Литвинова, Ngene Christopher Umerah // Радіоелектронні і комп'ютерні системи. 2009. № 7 (41). С. 319-323.

- [6] Хаханов В.И., Хаханова И.В., Литвинова Е.И., Гузь О.А. Проектирование и верификация цифровых систем на кристаллах. Verilog & System Verilog/ Харьков: Новое слово, 2010. – 528 с.

- [7] Ярмолик В.Н., Иванюк А.А. Тестовое диагностирование аппаратного и программного обеспечения

- вычислительных систем / Доклады БГУИР. 2014.  $\mathbb{N}_2$  2(80). – С. 127-142.

- [8] IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan: Architecture IEEE Std 1149.7. – 2009. – 985 p.

- [9] Kaushik S. Embedded Memory Test & Repair at 20-nm Nodes and Below/ [Электронный ресурс]. Режим доступа: https://www.synopsys.com/Company/

- [10] Legat U. On line self recovery of embedded multiprocessor SoC on FPGA using dynamic partial reconfiguration / Uros Legat, Anton Biasizzo, Franc Novak // Information Technology and Control. 2012. Vol. 41. № 2. P. 116-124.

- [11] Ryabtsev V., Almadi M. New Technology for Memory Tests Design // International Journal of Modern Trends in Engineering and Research (IJMTER), Volume 02, Issue 06, 2015 – P. 520-526.

- [12] Tsu-Wei Tseng. A Shared Parallel Built-In Self-Repair Scheme for Random Access Memories in SoCs / Tsu-Wei Tseng, Jin-Fu Li // Test Conference.ITC 2008. Oct. 2008. – P.1-9.

- [13] Zorian Y., Shoukourian S. Embedded-Memory Test and Repair: Infrastructure IP for SoC Yield, IEEE Design and Test of Computers, Num. 3, Vol. 20, 2003. – P. 58–66.

# Diagnostic facilities and configurable digital systems on crystal portable integration

V.G. Ryabtsev, A.A. Shubovich, A.S. Feklistov

Volgograd Agricultural State University,

akim.onoke@mail.ru

${\it Keywords}$  — portable intregration, testing, system-on-a-chip, SoC.

#### **ABSTRACT**

The problem of automated system diagnostics and configurable digital systems on crystal portable integration is at issue. The structure of high-speed performance of multiprocessor vector inverter able to perform test bits random-shift operations during one clock signal cycle is suggested.

For performing the SoC test diagnostics, the determinate and pseudo-random tests generator, algorithmic generators and other aids are employed. Thereby the generated tests are indexed vectors wherein single bits are ordered in a strictly defined sequence in which they must be transmitted to test object's edgecard pins. Nevertheless, due to the SoC crystal design features the bus pins physical location is random. The output signal from a testing object's pins could be transformed into an ordered sequence and then compared with early prepared master values.

Ordered sequences of test signals and master responses generate testing object's logical direction. Certain location of SoC edgecard pins corresponding to input or output buses is object's physical direction. In that case, the task of identification of the object's physical and logical directions is set.

The designed structure of multiprocessor vector inverter contains vector's bit decoder, operation processors consisting of storage register for vector's bit logical and physical directions correspondence code.

The converter units for stimulus vectors unpacking and packaging response vectors based on the structural schematic are required. The difference between multiprocessor vector converters is that stimulus vectors' storage registers contain matrix M codes of object's physical and logical directions correspondence and the responses converter contains codes of reciprocal matrix  $M^{-1}$ .

In preparation for diagnosis of new type of SoC, the multiprocessor vector convertors initialization is in progress. The stimulus vector converter's registers are populated with codes of matrix M for new testing object and responses vector converter's register is populated with codes of matrix  $M^{-1}$  using the bit decoder.

# PROJECT SUPPORT

The research is powered by RFBR grant financial support (project 16-08-00393).

## REFERENCES

- [1] Borisenko A.A., Ryabtsev V.G., Chernyshov V.A., Shamrin A.F. The method of diagnosing system performance digital blocks // Experience in development and implementation of hardware and software SM computers and ASVTPS. Severodonetsk: NPO "Impulse", 1986. – P. 142-143.

- [2] Ivanov A. Tools for Boundary Scan: Test boards and debugging functional units // Components and technologies. 2010. № 9. P. 162-166.

- [3] Basics of vector and tensor analysis for physicists. Malyshev A.I., Maksimov G.M. Electronic teaching aid. – Nizhny Novgorod: Nizhny Novgorod State University. 2012. – 101 p.

- [4] Designing and testing digital systems on crystals / V.I. Khakhanov, E.I. Litvinov, O.A. Guz. Kharkov: KNURE. 2009. – 484 p.

- [5] Khakhanov V.I. Servicing of modern digital systems on crystals / V.I. Khakhanov, E.I. Litvinov, Ngene Christopher Umerah // Radio electronic and computer systems. 2009. № 7 (41). – P. 319-323.

- [6] Khakhanov V.I., Hahanova I.V., Litvinova E.I., O.A. Guz Design and verification of digital systems nakristallah. Verilog & System Verilog: Kharkov: The new Word, 2010. – 528 p.

- [7] Yarmolik V.N., Ivanyuk A.A. Test diagnosing hardware and software computer systems / Reports BSUIR. 2014. № 2 (80). – P. 127-142.

- [8] IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan: Architecture IEEE Std 1149.7. – 2009. – 985 p.

- [9] Kaushik S. Embedded Memory Test & Repair at 20-nm Nodes and Below/ [Electronic resource]. Access mode: https://www.synopsys.com/Company/

- [10] Legat U. On line self recovery of embedded multiprocessor SoC on FPGA using dynamic partial reconfiguration / Uros Legat, Anton Biasizzo, Franc Novak // Information Technology and Control. 2012. Vol. 41. № 2. P. 116-124.

- [11] Ryabtsev V., Almadi M. New Technology for Memory Tests Design // International Journal of Modern Trends in Engineering and Research (IJMTER), Volume 02, Issue 06, 2015 – P. 520-526.

- [12] Tsu-Wei Tseng. A Shared Parallel Built-In Self-Repair Scheme for Random Access Memories in SoCs / Tsu-Wei Tseng, Jin-Fu Li // Test Conference.ITC 2008. Oct. 2008. – P.1-9.

- [13] Zorian Y., Shoukourian S. Embedded-Memory Test and Repair: Infrastructure IP for SoC Yield, IEEE Design and Test of Computers, № 3, Vol. 20, 2003. P. 58–66.