# Исследование вероятностных методов оценки логической уязвимости комбинационных схем

А.Л. Стемпковский, Д.В. Тельпухов, Р.А. Соловьев, Н.В. Тельпухова Институт проблем проектирования в микроэлектронике РАН, Nofrost@inbox.ru

Аннотация — В статье исследуются вероятностные методы оценки логической уязвимости комбинационных схем, позволяющие за один проход алгоритма получить искомый полином ошибки. Исследованы вопросы, связанные с вычислительной сложностью и точностью методов в зависимости от числа первичных входов, числа элементов, а также числа реконвергентных путей. Предложен эффективный метод вычисления обобщенного коэффициента логической чувствительности схемы. На наборе тестовых схем продемонстрирована применимость высокая эффективность метода.

Ключевые слова — сбоеустойчивость, комбинационные схемы, логическое маскирование, коэффициент логической чувствительности.

#### I. Введение

Постоянное уменьшение размерностей в области микроэлектронной промышленности открывает огромные перспективы, связанные с миниатюризацией увеличением устройств, тактовых частот уменьшением пороговых напряжений, напряжений питания и т. д. Обратной стороной медали являются серьезные проблемы, возникающие при переходе к нанометровым размерностям, такие как потребляемая и рассеиваемая мощность, токи утечек и различные параметрические колебания. Большинство проблем приводят к уменьшению надежности функционирования КМОП схем [1-3], что для ряда приложений может практических ослабить преимущества, связанные с повышением степени интеграции. Более того, такие факторы как увеличение тактовых частот и уменьшение размеров также увеличивают транзисторов уязвимость интегральных схем (ИС), работающих в условиях дестабилизирующих воздействий.

Под надежностью ИС понимается степень её уязвимости к постоянным, периодическим и кратковременным ошибкам. В данной работе основное внимание уделяется кратковременным ошибкам в комбинационных участках ИС, которые возникают изза одиночных обратимых сбоев (single event transient). Источниками таких сбоев чаще всего служат попадания ионизирующих частиц, а также различные температурные эффекты и параметрические флуктуации. Исторически кратковременные ошибки были объектом повышенного внимания со стороны разработчиков элементов памяти, однако современные

исследования сбоев. показывают что вкпал участках возникающих в логических схемы. становится сравнимым с общей интенсивностью сбоев при переходе в глубоко субмикронный техпроцесс [4]. Также было показано, что составляющая интенсивности сбоев логических схем, вероятнее всего, будет доминировать в общей интенсивности сбоев даже при более низких частотах по мере роста степени интеграции [5].

обеспечения сбоеустойчивости Проблема элементов памяти сравнительно простая и не требует введения значительной избыточности, так как память оперирует со статическими данными. Одним из общепринятых решений в данной области является использование различных методов кодовой защиты данных. Защита логических блоков, с другой стороны, требует несоизмеримо больших затрат обеспечения сбоеустойчивости как методологическом плане, так и в смысле площади, производительности и мощности.

Традиционными методами обеспечения сбоеустойчивости логических схем для различных ответственных применений де факто являются методы кратного резервирования [6]. Для удовлетворения все повышающимся требованиям достижения некоторого разумного компромисса структурными затратами и уровнем сбоеустойчивости в течение последних лет предлагаются различные методы селективной защиты и масштабирования транзисторов, также методы частичного a резервирования схем [7-9], однако выбор той или иной схемы защиты по-прежнему полностью возлагается на разработчика аппаратуры. В связи с этим, в настоящее время наиболее остро стоит вопрос о создании автоматизированных средств синтеза сбоеустойчивых комбинационных схем. В этом контексте центральную роль играют исследования, касающиеся разработки быстрых и эффективных методов оценки устойчивости схем к одиночным сбоям, призванные обеспечить возможность быстрой оценки различных вариантов схемы и выбора наиболее подходящего варианта.

Все базовые подходы опираются на три разных механизма маскирования [10]: логическое маскирование - когда сбой возникает в нечувствительных к ошибкам участках схемы; электрическое маскирование - когда скачок напряжения затухает при прохождении электрической

цепи из-за передаточных характеристик используемых вентилей; временное маскирование - когда ошибка в комбинационной логике не фиксируется триггером изза его кратковременного характера. Каждый из этих механизмов влияет на общую уязвимость схемы и, соответственно, требует своих методов учета и оценки. В данной статье речь пойдет об оценке степени логического маскирования. Это отчасти обусловлено тем, что логическая составляющая маскирующих свойств схемы имеет наибольшее влияние интенсивность сбоев в схеме [11], а также является наиболее трудоемкой с вычислительной точки зрения [12]. Кроме того, можно отметить, что механизм электрического маскирования имеет место только в рамках активного логического пути, что означает высокую зависимость электрического маскирования от логического.

#### II. ОЦЕНКА СБОЕУСТОЙЧИВОСТИ ЛОГИЧЕСКИХ СХЕМ

Логическая устойчивость комбинационной схемы характеризуется интенсивностью сбоев на основных выходах схемы в условиях сбоев, возникающих на логических элементах. Интенсивность сбоев схемы является функцией от интенсивности сбоев на её компонентах, в то время как интенсивность сбоев на основных выходах зависит от маскирующих свойств схемы. Следуя модели независимых вентильных сбоев в трактовке Фон Неймана [13] будем считать, что все вентили имеют одинаковую независимую вероятность сбоя, в то время как количество ошибок в схеме не ограничено. Под ошибкой понимается инверсия сигнала на выходе вентиля.

Пусть p — вероятность сбоя вентиля, N — число входов схемы, M — число элементов в схеме, X и e - входной вектор и вектор ошибки, соответственно. Тогда надежность логической схемы характеризуется выражением, представляющим собой вероятность возникновения наблюдаемой ошибки на выходе схемы [14]:

$$F(p) = \frac{1}{2^N} \sum_{\overline{X},\overline{e}} E(X,e) p^{|\overline{e}|} (1-p)^{M-|\overline{e}|}, \qquad (1)$$

где  $E(\boldsymbol{X},\boldsymbol{e})$  - характеристическая функция, принимающая значение единицы если набор  $(\boldsymbol{X},\boldsymbol{e})$  приводит к ошибке, и ноль - в остальных случаях.

Из формулы (1) видно, что вычислительная сложность точного аналитического вычисления полинома ошибки экспоненциально зависит от числа входов и числа элементов, что делает этот метод неприменимым даже для сравнительно небольших схем. В связи с этим в настоящее время все методы оценки маскирующих свойств комбинационной логики балансируют между высокой вычислительной сложностью и точностью результатов характеристик сбоеустойчивости [15].

Одним из способов сокращения вычислительной сложности в задаче оценки сбоеустойчивости

логических схем является разработка новых эффективных метрик, в той или иной мере отражающих уязвимость к одиночным сбоям. Одной из таких метрик является обобщенный коэффициент логической чувствительности схемы (2):

$$\alpha = \frac{1}{2^N} \sum_{\overline{X}, \overline{e}, |\overline{e}| = 1} E(X, e), \qquad (2)$$

где |e|=1 говорит о том, что суммирование идет только по векторам ошибки с весом равным единице.

Другим способом являются более эффективные приближенные методы нахождения полинома ошибки (1). В рамках этого направления следует выделить стохастические подходы на основе метода Монте-Карло, а также вероятностные методы, которые подробнее рассмотрены в следующем разделе.

### III. ОЦЕНКА СБОЕУСТОЙЧИВОСТИ ЛОГИЧЕСКИХ СХЕМ С ПОМОЩЬЮ ВЕРОЯТНОСТНЫХ МЕТОДОВ

В работе рассматриваются два метода оценки логической уязвимости комбинационных схем, основанных на вероятностной логике — метод вероятностных моделей вентилей (probability gate model) [16] и сквозной метод (single pass) [17]. Их особенность заключается в том, что при вычислении параметров сбоеустойчивости используются вероятности ошибок на вентилях, а также вероятности тех или иных входов и выходов на элементе.

Стоит сразу упомянуть, что, имея дело с вероятностными подходами оценки, мы будем иметь дело и с некоторыми погрешностями. Вычисляя те или иные вероятности, делается допущение о том, что элементы схемы независимы друг от друга, что неверно в условиях наличия реконвергентных путей. Поэтому погрешность будет тем больше, чем больше случаев реконвергенции в схеме. Здесь и далее под реконвергентным путем будет пониматься пути, исходящие из одного узла и снова сходящиеся на одном из элементов.

В основе данных методов лежит наблюдение, согласно которому ошибка на выходе любого элемента зависит от суммарного эффекта вероятности ошибки на самом элементе, и вероятности ошибки, передавшейся со всех зависимых элементов предыдущих уровней. Оба метода предполагают один проход по схеме от входов к выходам и рекурсивное применение основного шага алгоритма к каждому элементу.

Для метода вероятностных вентилей этот шаг заключается в подсчете вероятности появления единицы на выходе рассматриваемого элемента с учетом вероятности фон-Неймановской ошибки p. Эта вероятность представляет собой функцию, зависящую от вероятности ошибки вентиля, и вероятностей появления единицы на первичных входах:  $\Pr(x_1, x_2, ..., x_n, p)$ .

Для сквозного метода на этом шаге осуществляется вычисление вероятности ошибки на рассматриваемом вентиле при условии, что его эталонное значение равно нулю, и той же вероятности, но при условии, что эталонное значение равно единице. Эти вероятности представляют собой функции, зависящие от вероятности ошибки вентиля  $p: \Pr_{0 \to 1}(p)$ ,  $\Pr_{1 \to 0}(p)$ .

В процессе выполнения алгоритма от элемента к элементу найденное и переданное дальше по схеме значение полинома растет. Получив значения для последнего вентиля, выхода схемы, рассчитывается сбоеустойчивость всей схемы, представленная как полином ошибки:

$$F(p) = \operatorname{Pr}_0 \cdot \operatorname{Pr}_{0 \to 1}(p) + \operatorname{Pr}_1 \cdot \operatorname{Pr}_{1 \to 0}(p),$$

где  $Pr_0$  и  $Pr_1$  - вероятности нуля и единицы на выходе схемы, работающей безошибочно.

Основные различия методов, влияющие эффективность и область их применения, заключаются в переменных, от которых зависит передаваемый по схеме полином. Метод вероятностных моделей вентилей предполагает в качестве переменных наличие не только фон-Неймановской ошибки вентиля, но и вероятности появления единицы на первичных входах схемы. Последним шагом этого метода является прогон всех возможных входных комбинаций по этому полиному. С другой стороны, сквозной метод оценки учитывает входные параметры в числовом виде на каждой итерации, передавая по схеме полином, зависящий лишь от одной переменной. Это уменьшает эффективность при росте количества элементов, но не экспоненциального роста увеличении количества входов, которое дает метод вероятностных вентилей.

## IV. ОЦЕНКА ТОЧНОСТИ И ВЫЧИСЛИТЕЛЬНОЙ СЛОЖНОСТИ МЕТОДОВ

Одной из основных характеристик, определяющих эффективность и применимость метода оценки параметров сбоеустойчивости является Вычислительную вычислительная сложность. сложность на практике удобно оценивать как время выполнения алгоритма в зависимости от некоторых параметров. Основными параметрами. определяющими время работы вероятностных методов оценки логической устойчивости схемы, являются количество элементов схемы, а также количество первичных входов.

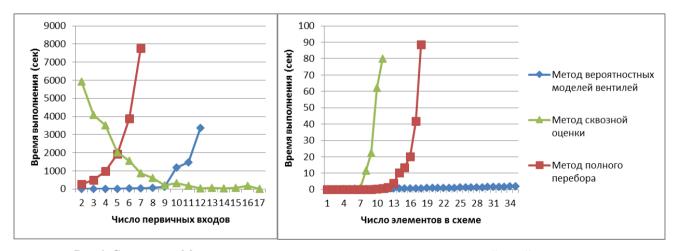

Были проведены вычислительные эксперименты, целью которых являлось определение вычислительных затрат на оценку сбоеустойчивости различных произвольных схем с помощью трех рассмотренных методов: метода вероятностных моделей вентилей, сквозного метода оценки, а также метода полного перебора. Для проведения исследований разработано программное обеспечение на языке Python 3.4, реализующее все три метода оценки, а также различные вспомогательные функции, функции генерации произвольных схем с заданным числом элементов И первичных входов. исследовании были использованы схемы, состоящие из базовых двухвходовых элементов. Оценка вычислительной сложности методов производилась на машине с двухъядерным процессором Intel Core i5-4200U с оперативной памятью 6 Гбайт DDR3L-1600. На рис. 1 представлены результаты проведенных экспериментов. Следует отметить, что каждая точка на графике была получена с помощью большого числа моделирований на различных комбинационных схемах с целью усреднения влияния числа реконвергентных путей, так как этот параметр существенно влияет на время выполнения вероятностных методов.

Рис. 1. Сравнение эффективности вероятностных методов оценки логической устойчивости схем

Анализируя полученные результаты можно сделать следующие выводы. Во-первых, как и предполагалось по формуле (1), вычислительная сложность метода

полного перебора экспоненциально зависит как от числа элементов схемы, так и от числа первичных входов. Во-вторых, метод вероятностных моделей

вентилей линейно зависит от числа элементов в схеме и экспоненциально от числа первичных входов. Это связанно с тем, что финальное выражение для вероятности единицы на выходе схемы вычисляется быстро в один проход, однако затем требуется полный перебор всех входных комбинаций, что обуславливает экспоненциальную зависимость от числа входов схемы. Также стоит отметить, что несмотря на то, что метод сквозной оценки работает за один проход по схеме, на графиках наблюдается экспоненциальная зависимость от числа элементов. Это связано со сложностью основного шага алгоритма, последовательно применяемого для каждого элемента схемы. Так как на этом шаге мы оперируем полиномами, с ростом количества элементов, будут усложняться операнды, и как следствие, время выполнения будет экспоненциально увеличиваться. Существенное снижение времени выполнения метода сквозной оценки при увеличении первичных входов на первый взгляд может показаться странным, однако объясняется внутренними особенностями метода. Дело в том, что на основном шаге алгоритма вероятности входных наборов для каждого элемента учитываются в численном виде, поэтому по мере роста количества входов, эффективность не будет падать, как у других методов. Увеличение же эффективности обусловлено тем, что когда у элемента входные наборы зависят от первоначальных входов схемы, а не других элементов, то мы оперируем не полиномами, а числами, что, очевидно, быстрее.

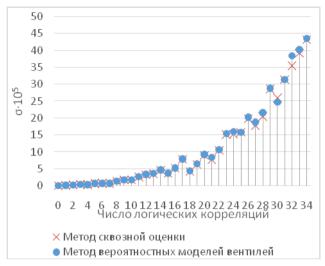

Помимо вычислительной сложности методов, для более полной картины также требуется оценить их точность в сравнении с методом полного перебора. Единственным источником погрешности для обоих вероятностных методов, как уже отмечалось ранее, является количество реконвергентных путей в схеме. Реконвергентные пути вносят дополнительные зависимости между внутренними узлами схемы, которые не учитываются рассматриваемыми методами. качестве количественного показателя взаимосвязей был использован параметр, характеризующий число логических корреляций в схеме, вычисляющийся как число повторяющихся входных переменных в списке зависимостей каждого вентиля в схеме.

В качестве метрики, характеризующей точность рассматриваемых методов, было выбрано среднеквадратичное отклонение полиномов на интервале [0,0.1]:

$$\sigma = \int_{0}^{0.1} (f(p) - F(p))^2 \partial p,$$

где f(p) - полином ошибки, полученный одним из вероятностных методов; F(p) - полином ошибки, полученный методом полного перебора.

На рис. 2 представлен график зависимости точности рассматриваемых методов от количества логических корреляций.

Рис. 2. Оценка точности вероятностных методов в зависимости от числа реконвергентных путей

#### V. ЗАКЛЮЧЕНИЕ

В статье были рассмотрены вероятностные методы получения полинома ошибки, который в свою очередь характеризует логическую устойчивость комбинационной схемы к одиночным сбоям. Исследования вычислительной сложности методов продемонстрировали существенные различия относительно зависимости от числа вхолов и числа элементов схемы, что позволяет выработать некоторые рекомендации относительно использования того или иного метода для конкретной комбинационной схемы.

Точность методов была проанализирована на широком наборе схем с разным количеством реконвергентных путей. Оба метода ожидаемо продемонстрировали существенную зависимость от степени реконвергентности схемы, в то время как точность рассматриваемых методов оказалась практически идентичной.

Дальнейшие исследование планируется посвятить разработке вероятностных методов для вычисления метрик сбоеустойчивости, таких как коэффициент логической чувствительности [18].

Исследование выполнено за счет гранта Российского научного фонда (проект №14-19-01036).

#### ЛИТЕРАТУРА

- [1] Shivakumar P., Kistler M., Keckler S.W., Burger D., Alvisi L. Modeling the effect of technology trends on the soft error rate of combinational logic // Proceedings of international conference on dependable systems and networks, 2002 (DSN 2002), June 2002. p. 389–98.

- [2] Narayanan V., Xie Y. Reliability concerns in embedded system designs // Computer 2006; 39(1): 118–20.

- [3] Franco D.T., Naviner J.-F., Naviner L. Yield and reliability issues in nanoelectronic technologies // Ann Télécommun 2006; 61(11–12):1422–57.

- [4] Asadi H., Tahoori M.B., Fazeli M., Miremadi S.G. Efficient algorithms to accurately compute derating factors of digital circuits // Microelectron Reliab 2012; 52(6):1215–26.

- [5] Han J., Gao J., Qi Y., Jonker P.P., Fortes J.A.B. Toward hardware-redundant, fault tolerant logic for nanoelectronics // IEEE Des Test Comput 2005; 22(4):328–39.

- [6] Стемпковский А.Л., Тельпухов Д.В., Соловьев Р.А., Мячиков М.В. Повышение отказоустойчивости логических схем с использованием нестандартных мажоритарных элементов // Информационные технологии. 2015. Т. 21. № 10. С. 749-756.

- [7] Zhou Q., Mohanram K. Gate sizing to radiation harden combinational logic // IEEE Trans Comput-Aid Des Integrat Circuit Syst 2006;25(1):155–66.

- [8] Dhillon Y., Diril A., Chatterjee A., Singh A. Analysis and optimization of nanometer cmos circuits for soft-error tolerance // IEEE Trans Very Large Scale Integrat (VLSI) Syst 2006;14(5):514–24.

- [9] Nieuwland A., Jasarevic S., Jerin G. Combinational logic soft error analysis and protection // 12th IEEE international on-line testing symposium, 2006 (IOLTS 2006), 10–12 July 2006. p. 6.

- [10] Shivakumar P., Kistler M., Keckler S.W., Burger D., Alvisi L. Modeling the effect of technology trends on the soft error rate of combinational logic // Int. conf. on dependable systems and networks (DSN 2002), Bethesda, MD, USA, June 2002, p. 389–98

- [11] Asadi H., Tahoori M.B., Fazeli M., Miremadi S.G. Efficient algorithms to accurately compute derating factors of digital circuits // Microelectron Reliab 2012;52(6):1215–26.

- [12] George N., Lach J. Characterization of logical masking and error propagation in combinational circuits and effects on system vulnerability // Dependable Systems Networks (DSN), 2011 IEEE/IFIP 41st International Conference on, 2011, pp. 323-334.

- [13] J. von Neumann Probabilistic logics and the synthesis of reliable organisms from unreliable components // Automata Studies, C. E. Shannon and J. McCarthy, Eds. Princeton, NJ: Princeton Univ. Press, 1956, pp. 43–98.

- [14] Стемпковский А.Л., Тельпухов Д.В., Соловьев Р.А., Соловьев А.Н., Мячиков М.В. Моделирование возникновения неисправностей для оценки надежностных характеристик логических схем // Информационные технологии. 2014. № 11. С. 30-36.

- [15] Xiao R., Chen C. Gate-level circuit reliability analysis: A survey // VLSI Design, Vol. 2014, Article ID 529392, pp. 1-12, 2014.

- [16] Han J., Chen H., Boykin E., Fortes J. Reliability evaluation of logic circuits using probabilistic gate models // Microelectronics Reliability 2011;51(2):468–76.

- [17] Choudhury M.R., Mohanram K. Reliability analysis of logic circuits // IEEE Trans CAD 2009;28(3):392–405.

- [18] Стемпковский А.Л., Тельпухов Д.В., Соловьев Р.А., Мячиков М.В., Тельпухова Н.В. Разработка технологически-независимых метрик для оценки маскирующих свойств логических схем // Вычислительные технологии. 2016. Т. 21. № 2.

# Probabilistic methods for reliability evaluation of combinational circuits

A.L. Stempkovskiy, D.V. Telpukhov, R.A. Soloviev, N.V. Telpukhova Institute for Design Problems in Microelectronics of RAS, nofrost@inbox.ru

Keywords — fault-tolerance, combinational circuits, logic masking, logic sensitivity factor.

#### ABSTRACT

Modern microelectronic devices design is closely associated with the demand to increase the integration level, performance and reliability. With the integration level increase and the element sizes decrease the importance of improving reliability and noise immunity of devices to the various sources of interference and failures correspondingly grows. These sources include the process radiation, crosstalk, temporary degradation, the power surges et al. This problem is especially urgent in military, aerospace, medical and other fields of human activity associated with high risks associated with undetected errors. Currently the noise immunity becomes a prerequisite of efficiency and reliability in electronic hardware design. Therefore, the research and development of the methods improving microelectronic circuits' fault tolerance are the items of great importance.

Despite the progress in the design of code protection methods intended for storage, transfer and arithmetic processing of data in order to provide the desired level of arithmetic and logic circuit fault-tolerance the archaic methods of adding multiple redundancies are still used. Thus it is very important to develop the efficient methods to increase the noise immunity characteristics of the logic circuits. The key aspect of this problem is the development of methods for the estimation of the proposed approaches efficiency.

The existing methods of fault tolerance analysis for combinational circuits require certain trade-off between the complexity and the accuracy. The reason is the exponential computational complexity growth with primary inputs and number of elements in the case of the accurate algorithms.

This paper contains a survey of the various reliability estimation methods based on probabilistic properties of the signals and the gates. Two methods are presented and discussed in detail: the method based on the probabilistic gate models (PGM) and the single-pass method. Both the complexity and accuracy of each method are addressed and compared.

The analysis of the computational complexity has demonstrated significant differences regarding the dependence on the number of inputs and the number of circuit elements. This allows to develop some guidelines about the use of a particular method for a particular combinational circuit.

The accuracy of the methods has been analyzed on a wide variety of circuits with different numbers of reconvergent fan-outs. Both methods have demonstrated the expected significant dependence on the reconvergence degree while the accuracy of these methods was almost identical.

Further research will be concerned with the development of probabilistic methods of the new fault-tolerance metrics calculation such as the logical sensitivity

The reported study was supported by the Russian Science Foundation (RSCF), research project №14-19-01036.

#### REFERENCES

- Shivakumar P, Kistler M, Keckler SW, Burger D, Alvisi L. Modeling the effect of technology trends on the soft error rate of combinational logic. In: Proceedings of international conference on dependable systems and networks, 2002 (DSN 2002), June 2002. p. 389–98.

- [2] Narayanan V, Xie Y. Reliability concerns in embedded system designs. Computer 2006; 39(1): 118–20.

- [3] Franco DT, Naviner J-F, Naviner L. Yield and reliability issues in nanoelectronic technologies. Ann Télécommun 2006; 61(11–12):1422–57.

- [4] Asadi H, Tahoori MB, Fazeli M, Miremadi SG. Efficient algorithms to accurately compute derating factors of digital circuits. Microelectron Reliab 2012; 52(6):1215–26.

- [5] Han J, Gao J, Qi Y, Jonker PP, Fortes JAB. Toward hardware-redundant, fault tolerant logic for nanoelectronics. IEEE Des Test Comput 2005; 22(4):328–39.

- [6] Stempkovskiy A.L., Telpukhov D.V., Soloviev R.A., Myachikov M.V. Povyshenie otkazoustojchivosti logicheskih shem s ispol'zovaniem nestandartnyh mazhoritarnyh jelementov // Informacionnye tehnologii. 2015. Vol. 21. № 10. pp. 749-756. (in Russian).

- [7] Zhou Q, Mohanram K. Gate sizing to radiation harden combinational logic. IEEE Trans Comput-Aid Des Integrat Circuit Syst 2006;25(1):155–66.

- [8] Dhillon Y, Diril A, Chatterjee A, Singh A. Analysis and optimization of nanometer cmos circuits for soft-error tolerance. IEEE Trans Very Large Scale Integrat (VLSI) Syst 2006;14(5):514–24.

- [9] Nieuwland A, Jasarevic S, Jerin G. Combinational logic soft error analysis and protection. In: 12th IEEE international on-line testing symposium, 2006 (IOLTS 2006), 10–12 July 2006. p. 6.

- [10] Shivakumar P, Kistler M, Keckler SW, Burger D, Alvisi L. Modeling the effect of technology trends on the soft error rate of combinational logic. In: Int. conf. on dependable systems and networks (DSN 2002), Bethesda, MD, USA, June 2002. p. 389–98

- [11] Asadi H, Tahoori MB, Fazeli M, Miremadi SG. Efficient algorithms to accurately compute derating factors of digital circuits. Microelectron Reliab 2012;52(6):1215–26.

- [12] N. George and J. Lach, "Characterization of logical masking and error propagation in combinational circuits and effects on system vulnerability," in Dependable Systems Networks (DSN), 2011 IEEE/IFIP 41st International Conference on, 2011, pp. 323-334.

- [13] J. von Neumann, "Probabilistic logics and the synthesis of reliable organisms from unreliable components," in Automata Studies, C. E. Shannon and J. McCarthy, Eds. Princeton, NJ: Princeton Univ. Press, 1956, pp. 43–98.

- [14] Stempkovskiy A.L., Telpukhov D.V., Soloviev R.A., Soloviev A.N., Myachikov M.V. Modelirovanie vozniknovenija neispravnostej dlja ocenki nadezhnostnyh harakteristik logicheskih shem // Informacionnye tehnologii. 2014. № 11. pp. 30-36. (in Russian).

- [15] R. Xiao, C. Chen, "Gate-level circuit reliability analysis: A survey," VLSI Design, Vol. 2014, Article ID 529392, pp. 1-12, 2014.

- [16] Han J, Chen H, Boykin E, Fortes J. Reliability evaluation of logic circuits using probabilistic gate models. Microelectronics Reliability 2011;51(2):468–76.

- [17] Choudhury MR, Mohanram K. Reliability analysis of logic circuits. IEEE Trans CAD 2009;28(3):392–405.

- [18] Stempkovskiy A.L., Telpukhov D.V., Soloviev R.A., Myachikov M.V., Telpukhova N.V. Razrabotka tehnologicheski-nezavisimyh metrik dlja ocenki maskirujushhih svojstv logicheskih shem // Vychislitel'nye tehnologii. 2016. Vol. 21. № 2. (in Russian).