# Синтез контроллера внешних прерываний с динамически изменяемым приоритетом

А.П. Самойленко, А.И. Панычев, С.А. Панычев Южный федеральный университет, ruu2011@mail.ru

Аннотация — С целью повышения эффективности управляющего вычислительного комплекса бортового радиоэлектронного оборудования предложен эффективный по ресурсам и времени метод динамического управления потоками информации. Показано, что применение метода формирования динамически изменяющейся очереди заявок целесообразно в случаях, когда параметры входного потока резко меняются по уровню и во времени или имеют случайный характер. Разработано прикладное математическое обеспечение и соответствующий алгоритм, реализующий упорядочение больших однородных массивов на основе использования математического аппарата порядковой логики. Описана процедура раскрытия логического определителя, адаптированная к аппаратной реализации. Разработан функциональноориентированный контроллер внешних прерываний с изменяемым приоритетом. Контроллер функционирует по алгоритму динамического упорядочения массива поступающих от датчиков состояний сигналов по интегральному уровне-темпоральному критерию приоритетов. Эффективность контроллера обеспечена отсутствием избыточности, высокой разрешающей способностью и быстродействием благодаря одновременному сравнению приоритетов поступающих заявок.

Ключевые слова — автомат контроля, диагностика, датчик, приоритет, регистр, упорядочение элементов массива, порядковая логика, бесконечнозначная логика, логический определитель, темпоральный критерий, интегральный критерий.

#### I. Введение

Управляющие вычислительные комплексы (УВК) авиационной и космической техники относятся к классу динамических систем реального времени, в оперативной памяти которых хранится информационный образ, отображающий текущее состояние бортового радиоэлектронного оборудования (БРЭО) в соответствии с сигналами, получаемыми от датчиков функциональных контрольных точек (ФКТ) [1].

Контролируемые параметры БРЭО наряду с флуктуационными изменениями внутри регламентируемых допусков имеют тенденцию к случайным выбросам значений за пределы допусков как в сторону увеличения, так и в сторону уменьшения. В общем случае параметры БРЭО представляет собой случайную функцию времени, режима функционирования, динамического состояния элементов системы и других факторов. Функции

контроля состояния, диагностики и восстановления работоспособности БРЭО выполняет встроенный автомат контроля, имеющий программный модуль для тестирования ФКТ по внешнему прерыванию работы УВК.

Анализ архитектурных особенностей контроллеров внешних прерываний (КВП) микропроцессорных наборов позволяет выделить следующие классы организации систем прерывания [2]: по методу опроса; по выбору вектора; по «дейзи-цепочке»; на основе сравнения с кодом порога; по таймеру счетчика событий; переменное прерывание посредством маскирования.

Поскольку параметры БРЭО неоднородны, время и величина их выхода за пределы допусков случайны, параметров различна, значимость ввиду функциональных ограничений традиционных КВП их применение в автоматах контроля работоспособности БРЭО, функционирующих в режиме Real Time, что существенная приводит тому, вычислительных ресурсов тратится на распределение информации в памяти УВК, организацию доступа к информационным массивам, упорядочивание данных [3-6].

требуемая C учетом этих обстоятельств эффективность УВК может быть достигнута применением КВП с динамически изменяемыми приоритетами в соответствии с текущим состоянием БРЭО, реализующих алгоритм упорядочения массива поступающих в УВК заявок согласно траекторий изменяемых параметров БРЭО линамически относительно регламентируемых допусков [2, 7].

## II. ПОСТАНОВКА ЗАДАЧИ

На основе анализа последовательности сигналов, формируемых датчиками ФКТ БРЭО, разработать оптимальный по ресурсам и времени метод динамического управления УВК. Осуществить принцип аппаратного управления посредством КВП в соответствии с динамикой отклонений контролируемых параметров от регламентируемых допусков и с учетом реального времени запаздывания («старения») запросов на прерывание.

# III. МАТЕМАТИЧЕСКОЕ ОБЕСПЕЧЕНИЕ ФУНКЦИОНАЛЬНО-ОРИЕНТИРОВАННОГО КОНТРОЛЛЕРА ВНЕШНИХ ПРЕРЫВАНИЙ

Традиционным методом анализа функционального состояния и работоспособности БРЭО является поллинг обработки циклический массива зафиксированных значений контролируемых параметров с последующим принятием решения об оценке интегрального состояния системы [8-14]. Такая технология чревата чрезмерной информационной избыточностью и независимостью мониторинга поллинга от изменения параметров. Вследствие этого она является неэффективной, поскольку приводит к старению информации.

С целью повышения эффективности приходится увеличивать быстродействие процессов сбора и обработки данных, что существенно повышает удельную стоимость процесса диагностики.

Таким образом, актуальна необходимость подбора адекватного математического инструментария для реализации аппаратного поиска и упорядочения больших однородных массивов, обеспечивающего более медленный рост трудоемкости поиска.

# А. Технология упорядочения однородных массивов

Эффективная процедура упорядочения больших однородных массивов может быть реализована на основе использования математического аппарата порядковой логики [15]. Предлагается следующий способ упорядочения элементов в массиве:

- 1) приоритеты заявок формируются путем одновременного сравнения значений параметров между собой и выделения элемента с наибольшим отклонением за пределы допусков;

- 2) в случае равенства приоритетов у двух и более заявок выбор для обслуживания производится по дополнительному признаку, например, по значению первой производной временных траекторий параметров;

- 3) на последующих интервалах времени сравниваются приоритеты еще необслуженных заявок.

Построим алгоритм поиска заданного элемента и его места в числовом массиве. Рассмотрим неупорядоченное множество чисел

$$A_n = \{a_1, a_2, ..., a_n\}$$

(1)

в качестве математической модели простейшего неупорядоченного информационного массива. Требуется найти некоторый r -й элемент  $a^{(r)}$  множества (1).

Множество  $A_n$  можно представить в виде квазиматрицы, при этом  $a^{(r)}$  численно равно определителю-столбцу r -го ранга:

$$A_n = \begin{vmatrix} a_1 \\ \dots \\ a_n \end{vmatrix}, \ a^r = A_n^r, \ A_n^r = \begin{vmatrix} a_1 \\ \dots \\ a_n \end{vmatrix}^r, \ r = \overline{1, n}.$$

(2)

Раскрыв логический определитель (ЛО) (2), получим функцию бесконечнозначной логики  $f_r$ , выражающую искомый элемент  $a^{(r)}$  через элементы  $a_1, ..., a_n$  множества  $A_n$ .

Рассмотрим частично упорядоченное множество чисел

$$A_n = \{a_{11}, ..., a_{1m_1}, a_{21}, ..., a_{2m_2}, ..., a_{q1}, ..., a_{qm_q}\},$$

$$\sum_{i=1}^{q} m_i = n , \qquad (3)$$

состоящее из q подмножеств  $Q_1, Q_2, ..., Q_q$  , упорядоченных согласно правилу

$$a_{11} < a_{12} < \dots < a_{1m_1}, a_{21} < a_{22} < \dots < a_{2m_2},$$

$$a_{q1} < a_{q2} < \dots < a_{qm_a}, a_{1m_1} < a_{2m_2} < \dots < a_{qm_a}.$$

Считаем множество (3) математической моделью частично упорядоченного информационного массива.

Требуется найти r -й по порядку величины элемент  $a^{(r)}$  множества (3). Представим это множество в виде

$$A_{q} = \begin{vmatrix} a_{11} & \dots & a_{1m_{1}} \\ \dots & \ddots & \dots \\ a_{q1} & \dots & a_{qm_{q}} \end{vmatrix} . \tag{4}$$

Элемент  $a^{(r)}$  равен общему определителю r -го ранга квазиматрицы (4):

$$a^r = A_a^r$$

,

где

$$A_{q}^{r} = \begin{vmatrix} a_{11} & \dots & a_{1m_{1}} \\ \dots & \ddots & \dots \\ a_{q1} & \dots & a_{qm_{q}} \end{vmatrix}^{r} = \bigvee_{\substack{\sum \\ 1 \ r_{i} = r+q-1}} (a_{11}, \dots, a_{qq}). (5)$$

Функция бесконечнозначной логики  $f_r$  задает алгоритм поиска элемента  $a^{(r)}$  в неупорядоченном массиве и является поисковой функцией. При этом определитель можно рассматривать как компактное блочное описание алгоритма поиска, подобное блочному описанию линейных преобразований с помощью матриц [15].

С целью построения эффективных с точки зрения аппаратной реализации алгоритмов упорядочения в больших массивах предлагается производить раскрытие ЛО в соответствии со следующей процедурой.

Квазиматрица упорядочиваемого по приоритетам массива заявок  $\Lambda_n = \{\lambda_1, ..., \lambda_n\}$  представляется в двоичном виде

$$\lambda^{(1)} = \begin{vmatrix} \overline{\lambda}_{1} \\ \dots \\ \overline{\lambda}_{n} \end{vmatrix}^{(1)} = \begin{vmatrix} \lambda_{1}^{m} & \lambda_{1}^{m-1} & \cdots & \lambda_{1}^{1} \\ \lambda_{2}^{m} & \lambda_{2}^{m-1} & \cdots & \lambda_{2}^{1} \\ \dots & \dots & \ddots & \dots \\ \lambda_{n}^{m} & \lambda_{n}^{m-1} & \cdots & \lambda_{n}^{1} \end{vmatrix}^{(1)}, \quad (6)$$

где  $\overline{\lambda}_i = \left(\lambda_i^m, \ldots, \lambda_i^1\right), \ i = \overline{1,n}$  — значение приоритета заявки, представленное в m -разрядном двоичном коде;  $\lambda_i^j \in \left\{0,1\right\}$  — j -разрядный коэффициент  $\overline{\lambda}_i$  ;  $j = \overline{1,m}$  .

Способ раскрытия ЛО (6) для вычисления максимального элемента  $\lambda^{(1)}$  в дизъюнктивной нормальной форме состоит в следующем.

На каждом j-м этапе производится рекурсивное вычисление соответственно разрядных коэффициентов  $\mathcal{X}_{extr}^{j}$  и адресно-разрядных коэффициентов  $Z^{j}$  в порядке от старших разрядов к младшим по правилам:

$$\lambda_{extr}^{j} = \max_{i=1}^{n} \left\{ \left( \lambda_{1}^{j} \& Z_{1}^{j+1} \right), \dots, \left( \lambda_{n}^{j} \& Z_{n}^{j+1} \right) \right\} = \bigvee_{i=1}^{n} \left( \lambda_{n}^{j} \& Z_{n}^{j+1} \right),$$

$$\lambda_{extr}^{j} \in \left\{ 0,1 \right\}, \quad j = \overline{m-1,1},$$

$$Z^{j} = \min_{i=1}^{n} \left( Z^{j+1}, \left( \overline{\lambda_{extr}^{j}} \vee \lambda_{i}^{j} \right) \right) =$$

$$= Z^{j+1} \& \left( \overline{\lambda_{extr}^{j}} \vee \begin{vmatrix} \lambda_{1}^{j} \\ \lambda_{2}^{j} \\ \dots \\ \lambda_{n}^{j} \end{vmatrix} \right) = \begin{vmatrix} Z_{1}^{j} \\ Z_{2}^{j} \\ \dots \\ Z_{n}^{j} \end{vmatrix},$$

$$Z_{i}^{j} = Z_{i}^{j+1} \& \left( \overline{\lambda_{extr}^{j}} \vee \lambda_{i}^{j} \right), \quad i = \overline{1, n}.$$

$$(7)$$

На последнем, m -м этапе, вырабатывается экстремальное значение интенсивности импульсной последовательности, представленное в m -разрядном двоичном коде

$$\overline{\lambda}_{extr} = \left| \lambda_{extr}^m, \lambda_{extr}^{m-1}, ..., \lambda_{extr}^1 \right|$$

и столбец адресно-разрядных коэффициентов первого разряда

$$Z^{1} = \begin{bmatrix} Z_{1}^{2} & & \left(\overline{\lambda}_{extr}^{1} \vee \lambda_{1}^{1}\right) \\ Z_{2}^{2} & & \left(\overline{\lambda}_{extr}^{1} \vee \lambda_{2}^{1}\right) \\ & \dots \\ Z_{n}^{2} & & \left(\overline{\lambda}_{extr}^{1} \vee \lambda_{n}^{1}\right) \end{bmatrix} = \begin{bmatrix} Z_{1}^{1} \\ Z_{2}^{1} \\ \dots \\ Z_{n}^{1} \end{bmatrix}.$$

(8)

Столбец (8) может содержать один или несколько единичных элементов, соответствующих экстремальным (максимальным) числовым значениям, то есть наиболее приоритетным заявкам в УВК. При

наличии одного единичного элемента применение к (8) функции кодирования позволяет получить первоначальный адрес заявки с максимальным приоритетом. Наличие нескольких элементов свидетельствует о том, что имеется несколько заявок с одинаковым приоритетом, тогда в данном случае необходим выбор по дополнительному критерию, например, по порядковым номерам заявок. В общем случае получить адрес заявки с наибольшим приоритетом позволяет операция кодирования вида

$$Adr(i) = F_{CD}(Z^i), (9)$$

где  $\mathit{F}_{\mathit{CD}}$  – операция формирования адреса  $\mathit{i}$  -й заявки.

Предлагаемый алгоритм является одним из эффективных методов раскрытия ЛО квазиматрицы большой размерности с индикацией первичных адресов элементов матрицы, поскольку, в отличие от [15], алгоритм:

- 1) характеризуется свойствами однородности и параллельности;

- 2) обладает достаточно высоким быстродействием, определяемым быстродействием переходных процессов в элементах;

- 3) позволяет работать с массивами чисел в прямом и обратном кодах, что вдвое сокращает инерционность.

- В. Технология темпоральной оценки информационных потоков

Процесс контроля функционального состояния БРЭО характеризуется не только измерением значений отклонения параметров за пределы регламентируемых допусков, но и темпоральной составляющей, учитывающей степень временного запаздывания (степень «старения» данных) [16, 17].

Из теории приоритетных систем массового обслуживания известно, что статистический приоритет p поступившей в систему заявки определяется с учетом значений коэффициента штрафа за задержку в обслуживании на единицу времени (или за потерю заявки)  $\alpha_n$  и длительности ее обслуживания  $\nu_n$ :

$$\frac{\alpha_{p-1}}{\nu_{p-1}} > \frac{\alpha_p}{\nu_p} > \frac{\alpha_{p+1}}{\nu_{p+1}} \ . \tag{10}$$

Динамический приоритет формируется путем периодического пересмотра очереди заявок УВК с учетом времени пребывания каждой из них в системе и функции изменения приоритета заявки во времени. Время пребывания j-й заявки в УВК определяется выражением

$$v_i = \omega_i + \tau_i$$

где  $\omega_j$  — время ожидания обслуживания (сумма времени пребывания заявки в очереди до начала обслуживания в УВК и времени ожидания в очереди в

прерывном состоянии);  $j = \overline{1,n}$  — номер заявки;  $\tau_j$  — длительность обслуживания j -й заявки.

Если  $v_j'$  — предельно допустимое время пребывания j -й заявки в УВК, то необходимо выполнить условие

$$v_j \le v_j' \,. \tag{11}$$

Это условие соблюдается только за счет изменения времени ожидания обслуживания  $\omega_j$ . При этом, с одной стороны, при уменьшении длительности ожидания обслуживания приоритет заявки может повышаться, так как со временем вероятность превышения допустимого времени ожидания увеличивается. С другой стороны, при длительном пребывании заявки в системе содержащаяся в ней информация «стареет», поэтому приоритет заявок может со временем уменьшаться.

Если допустить, что  $y_j = f(t_j)$  — функция изменения приоритета j -й заявки от времени её пребывания в УВК  $t_j$ , то приоритет j -й заявки пропорционален первой производной этой функции  $\frac{df(t_j)}{dt} = f'(t_j) \quad , \quad \text{величина} \quad dt \quad \text{может} \quad \text{быть}$  интерпретирована как интервал между соседними значениями времени, в которых пересматриваются приоритеты заявок, находящихся в очереди в УВК.

Приоритет находящихся в очереди УВК заявок одного типа (для которых одинаковы отклонения  $\alpha/\nu$ ) целесообразно распределять пропорционально первым производным функций изменения приоритетов

$$f_p'(t) > f_{p+1}'(t) > \dots$$

(12)

С учетом (10) и (12) динамический приоритет заявок, находящихся в очереди УВК, распределяется в зависимости от соотношения

$$\left[\frac{\alpha_j}{v_j}f_j'(t)\right]_p > \left[\frac{\alpha_i}{v_i}f_i'(t)\right]_{p+1}, \tag{13}$$

то есть из двух заявок j и i , находящихся на обслуживании в УВК, высший приоритет присваивается той, для которой больше значение  $\frac{\alpha}{V}f'(t)$  .

Таким образом, для управления очередью заявок в УВК каждая (для примера j -я) поступающая в систему заявка должна характеризоваться следующими параметрами:  $\alpha_j, \nu_j', f_j'(t), \nu_j, T_j$ , где  $T_j$  – момент время поступления заявки в систему.

После вычисления приоритетов по зависимости (13) проверяется условие (11). При этом время

ожидания обслуживания заявки j-го типа, которой присвоен приоритет p, составляет

$$\omega_p = \sum_{j=0}^{p-1} v_j .$$

Для i -й заявки должно выполняться условие

$$v_i' \ge \sum_{j=0}^{p-1} v_j + v_p = \sum_{j=0}^{p} v_j$$

(14)

При невыполнении (14) система снимает i -ю заявку с обслуживания и выдает соответствующее сообщение. Таким образом, применение метода формирования динамически изменяющейся очереди заявок целесообразно в случаях, когда параметры входного потока резко меняются во времени.

По значениям (14) формируется квазиматрица, аналогичная (4), и обрабатывается по технологии порядково-логического анализа (6)—(8). В итоге каждая заявка будет представлена как темпоральным показателем (14), так и его адресом *i* , указывающим принадлежность сигналу функционального состояния БРЭО.

# С. Интегрально-аддитивный критерий значимости информационного потока

Каждый i -й элемент входного информационного потока КВП характеризуется двумя независимыми показателями — уровневым и темпоральным. Приоритеты обслуживания формируются на основе порядково-логической технологии независимо для каждого из учитываемых критериев.

Чтобы учесть оба показателя сигнала диагностической системы, выходной сигнал КВП должен формироваться на основании функционального компромисса исходя из динамики отклонения параметра от допусковой зоны и времени его запаздывания.

В связи с этим выходной сигнал контроллера должен учитывать априорные оценки значимости уровневого  $\overline{\lambda}_i$  и темпорального  $v_i$  показателей. Предлагается использовать методологию аддитивного формирования интегрального критерия каждого параметра:

$$\varphi_i(\overline{\lambda}_i, \nu_i) = b_{1i}\overline{\lambda}_i + b_{2i}\nu_i, \qquad (15)$$

где  $b_{ki}$  ,  $k=\overline{1,2}$  — экспертные коэффициенты значимости параметров, выбираемые из условия  $\sum_{k=1}^2 b_{ki} = 1 \; , \; i=\overline{1,n} \; .$

# IV. СТРУКТУРА ПОРЯДКОВО-ЛОГИЧЕСКОГО ПРОЦЕССОРА КОНТРОЛЛЕРА ВНЕШНИХ ПРЕРЫВАНИЙ

Процессор в составе КВП для упорядочивания элементов в массивах большой размерности

разработан на базе математического аппарата порядковой логики и логических определителей. В процессоре реализованы алгоритмы упорядочения массивов путем поблочного разложения исходной квазиматрицы, задаваемые процедурами (4)—(8).

В отличие от программной реализации алгоритма определения экстремальных значений сравниваемых параметров комбинаторными методами, характерной для микропроцессоров традиционной архитектуры, разрабатываемый порядково-логического процессор (ПЛП) позволит решить задачу выбора экстремального операнда и его адреса за один такт.

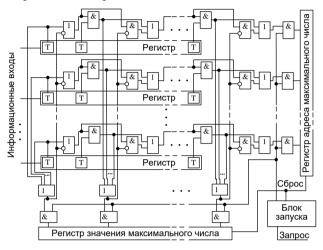

Рис. 1. Функциональная схема порядково-логического процессора

Функциональная схема ПЛП для поиска максимального значения и его позиции в числовом массиве приведена на рис. 1.

Процессор содержит блок запуска, регистры фиксации значения максимального числа, адреса максимального числа, значений анализируемых параметров, разрядные элементы «И», «ИЛИ», группы элементов «И», «ИЛИ».

ПЛП позволяет обработать весь массив данных за один цикл и установить экстремальное значение параметра и адрес регистра, где оно содержится. Строка, содержащая максимальный элемент, далее не рассматривается. Процесс повторяется до тех пор, пока массив не будет полностью упорядочен [18].

# V. СТРУКТУРА КОНТРОЛЛЕРА ВНЕШНИХ ПРЕРЫВАНИЙ

Сигнал внешнего прерывания бортового УВК формируется в соответствии с адресами экстремальных параметров, определяемыми по (9), значением максимального уровневого операнда, рассчитанным по (7), (8), и соотношением первых производных по времени, полученным по (12), (13).

Аппаратная реализация фиксации уровневого и темпорального параметров и их адресов осуществляется ПЛП, представленным на рис. 1, представляющим реляторный процессор и являющимся элементом архитектуры КВП.

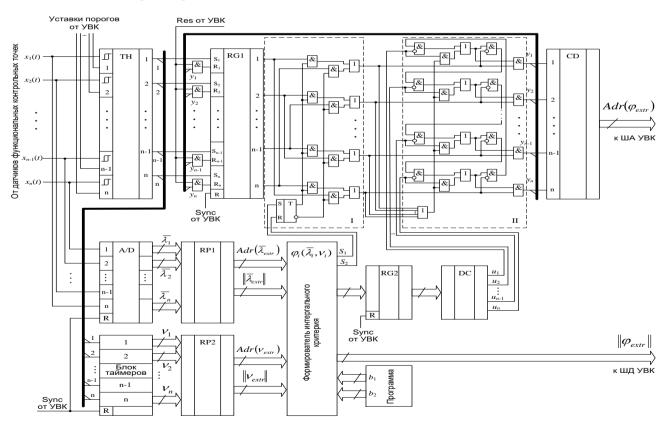

Рис. 2. Функциональная схема контроллера внешних прерываний

Обобщенная функциональная схема КВП с динамически изменяемым приоритетом обслуживания по уровневым и темпоральным признакам представлена на рис. 2. КВП содержит следующие основные функциональные узлы.

- 1) Блок пороговых элементов TH по числу контролируемых параметров n с априорными уставками допусков контролируемых параметров.

- 2) Регистр RG1 фиксации вектора состояния параметров датчиков ФКТ  $\{x_1(t), x_2(t), ..., x_i(t), ..., x_n(t)\}$ .

- 3) Логический блок I, содержащий элементы «И», «ИЛИ» и триггер T для управления формированием вариационного ряда приоритета.

- 4) Логический блок II, содержащий кольцевую структуру элементов «И», «ИЛИ».

- 5) Кодер адреса CD для формирования адреса наиболее приоритетного сигнала параметра из множества  $\{x_1(t), x_2(t), ..., x_i(t), ..., x_n(t)\}$ .

- 6) Блок аналого-цифровых преобразователей A/D (по числу контролируемых параметров n).

- 7) Блок таймеров для фиксации времени ожидания (запаздывания) обработки сигнала параметра (по числу контролируемых параметров n).

- 8) Порядково-логический процессор (реляторный процессор) RP1 для нахождения адреса и значения параметра с наибольшим отклонением от границы допусковой области.

- 9) Порядково-логический процессор (реляторный процессор) RP2 для определения адреса параметра с наибольшим временем ожидания и значения его задержки.

- 10) Формирователь интегрального критерия значимости находящихся в очереди на обслуживание параметров, вырабатывающий три сигнала: вектор  $(S_1, S_2)$ , управляющий который задает направление коммутации; vправляющий вектор  $(u_1, ..., u_n)$ , который выбирает наиболее эффективную обслуживания «лейзи-цепочку» для значение текущего приоритетного интегрального критерия значимости. Формирователь интегрального представляет собой стандартный микропроцессор, алгоритм работы которого задается программой, учитывающей априорные весовые коэффициенты значимости уровневого темпорального  $b_2$  показателей.

- 11) Регистр RG2 для фиксации адреса наиболее приоритетного операнда.

- 12) Декодер DC для преобразования двоичного кода адреса В унитарный управляющий вектор, указывающий номер канала c наибольшим приоритетом, определенным ПО значению интегрального критерия значимости.

- 13) Кодер CD, вырабатывающий адрес  $Adr(\varphi_{extr})$  приоритетного по интегральному критерию операнда в текущий момент времени.

- 14) Выход КВП, соединяемый с шиной адреса УВК, на котором формируется адрес текущего приоритетного интегрального критерия значимости  $Adr(\varphi_{ext})$ .

- 15) Выход КВП, соединяемый с шиной данных УВК, на котором формируется значение текущего приоритетного интегрального критерия значимости  $\|\varphi_{extr}\|$ , выработанное формирователем этого критерия.

Начало работы КВП синхронизируется сигналом Sync от УВК, который обнуляет элементы памяти КВП.

Текущие значения сигналов с датчиков ФКТ  $x_1(t), x_2(t), ..., x_i(t), ..., x_n(t)$  поступают на блок пороговых элементов ТН. Каждый пороговый элемент настроен на определенный уровень допусковой области траектории аналогового параметра  $x_i(t)$ ,  $i=\overline{1,n}$ . Выходы параметров за пределы допусковой зоны отображаются единичными сигналами.

Текущее состояние контролируемого объекта отображается на выходе ТН кодовым вектором с рядом единичных элементов, который фиксируется регистром RG1.

Выбросы значений параметров за пределы априорно заданных от УВК уставок пороговых уровней отображаются на соответствующих разрядных выходах регистра RG1 единичными сигналами:

$$\begin{cases} x_i(t) \ge u_{inop} \equiv 1_i; \\ x_i(t) < u_{inop} \equiv 0_i. \end{cases}$$

Одновременно посредством блока A/D осуществляется формирование цифровых значений параметров  $x_i(t)$ ,  $i=\overline{1,n}$  в виде матрицы (6), которые фиксируются регистрами порядково-логического процессора RP1 (см. рис. 1). Этот ПЛП реализует алгоритм раскрытия логического определителя (5), (6), результатом работы которого является адрес и значение максимального операнда в соответствии с (8), (9).

Параллельно с этим таймерами формируется время ожидания процессором обслуживания для всех параметров с единичной координатой вектора состояния объекта контроля.

Начиная со второго шага определения наиболее приоритетного параметра, т.е. после прихода сигнала Res от УВК, раскрытием логического определителя, аналогичного (5), (6), формируется адрес параметра с наибольшим временем ожидания и величина этого запаздывания в соответствии с (12), (13).

В формирователе интегрального критерия по принципу (15) с использованием весовых

коэффициентов значимости уровневого отклонения и времени запаздывания вырабатывается три сигнала управления.

Первый сигнал подается на тригтер, который формирует вариационный ряд приоритета посредством линейки логических элементов I:

$$S = 1, R = 0 \Rightarrow S_1 : 1 \succ 2 \succ \dots \succ i \succ \dots \succ (n-1) \succ n,$$

$$S = 0, R = 1 \Rightarrow S_2 : n \succ (n-1) \succ \dots \succ i \succ \dots \succ 2 \succ 1.$$

Выходы элементов «ИЛИ» блока I поставляют единичные компоненты вектора состояния БРЭО на логическую структуру II, представляющую собой «дейзи-кольцо».

Второй управляющий сигнал подается на декодер DC, где преобразуется в унитарный код  $(u_1,u_2,...,u_i,...,u_n)$  с единственной единичной компонентой, соответствующей приоритетному параметру из  $x_i(t)$ ,  $i=\overline{1,n}$ . Этот сигнал поступает на вход логического блока II, где выбирается наиболее эффективная для обслуживания параметра «дейзицепочка» из «дейзи-кольца» с диапазоном 2n! вариантов.

Кодер адреса CD на основе выходного сигнала логического блока II  $\{y_1(t), y_2(t), ..., y_i(t), ..., y_n(t)\}$  формирует адрес наиболее приоритетного параметра.

Одновременно формирователем интегрального критерия вырабатывается величина текущего приоритетного параметра с учетом уровневого и темпорального показателей потока диагностических данных.

## VI. ЗАКЛЮЧЕНИЕ

В работе предложен и разработан функциональноориентированный КВП с динамически изменяемым приоритетом, реализующий алгоритм упорядочения массива поступающих в УВК заявок, который:

- 1) реализует адаптивно-детерминированную процедуру обработки поступающих в УВК заявок; адаптивность состоит в учете динамически изменяющихся приоритетов заявок; детерминизм заключается в упорядоченности обработки заявок по убыванию или возрастанию;

- 2) уменьшает относительно традиционных методов избыточность хранимой в УВК информации, поскольку массивы данных находятся в упорядоченном виде;

- 3) обладает высокой разрешающей способностью и быстродействием благодаря выбору текущего максимального операнда в массиве из n элементов за один такт работы, в отличие от традиционных алгоритмов, выполняющих  $C_n^2 = \frac{n(n-1)}{2}$  операций; диагностическая система БРЭО насчитывает не менее ста ФКТ, следовательно, выигрыш по скорости выбора экстремального параметра можно оценить в 5 000 раз;

4) информационная мощность КВП может быть оценена значением 2n! (коэффициент 2 обусловлен одновременным определением максимального и минимального элементов матрицы), что значительно больше этого показателя у традиционных контроллеров прерывания; так, при прерываниях по «дейзи-цепочке» информационная мощность равна числу входов КВП и составляет величину n.

#### Литература

- [1] Абрамов Н.С., Заднепровский В.Ф., Талалаев А.А., Фраленко В.П., Хачумов М.В. Перспективная система состояния мониторинга прогнозирования И космического аппарата на основе анализа интегрированной информации // Авиакосмическое приборостроение. 2015. № 6. С. 33-48.

- [2] Авдеев В.А. Организация ЭВМ и периферия с демонмтрацией имитационных моделей. М.: ДМК Пресс, 2014. 708 с.

- Inpecc, 2014. 708 c.

[3] Agrawala A., Tripathi S., Ricard G. Adaptive routing using a virtual waiting time technique // IEEE Trans. Software Eng. 1982. Vol. SE-8. No. 1, P. 76-82.

- Eng. 1982. Vol. SE-8. No. 1. P. 76-82.

[4] Borgelt C. Prototype-based classification and clustering habilitation thesis. Magdeburg: Otto-von-Guericke-Universität Magdeburg. 2009. 350 p.

- [5] Russel Stuart J., Norvig Peter, Artificial intelligence: A modern approach (3rd Ed.). New Jersey: Publishing House "Prentice Halls. 2010, 1152 p.

- «Prentice Hall». 2010. 1152 p.

[6] Shelton C., Koopman P., Nace W. A framework for scalable analysis and design of system-wide graceful degradation in distributed embedded systems // Eighth IEEE International Workshop on Object-Oriented Real-Time Dependable Systems (WORDS 2003): Guadelajare (Mexico), Jan. 2003, Guadelajare. 2003. P. 8.

- [7] Edvin E. Kligman, Microprocessor systems design // Prentice-Hall, Inc. Englewood Cliffs, New Jersy, 1987.

- [8] George A. Smith, Computer interfacing // B.A. (Hons), C. Eng. M.I.E.E. Newnes. Oxford, Boston. 1999.

- [9] Фритч В. Применение микропроцессоров в системах управления. М.: Мир, 1984. 464 с.

- [10] Авдеев В.А., Гузик В.Ф. Компьютеры: шины, контроллеры, периферийные устройства: Учеб. пособие. М.: Радио и связь, 2001. 480 с.

- [11] Микропроцессорное управление технологическим оборудованием микроэлектроники / Под. ред. А.А. Сазонова. М.: Радио и связь, 1988. 264 с.

- [12] Lesh F. Software development aids in distributed microprocessor system // Proc. 1977 Jnt. Sump. MINI and MIKRO Comput. MINI77, Monthreal. P. 88-90.

- [13] Longden L. The Designing a single board computers for space using the most advanced processor and mitigation technologies // Proceedings of the European Space Components Conference / ESA, Toulouse, France. 2002. P. 313-316.

- [14] Hahn M., Elsner G. Advanced integrated control and data systems for constellation satellites // MAPLD International Conference. NASA Office of Logic Design, Washington, USA. 2002. P. 217-225.

- [15] Левин В.И. Структурно-логические методы исследования сложных систем с применением ЭВМ. М.: Наука, 1987. 304 с.

- [16] Самойленко А.П., Панычев А.И., Панычев С.А. Синтез системы автоматического контроля работоспособности бортового радиоэлектронного комплекса // Известия ЮФУ. Технические науки. 2015. № 11 (172). С. 166-177.

- [17] Самойленко А.П., Панычев А.И., Панычев С.А. Метод оценки надежности комплекса радиоэлектронного оборудования летательного аппарата // Известия ЮФУ. Технические науки. 2015. № 3 (164). С. 102-110.

- [18] Устройство для поиска экстремальных значений // Авт. свид. № 525083. 1976. Бюл. № 30 G 06 F 7/06 / Самойленко А.П., Скубилин М.Д.

# Synthesis of external interrupt controller with dynamic priority change

A.P. Samoilenko, A.I. Panychev, S.A. Panychev Southern Federal University, ruu2011@mail.ru

Keywords — array elements ordering, ordinal logic, infinite-valued logic, logical determinant, integral criterion, avionics.

#### **ABSTRACT**

Controlled parameters of avionics are a random function of the current state of system elements as a diagnostic object. Urgent is the development of effective method of dynamic control of information flow and organizing data according to level and temporal priorities, as well as synthesis of the corresponding controller external interrupts.

A functional-oriented external interrupt controller with priority change, operating according to the algorithm of dynamic ordering of the array of incoming requests according to their priorities, is presented. The algorithm is based on the use of ordinal logic mathematical tool and application of integrated criterion on the basis of a priori weighting factors. The algorithm provides for simultaneous comparison of priority needs and allocation of the element with the highest priority; in case of equal parameters for two or more elements selection is carried out based on additional features; further, priorities of still unserved requests are compared.

Search for extreme element in the array is described by function of infinite valued logic. Disclosure Procedure logical determinant of large dimension quasimatrices is adapted to the hardware implementation. The algorithm is characterized by uniformity and parallelism; high speed, determined by the nature of transients in the elements; ability to work with arrays of direct and inverted codes, which reduces lag.

Controller effectively ensure the absence of redundancy, high resolution and performance due to the simultaneous comparison of incoming request priorities.

## REFERENCES

- [1] Abramov N.S., Zadneprovskii V.F., Talalaev A.A., Fralenko V.P., Khachumov M.V. The perspective system for monitoring and forecasting the state of the spacecraft on the basis of analysis of integrated information. Aviakosmicheskoe priborostroenie, 2015, no. 6, pp.33-48 (in Russian).

- [2] Avdeev V.A. Organizatsiya EVM i periferiya s demonmtratsiei imitatsionnykh modelei Organization of computers and peripherals with a demonstration of simulation models, Moscow, DMK Press Publ., 2014, 708 p (in Russian).

- [3] Agrawala A., Tripathi S., Ricard G. Adaptive routing using a virtual waiting time technique. IEEE Trans. Software Eng., 1982, vol. SE-8, no. 1, pp. 76-82.

- [4] Borgelt C. Prototype-based classification and clustering habilitation thesis. Magdeburg: Otto-von-Guericke-Universität Magdeburg, 2009, 350 p.

- [5] Russel Stuart J., Norvig Peter Artificial intelligence: A Modern Approach (3rd Ed.). New Jersey: Publishing House «Prentice Hall», 2010, 1152 p.

- «Prentice Hall», 2010, 1152 p.

[6] Shelton C., Koopman P., Nace W. A framework for scalable analysis and design of system-wide graceful degradation in distributed embedded systems. Eighth IEEE Int. Workshop on Object-Oriented Real-Time Dependable Systems (WORDS 2003): Guadelajare (Mexico), 2003, p. 8.

- [7] Edvin E. Kligman Microprocessor systems design, Prentice-Hall, Inc. Englewood Cliffs, New Jersy, 1987.

- [8] George A. Smith, Computer Interfacing. B.A. (Hons), C. Eng. M.I.E.E. Newnes. Oxford, Boston, 1999.

- [9] Fritch V. Primenenie mikroprotsessorov v sistemakh upravleniya - The use of microprocessors in control systems, Moscow, Mir Publ., 1984, 464 p (in Russian).

- [10] Avdeev V.A., Guzik V.F. Komp'yutery: shiny, kontrollery, periferiinye ustroistva - Computers: bus controllers, peripherals, Moscow, Radio i svyaz' Publ., 2001, 480 p (in Russian).

- [11] Mikroprotsessornoe upravlenie tekhnologicheskim oborudovaniem mikroelektroniki - Microprocessor control technology microelectronics equipment, Pod. red. A.A. Sazonova, Moscow, Radio i svyaz' Publ., 1988, 264 p (in Russian).

- [12] Lesh F. Software development aids in distributed microprocessor system, Proc. 1977 Jnt. Sump. MINI and MIKRO Comput. MINI77, Monthreal, pp. 88-90.

- [13] Longden L. The designing a single board computers for space using the most advanced processor and mitigation technologies, Proc. of the European Space Components Conference, European Space Agancy, Toulouse, France, 2002, pp. 313-316.

- 2002, pp. 313-316.

[14] Hahn M., Elsner G. Advanced integrated control and data systems for constellation satellites. MAPLD International Conference, NASA Office of Logic Design, Washington, USA, 2002, pp. 217-225.

[15] Levin V.I. Strukturno-logicheskie metody issledovaniya slozhnykh sistem s primeneniem EVM Structural and

- [15] Levin V.I. Strukturno-logicheskie metody issledovaniya slozhnykh sistem s primeneniem EVM - Structural and logical methods for complex systems research with the use of computers, Moscow, Nauka Publ., 1987, 304 p (in Russian).

- [16] Samoilenko A.P., Panychev A.I., Panychev S.A. Synthesis of the automatic control of the operational avionics complex. Izvestiya YuFU. Tekhnicheskie nauki, 2015, no. 11 (172), pp. 166-177 (in Russian).

[17] Samoilenko A.P., Panychev A.I., Panychev S.A. The

- [17] Samollenko A.P., Panychev A.I., Panychev S.A. The method of evaluating the reliability of complex electronic equipment of the aircraft. Izvestiya YuFU. Tekhnicheskie nauki, 2015, no. 3 (164), pp. 102-110 (in Russian).

- [18] Samoilenko A.P., Skubilin M.D. Ustroistvo dlya poiska ekstremal'nykh znachenii - Device for searching extreme values. Patent USSR, no. 525083, 1976 (in Russian)