# Логический элемент сравнения для 65-нм КМОП-селекторов ассоциативных запоминающих устройств

В.Я. Стенин<sup>1,2</sup>, А.В. Антонюк<sup>1,2</sup>

<sup>1</sup>Национальный исследовательский ядерный университет "МИФИ"

<sup>2</sup>НИИ системных исследований РАН

vystenin@mephi.ru; antonyukartem@gmail.com

Аннотация — Предлагается вариант логического элемента сравнения для КМОП-селекторов ассоциативных запоминающих устройств, созданный на основе ячеек памяти DICE с разделенными на две группы транзисторами, разнесенными на кристалле. Элемент сравнения с повышенной помехоустойчивостью предназначен для ассоциативных запоминающих устройств по проектным нормам для 65-нм КМОП-технологии на объемном кремнии..

Ключевые слова — логический элемент, ячейка памяти, запоминающее устройство, топология, одиночная ядерная частица, помехоустойчивость

### I. Введение

Основой элементов сравнения для блоков регистров-селекторов ассоциативных запоминающих устройств (или translation lookaside buffer – TLB) являются комбинационные логические элементы "Исключительное ИЛИ" и элементы памяти, в качестве которых обычно используются КМОП 6транзисторные ячейки памяти [1]. При уменьшении проектно-технологических норм до КМОП 65 нм и ниже снизилась надежность работы ассоциативных запоминающих устройств (АЗУ), выполненных по таким проектным нормам, используемых в условиях воздействия одиночных ядерных частиц.

Простая замена 6-транзисторной ячейки памяти на ячейку памяти с повышенной устойчивостью к одиночным эффектам, которой является ячейка памяти DICE (Dual Interlocked Storage Cell) [2], не решает устойчивости проблему повышения элементов сравнения для КМОП-селекторов. Характерное для наноразмерных проектных норм снижение расстояний между чувствительными парами узлов в традиционном варианте ячеек DICE при масштабировании топологии ячейки DICE сопровождается потерей преимуществ по устойчивости относительно транзисторных ячеек [3], [4]. Экспериментальные исследования [5] новых 65-нм КМОП-ячеек памяти STG DICE [6], [7] с транзисторами, разделенными на две группы, показали их высокую устойчивость по сравнению с 6-транзисторными ячейками памяти.

Цель данной работы – дать анализ логического элемента сравнения для КМОП-селекторов

ассоциативных запоминающих устройств на основе ячеек памяти STG DICE, которые обеспечивают потенциально повышенную помехоустойчивость логического элемента сравнения.

## II. НОВЫЙ ВАРИАНТ ЛОГИЧЕСКОГО ЭЛЕМЕНТА СРАВНЕНИЯ НА ОСНОВЕ ЯЧЕЙКИ ПАМЯТИ STG DICE

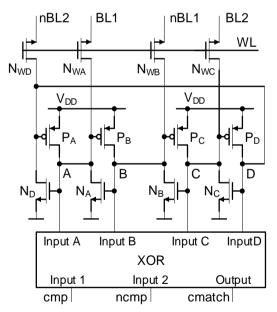

На рис. 1 приведена схема логического элемента сравнения для КМОП-селекторов ассоциативных запоминающих устройств на основе триггера DICE, названного как Spaced Transistor Groups DICE (STG DICE). Триггер STG DICE изображен состоящим из двух групп транзисторов, каждая из которых имеет последовательно расположенные пары открытых *N*- и *P*МОП-транзисторов и закрытых *N*- и *P*МОП-транзисторов [6], [7]. Комбинационная логическая часть элемента на рис. 1 выполнена на элементе "Исключительное ИЛИ", обозначенном на рис. 1 как XOR.

Рис. 1. Схема логического элемента сравнения на основе триггера STG DICE с разделенными на две группы транзисторами и комбинационного элемента XOR

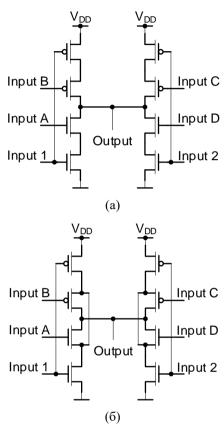

На рис. 2 приведены два варианта схемы логического элемента "Исключительное ИЛИ" (ХОR). Первый вариант на рис. 2а выполнен на основе двух инверторов с третьим состоянием; второй вариант на рис. 2б — на основе традиционных инверторов и проходных ключей на парах *N*- и *P*МОП-транзисторов. Схема на рис. 2б приведена в нетрадиционном изображении, чтобы подчеркнуть максимальное схемное сходство обоих вариантов, где внутренние пары *N*- и *P*МОП-транзисторов каждой из симметричных половин элемента ХОR выполняют блокирование передачи сигналов с входов Іприt 1 или Іприt 2 на выход.

Рис. 2. Схемы вариантов логического элемента "Исключительное ИЛИ" (XOR): (а) на основе двух инверторов с третьим состоянием; (б) на основе традиционных инверторов и проходных ключей на парах N- и PMOП транзисторов

Логический элемент сравнения работает в одном из двух режимов. Во-первых, запись одной переменной в триггер STG DICE и, во-вторых, сравнение с этой переменной (для селекции данных) данных из последовательности, поступающей на нормальный и инверсный входы логического элемента XOR Input 1 и Input 2 с первой и второй Input 2 входных шин элемента XOR стр и пстр.

Запись данных в STG DICE осуществляется в четыре узла триггера A, B, C, D через проходные ключи  $N_{WA}$ ,  $N_{WB}$ ,  $N_{WC}$ ,  $N_{WD}$ . При записи данных на битовые линии подают записываемые данные в дифференциальной форме, а именно, на линии BL1,

BL2 в нормальном виде, а на линии nBL1, nBL2 в инверсном. Установка активного уровня на линию выборки WL открывает проходные ключи, записывая данные (первую из двух переменных) на четыре узла триггера A, B, C, D. Логический уровень записанной переменной в триггер соответствует уровням на узлах A и C двух групп транзисторов.

В режиме сравнения (селекции) на входные шины элемента подаются синхронно cmp. ncmp последовательности сигналов в нормальном (входная шина стр) и инверсном (входная шина пстр) виде, логические уровни которых сравниваются логическими уровнями данных, записанных в четыре узла двух групп транзисторов триггера, и, в итоге, на выходную шину cmatch элемента сравнения с выхода (Output) элемента XOR поступает последовательность логических сигналов, являющихся результатом сравнения. Длительность интервала времени сравнения (селекции) данных определяется длительностью заданной последовательности данных (сигналов), поступающих на входные шины стр, пстр элемента. Соответственно, в интервале времени сравнения (селекции) данных недопустима потеря данных, хранимых триггером, то есть сбой его логического состояния из-за воздействия одиночных ядерных частиц.

Логический элемент сравнения XOR описывается логической функцией следующего вида:

$$Y_{OUT} = X_{IN1} \cdot X_{BD} + X_{IN2} \cdot X_{AC},$$

где  $X_{AC}=X_A=X_C$  — логические уровни на узлах A и C, имеющие одинаковые нормальные значения в стационарном состоянии триггера STG DICE;  $X_{BD}=X_B=X_D$  — логические уровни на узлах B и D, имеющие одинаковые инверсные значения в стационарном состоянии триггера;  $X_{IN1}$  — нормальный (прямой) логический уровень сигнала на входе Input 1 элемента;  $X_{IN2}=nX_{IN1}$  — инверсный логический уровень сигнала на входе Input 2 элемента;  $Y_{OUT}$  - логический уровень на выходе элемента XOR.

## III. ХАРАКТЕРИСТИКИ ТРИГГЕРА STG DICE В НЕСТАЦИОНАРНОМ СОСТОЯНИИ

В стационарном состоянии триггера DICE логические уровни внутренних узлов (А и С) обеих групп определяют логическое состояние триггера. Воздействие частицы лишь на одну из групп триггера STG DICE не вызывает сбоя, а переводит триггер во временное нестационарное состояние вследствие переходного процесса (Single Event Transient – SET).

Сбой (Single Event Upset – SEU) триггера STG DICE зависит от продолжительности сбора заряда первой группой  $t_{COLL.GR1}$  и одновременно от задержки переключения второй группы  $t_{DEL.SW.GR2}$  триггера STG DICE [8]. Полагается, что одна из групп (первая) ближе к треку частицы и сразу подвергается воздействию заряда, что приводит к изменению логического состояния ее узлов, а на вторую группу заряд собирается в виде импульса тока, образованного

диффузией заряда с трека. Значения заряда, собранного первой группой, как и у инвертора [9], [10], не более 1 пКл, а время его сбора  $t_{\rm COLL.GR1}$  не превышает 0.4-1 нс, что определяет длительность эффекта воздействия, когда возможен сбой.

На рис. 3 приведен пример развития переходного процесса в триггере при воздействии частицы. Исходное состояние узлов триггера ABCD = 1010; транзисторы первой группы  $\hat{N_A}$  и  $P_B$  заперты, заперты и транзисторы  $N_C$ ,  $P_D$  второй группы. Первое воздействие оказывается на запертый транзистор РВ первой группы (узел В сразу повышает потенциал до напряжения питания  $V_{DD}$ , транзистор  $N_A$  открывается и потенциал узла А начинает снижаться). Интервал времени 250 пс на рис. 3 соответствует случаю воздействия только на одну группу. дополнительного воздействия на вторую группу нет, то после окончания воздействия на первую группу триггер возвращается в исходное состояние [8].

Если воздействие частицы затрагивает и вторую группу транзисторов, а в рассматриваемом примере это происходит через время задержки  $t_{DEL,C} = 250$  пс при дополнительном воздействии на запертый транзистор  $N_{\rm C}$  второй группы, то это вызывает снижение потенциала узла С и через 0.15 нс открывает транзистор стимулируя возникновение  $P_D$ положительной обратной связи через транзистор РА и переключение состояния ячейки DICE. Если воздействие заряда с трека частицы прекратится до окончания интервала t<sub>DEL.SW.GR2.THR</sub>, то сбоя не будет.

Рис. 3. Зависимости напряжений на узлах ячейки DICE ( $W_P=W_N=120$  нм) во времени в нестационарном состоянии  $P_AN_B1001$  с дополнительным воздействием на транзистор  $N_B$  второй группы импульсом тока с постоянными  $\tau_{\rm CII}=0.1$  нс,  $\tau_H=\tau_{\rm CII}/9$ , амплитуда импульса  $I_M=2.5$  мкА; b=0.3-0.4

Пороговое значение задержки переключения второй группы определяется выражением [8]:

$t_{DEL.SW.GR2.THR} = 0.01(100 \ \mbox{mkA/I}_M)^{0.25(3+lg2)}$  (нс),

где  $I_{M}$  – амплитуда импульса тока, образованного диффундирующим от трека частицы зарядом (в мкА).

Это выражение справедливо для триггера DICE с транзисторами минимальной ширины. Если время сбора заряда первой группой  $t_{COLL.GR1}$  меньше порогового значения задержки переключения второй группы  $t_{COLL.GR1} < t_{DEL.SW.GR2.THR}$ , то сбой невозможен, а при  $t_{COLL.GR1} \ge t_{DEL.SW.GR2.THR}$  сбой вероятен. Вероятность сбоя падает с увеличением расстояния между группами, поскольку существенно уменьшается доля частиц с большими линейными потерями энергии, имеющих треки в этом весьма ограниченном направлении пространства.

# IV. ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ С РАЗДЕЛЕННЫМИ НА ДВА БЛОКА ТРАНЗИСТОРАМИ

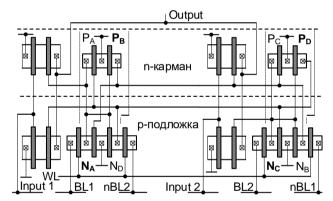

На рис. 4 приведен эскиз топологии одного логического элемента сравнения для селектора ассоциативного ЗУ, выполненного в виде двух одинаковых блоков транзисторов. Один базовый блок содержит одну группу транзисторов триггера STG DICE, включая соответствующие проходные ключи записи данных, а также транзисторы инвертора с третьим состоянием (половины логического элемента XOR). Две группы транзисторов триггера STG DICE топологически соединены двумя проводами, что снижает издержки по площади при разнесении базовых блоков на кристалле микросхемы. В логическом состоянии АВСО = 1010 транзисторная пара N<sub>A</sub>P<sub>B</sub> левой группы STG DICE триггера (см. рис. 1 и 4) находится в закрытом состоянии, а пара  $N_D P_A - B$ открытом. В правой группе в закрытом состоянии пара  $N_C P_D$ , а в открытом –  $N_B P_C$ .

Рис. 4. Эскиз топологии элемента сравнения на основе транзисторов логического элемента XOR и триггера STG DICE, разделенных на два базовых блока транзисторов

Жирным шрифтом на рис. 4 отмечены транзисторы триггера в состоянии узлов триггера 1010, расстояния между обратно смещенными *pn* переходами стокподложка которых определяют его помехоустойчивость. В другом состоянии расстояния будут те же, но между другими парами закрытых транзисторов, отмеченных обычным шрифтом. На рис. 4 вариант схемы XOR, представленный на рис. 26, реализуется дополнительной проводной связью диффузионных областей между затворами *N*- и *P*МОП транзисторов у обоих инверторов с третьим состоянием. Базовые блоки транзисторов в топологии

регистра-селектора образуют последовательность, в которой два базовых блока конкретного логического элемента сравнения разделены одном или несколькими транзисторов других элементов, позволяет формировать элементы сравнения с большими расстояниями между их чувствительными узлами.

## V. Параметры 65-нм элемента сравнения

В табл. 1 приведены параметры логического элемента сравнения, где  $H_B$ ,  $W_B$  и  $N_{TR}$  — высота, ширина одного базового блока и количество транзисторов в нем; Іоит. LEAK - ток утечки на выходе инвертора с третьим состоянием;  $t_{DEL.P}$  — задержка распространения сигнала элемента XOR при емкости нагрузки 3фФ. Размеры транзисторов в XOR-элементе: ширина *N*МОП и *P*МОП транзисторов  $W_N = 300$  нм и  $W_P = 360 \text{ HM}.$

Таблица 1 Параметры 65-нм КМОП базового блока логического элемента сравнения

| Параметры | $N_{TR}$ | $W_{B}$ , | $H_B$ , | I <sub>OUT.LEAK</sub> , | t <sub>DEL.P</sub> , |

|-----------|----------|-----------|---------|-------------------------|----------------------|

|           |          | MKM       | MKM     | пА                      | пс                   |

| Значения  | 10       | 2.4       | 2.45    | 30-33                   | 20-25                |

В табл. 2 приведены расстояния между парами взаимно чувствительных узлов логических элементов сравнения для КМОП 65-нм элемента в составе фрагмента регистра из четырех базовых блоков.

Таблица 2

| Расстояния между чувствительными парами  |

|------------------------------------------|

| транзисторов в одном логическом элементе |

| Пары узлов | $N_A - N_C$ | $P_B-P_D$ | $P_B-N_C$ | $N_A - P_D$ |

|------------|-------------|-----------|-----------|-------------|

| Расстояния | 4.55        | 4.55      | 4.15      | 5.15        |

# VI. ЗАКЛЮЧЕНИЕ

Рассмотрен вариант логического элемента сравнения для селекторов ассоциативных запоминающих устройств с проектной нормой объемный КМОП 65 нм на основе сбоеустойчивого триггера STG DICE с разделенными на две группы транзисторами. Топологически логический элемент сравнения выполнен в виде двух одинаковых блоков транзисторов, которые В составе регистров устройства ассоциативного запоминающего чередуются подобными блоками смежных логических элементов, что позволило увеличить расстояния между взаимно чувствительными к сбоям узлами логического элемента при минимальных издержках на площадь межсоединений, характерных для триггеров STG DICE. Это делает перспективным данное техническое решение для использования в микропроцессорных системах c повышенной

устойчивостью к воздействиям тяжелых заряженных частиц.

Работа выполнена при полдержке Российского фонда фундаментальных исследований, проект № 14-29-09284.

#### ЛИТЕРАТУРА

- [1] Patterson D.A.; Hennessy J.L. Computer organization and design. Hardware/Software interface. Fourth edition. Burlington, MA 01803, USA: Morgan Kaufmann Publishers, 2009. p. 503.

- [2] Calin T. Nicolaidis M., Velazco R. Upset hardened memory design for submicron CMOS technology // IEEE Transactions on Nuclear Science. 1996. V. 43. № 6. P. 2874-2878.

- Seifert N.P., Ambrose V., Gill B., Shi Q., Allmon R., Recchia C., Mukherjee S., Nassif N., Krause J., Pickholtz J., Balasubramanian A. On the radiation-induced soft error performance of hardened sequential elements in advanced bulk CMOS technologies // Proceedings of IEEE International Reliability Physics Symposium. 2010. P.

- [4] Loveless T.D., Jagannathan S., Reece T., Chetia J., Bhuva B.L., McCurdy M.W., Massengill L.W., Wen S.-J., Wong R., Rennie D. Neutron- and proton-induced single event upsets for D- and DICE-flip/flop designs at a 40 nm technology node // IEEE Transactions on Nuclear Science. 2011. V. 58. № 3. P. 1008-1014.

- Катунин Ю.В., Савченков Д.В., Стенин В.Я., Степанов П.В. Исследование 65-нм КМОП однопортовых и многопортовых блоков статических ОЗУ на ячейках памяти DICE к воздействию импульсов лазерного излучения // Вопросы атомной науки и техники. Серия: Физика радиационного воздействия на радиоэлектронную аппаратуру. 2015. Вып. 3. С. 1-8.

- [6] Стенин В.Я., Катунин Ю.В., Степанов Особенности проектирования DICE элементов 65-нм КМОП статических запоминающих устройств с учетом эффекта кратного воздействия отдельных ядерных частиц // Вестник НИЯУ МИФИ. 2013. Т. 2. № 3. С. 363-370.

- [7] Стенин В.Я., Катунин Ю.В., Степанов П.В. Ячейка памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ // Патент РФ на изобретение № 2554849. Бюлл. № 18. Опубл. 27.06.2015.

- [8] Stenin V.Ya. Simulation of the characteristics of the DICE 28-nm CMOS cells in unsteady states caused by the effect of single nuclear particles // Russian Microelectronics. 2015. V. 44. № 5. P. 324–334.

- [9] Ferlet-Cavrois V., Paillet P., Gaillardin M., Lambert D., Baggio J., Schwank R., Vizkelethy G., Shaneyfelt M.R., Hirose K., Blackmore E.W., Faynot O., Jahan C., Tosti L. Statistical analysis of the charge collected in SOI and bulk devices under heavy ion and proton irradiation implications for digital SETs // IEEE Transactions on Nuclear Science. 2006. V. 53. № 6. P. 3242-3252.

- [10] Gadlage M. J., Ahlbin J. R., Narasimham B., Bhuva B. L., L. W. Massengill L. W., Reed R. A., Schrimpf R. D., and Vizkelethy G. Scaling trends in SET pulse widths in sub-100 nm bulk CMOS processes // IEEE Transactions on Nuclear Science. 2010. V. 57. № 6. P. 3336-3341.

# The logical elements of comparison for the 65 nm CMOS selectors of associative memory

V.Ya. Stenin<sup>1, 2</sup>; A.V. Antonyuk<sup>1, 2</sup>

Keywords — logical element, memory cell, associative memory, topology layout, single nuclear particle, noise immunity

### ABSTRACT

The basic comparison elements for registers-selectors of associative memory (or translation lookaside buffer – TLB) are combinational logic elements "Exclusive OR" and the memory cell, which typically is CMOS 6-transistor cell [1]. Decreasing the design rules to the CMOS 65-nm and below has decreased the reliability of the associative memory developed according to such design rules and used in conditions of exposure to single nuclear particles.

Simple replacement of the 6-transistor cell in the memory cell with high resistance to single effects, which is a memory cell DICE (Dual Interlocked Storage Cell) [2], does not solve the problem of increasing the hardness of comparison elements for CMOS registers-selectors of associative memory units. Characteristic of nano-scale design rules, the reduction of distances between pairs of sensitive nodes in the traditional version of the DICE cells when scaling the layout of their DICE cell is accompanied by loss of its advantages in terms of hardness relative to a 6-transistor cell [3], [4]. Experimental studies [5] of the new 65-nm CMOS memory cells STG DICE [6], [7] with the transistors spaced into two groups showed their high noise resistance compared with 6-transistor memory cells.

The aim of this paper is to present the analysis of the logic comparison element compared to CMOS selectors associative memory units based on STG DICE memory cells that provide potentially high noise immunity of this logic comparison gate.

The element of comparison to CMOS selectors was created using Spaced Transistor Groups DICE (STG DICE) trigger. STG DICE trigger consists of two groups of transistors each group has the opened and closed pairs of N- and PMOS-transistors [6], [7]. The combinational logic of the comparison element is the logical element "Exclusive OR", denoted as XOR.

We consider two variants of the logical element "Exclusive OR" (XOR) circuit. The first option is implemented on two tristate inverters; the second on traditional inverters and pass gates on pairs of N - and PMOS-transistors.

Writing data to STG DICE is carried out in four nodes of the trigger A, B, C, D through the pass gates. When you write the data to the trigger the bit line gets the data written in the differential form - in normal form and in inverted. The active level on the sampling line opens the gates recording data (first two variables) on the four nodes of the trigger A, B, C, D.

In compare mode (selection) of data on two intputs serves a sequences of signals in normal and inverse form. On the output of the XOR-element we get the result of a comparison of the data. The logical element comparison has the function in the following form:

$$Y_{OUT} = X_{IN1} \cdot X_{BD} + X_{IN2} \cdot X_{AC},$$

$X_{AC}=X_A=X_C-logic$  values of nodes A and C that have the same normal value in the stationary state of the trigger STG DICE;  $X_{BD}=X_B=X_D-logic$  values of nodes B and D that have the inverse value in the stationary state of the trigger.  $X_{IN1}-normal$  (direct) logic level at the Input 1 of the element;  $X_{IN2}=nX_{IN1}-inverted\ logic\ level$  of the signal at the Input 2 of the element;  $Y_{OUT}$  is the logical level at the output of the XOR-element.

The impact of the particle on one of the STG DICE trigger groups does not cause a failure, and puts the trigger in a temporary unsteady state due to a transient (Single Event Transient – SET).

The fault (Single Event Upset – SEU) of the STG DICE trigger depends on the duration of charge collection on the first group and at the same time from the delay time switching on of the second group of STG DICE trigger transistors [8]. After exposure on the first group if the impact on the second group was small the trigger returns to its original state. The value of charge collected to the first group is just the same as that of the inverter [9], [10] (less, then 1 pC), and the time of its collection t<sub>COLL.GR1</sub> does not exceed 0.4–1 ns. This value determines the duration of the effect of the impact when crashing.

To protect against the latch-up during the impact of single nuclear particles we have used n+ and p+ guard rings in the form of ohmic contacts at the boundaries of the areas of P-substrate and the N-wells. Using separated ohmic contacts distributed on P-substrate has increased the rate of passing the induced charge from the bulk of semiconductor to the power buses and ground buses.

<sup>&</sup>lt;sup>1</sup> National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Russia

<sup>&</sup>lt;sup>2</sup> Scientific Research Institute of System Analysis, Russian Academy of Sciences, Moscow, Russia vystenin@mephi.ru; antonyukartem@gmail.com

The basic transistors block contains one group of the STG DICE-trigger transistors, and the tristate inverter (half part the transistors of a logic gate XOR). Two groups of transistors of the trigger-STG DICE connected by two wires. The separaton of the basic blocks on the chip reduces costs in comparison with the traditional DICE layout.

Schematics and layout of basic transistors blocks of the CMOS units were designed in CAD Schematic Cadence Virtuoso Editor and Cadence Virtuoso Layout Editor. Verification of the layout was carried out using CAD packages from Mentor Graphics: Calibre nmDRC and Calibre nmLVS.

The basic blocks in the register-selector layout form a sequence in which two basic blocks of the specific logical element are spaced by several blocks of other elements (two or four, for example). This allows forming logic comparison elements with the large distances between mutually sensitive nodes of the two such blocks of each logic comparison element. This increases the noise immunity of the logical comparison elements because significantly decreases the fraction of nuclear particles with large linear energy losses with the tracks in this very limited space of directions.

The parameters of comparison elements based on 65-nm bulk CMOS design rules are the next. The width of NMOS and PMOS-transistors channels are  $W_N=300$  nm and  $W_P=360$  nm. The height and the width of the basic block are  $H_B=2.45~\mu m,$  and  $W_B=2.4~\mu m,$  respectively; a leakage current of the output of A tristate inverter is  $I_{OUT.LEAK}=30{-}33~pA;$  the XOR propagation delay is  $t_{DEL.PROP}=20{-}25~ps$  ( $C_L=3~fF).$  Distances between pairs of the mutually sensitive logical nodes of two blocks of the comparison element for the CMOS 65-nm implementation are the next:  $L_{NA-NC}=4.55~\mu m,\, L_{PB-PD}=4.55~\mu m,\, L_{PB-NC}=4.15~\mu m,\, L_{NA-PD}=5.15~\mu m.$

The parameters of comparison elements implemented with 28-nm bulk CMOS design rules are the next. The width of NMOS and PMOS-transistors are  $W_N=200$  nm and  $W_P=240$  nm; the height and the width of the basic group are  $H_{GR}=1.4~\mu m$ , and  $W_{GR}=1.2~\mu m$ ; a leakage current on the XOR-element output is  $I_{OUT.LEAK}=15-17~pA$ ; the XOR propagation delay is  $t_{DEL.PROP}=25~ps$  ( $C_L=3~fF$ ). Distances between pairs of the mutually sensitive logical nodes of two groups of the comparison element for the CMOS 28-nm block of the eight basic groups are the next:  $L_{NA-NC}=4.65~\mu m$ ,  $L_{PB-PD}=4.65~\mu m$ ,  $L_{PB-NC}=4.45~\mu m$ ,  $L_{NA-PD}=4.95~\mu m$ .

The distances between the sensitive nodes in the comparison elements with CMOS 65-nm and 28-nm design rules are almost the same due to the corresponding spacing between the basic groups of transistors within blocks of four (CMOS 65-nm) and eight (CMOS 28-nm) groups of transistors.

It was conducted the analysis of logical elements of comparison for the 65 nm CMOS selectors of associative memory. New logical elements of comparison were designed on the STG DICE trigger with the transistors spaced in two groups on distance four micrometers and showed their high noise resistance compared with normal 6-transistors memory cells.

This work supported in part by the Russian Foundation for Basic Research under grant no. 14-29-09284.

#### REFERENCES

- Patterson D.A.; Hennessy J.L. Computer organization and design. Hardware/Software interface. Forth edition. Burlington, MA 01803, USA: Morgan Kaufmann Publishers, 2009. p. 503.

- [2] Calin T. Nicolaidis M., Velazco R. Upset hardened memory design for submicron CMOS technology // IEEE Transactions on Nuclear Science. 1996. V. 43. № 6. P. 2874–2878.

- [3] Seifert N.P., Ambrose V., Gill B., Shi Q., Allmon R., Recchia C., Mukherjee S., Nassif N., Krause J., Pickholtz J., Balasubramanian A. On the radiation-induced soft error performance of hardened sequential elements in advanced bulk CMOS technologies // Proceedings of IEEE International Reliability Physics Symposium. 2010. P. 188–197.

- [4] Loveless T.D., Jagannathan S., Reece T., Chetia J., Bhuva B.L., McCurdy M.W., Massengill L.W., Wen S.-J., Wong R., Rennie D. Neutron— and proton-induced single event upsets for D- and DICE-flip/flop designs at a 40 nm technology node // IEEE Transactions on Nuclear Science. 2011. V. 58. № 3. P. 1008–1014.

- [5] Katunin, Yu.V., Savchenkov D.V., Stenin V.Ya., Stepanov, P.V. Research of 65-nm CMOS one-port and multiport blocks of static RAM on DICE memory cells to influence of laser radiation pulses. Voprosy atomnoj nauki i tehniki. Serija: Fizika radiacionnogo vozdejstvija na radiojelektronnuju apparaturu Questions of atomic science and technics. Series: Physics of radiation effects on radio-electronic equipment, 2015, Issue 3, C. 1–8 (In Russian).

- [6] Stenin V.Ya., Katunin Yu.V., Stepanov P.V. Specific design aspects of 65-nm CMOS DICE cells subject to single-event multi-node charge collection, Vestnik of NRNU MEPhI - MEPhI Transactions, 2013, vol. 2, no. 3, pp. 363–370 (in Russian).

- [7] Stenin V.Ya., Katunin Yu.V., Stepanov P.V. The memory cell of complementary metal-oxide-semiconductor structure of the RAM, RF Patent 2554849, Byull. Izobret – Bulletin of Invention, 2015, no. 18 (in Russian).

- [8] Stenin V.Ya. Simulation of the characteristics of the DICE 28-nm CMOS cells in unsteady states caused by the effect of single nuclear particles // Russian Microelectronics. 2015. V. 44. № 5. P. 324–334.

- [9] Ferlet-Cavrois V., Paillet P., Gaillardin M., Lambert D., Baggio J., Schwank R., Vizkelethy G., Shaneyfelt M.R., Hirose K., Blackmore E.W., Faynot O., Jahan C., Tosti L. Statistical analysis of the charge collected in SOI and bulk devices under heavy ion and proton irradiation – implications for digital SETs // IEEE Transactions on Nuclear Science. 2006. V. 53. № 6. P. 3242–3252.

- [10] Gadlage M. J., Ahlbin J. R., Narasimham B., Bhuva B. L., L. W. Massengill L. W., Reed R. A., Schrimpf R. D., and Vizkelethy G. Scaling trends in SET pulse widths in sub-100 nm bulk CMOS processes // IEEE Transactions on Nuclear Science. 2010. V. 57. № 6. P. 3336–3341.