# Проектирование цифровых КМОП схем для экстремальных температур

A.O. Власов<sup>1</sup>, В.Б. Мараховский<sup>2</sup>, A.B. Сурков<sup>1</sup>

<sup>1</sup>ФГУ ФНЦ Научно-исследовательский институт системных исследований РАН, {vlaalex, surkov}@cs.niisi.ras.ru

<sup>2</sup>Санкт-Петербургский государственный политехнический университет Петра Великого, vbmarak@gmail.com

Аннотация — В статье рассматриваются вопросы проектирования цифровых схем для расширенного диапазона температур. Для исследований выбрана технология TSMC 65GP. Разработана топология трех схемы целочисленного умножения с реализаций накоплением: синхронной, самосинхронной и квазисамосинхронной. При проектировании квазисамосинхронной и самосинхронной схем использована методика схемной трансляции синхронных конвейерных схем в самосинхронные. Проведено сравнительное исследование полученных схем с помощью spiceмоделирования (Spectre), а также с использованием результатов анализа в САПР Encounter и временного моделирования с задержками. Моделирование проводилось с изменением температуры в диапазоне от -175°C до +200°C, а также напряжения питания от 200 мВ до 1.2 В.

*Ключевые слова* — экстремальные температуры, самосинхронные схемы, ГАЛП, САПР.

#### I. Введение

Большая часть цифровых схем разрабатывается для диапазона температур от -55°C до +125°C, использующегося для коммерческих, промышленных и других применений. Также существуют задачи проектирования аппаратуры для нестандартных условий эксплуатации, в том числе для температур ниже -55°C и выше +125°C. Примерами могут служить системы телеметрии, расположенные за бортом самолета [1], и высокотемпературные датчики, использующиеся в буровых установках [2]. С развитием техники растет поток получаемой с датчиков. В условиях ограниченного числа линий передач возникает необходимость в локальной обработке и сжатии данных перед отправкой. Предварительную обработку информации может осуществлять микроконтроллер, совмещенный с датчиком и передающий сжатый поток информации центральному вычислителю. Использование микроконтроллера позволяет выполнять и другие задачи, к примеру – локальное управление, требующее быстроты реакции. Таким образом, возникает необходимость проектирования цифровых схем для тех же условий эксплуатации, что и датчиков.

Для экстремальных температур применяются различные материалы, такие как SiGe, SiC [3] и другие. В диапазоне от -175°C до +200°C также работают КМОП [4], выгодно отличающиеся стоимостью изготовления, И не требующие специального производства. Основными препятствиями к использованию КМОП схем являются сложность проектирования и рост токов утечки при высокой температуре. В условиях ограниченного правило, потребления рост токов утечки, как компенсируют снижением напряжения питания. Сложность проектирования заключается в учете возможного разброса задержек в схеме для расчета на И наилучший случаи, работоспособность синхронных схем целиком и полностью зависит от диапазона изменения задержек. При этом диапазон используемых напряжения питания и температуры напрямую зависит от разброса задержек переключения логических элементов в схеме, что приводит к снижению тактовой частоты. Кроме синхронного принципа работы схем, использующего тактовый генератор, существует также асинхронный принцип работы [5], основанный на причинноследственных отношениях между событиями в схеме и использующий взаимодействия между элементами системы по типу запрос-ответ.

Самосинхронные схемы (СС) [6] являются одним из видов асинхронных и отличаются инвариантностью поведения от задержек элементов. Инвариантность к элементов гарантирует задержкам самосинхронных схем во всем диапазоне температур и напряжения питания, при котором осуществляется переключение транзисторов. Независимость задержек самосинхронных автоматов в большинстве случаев является следствием их полумодулярности, где термин полумодулярность позаимствован из теории решеток [7]. Будем говорить, что асинхронный автомат, кумулятивная диаграмма состояний [8] представляет собой полумодулярную которого алгебраическую структуру, также обладает свойством полумодулярности, следствием которой является самосинхронность [9]. Таким образом, при реализации самосинхронной схемы из библиотечных элементов необходимо контролировать полумодулярность диаграммы переходов состояний выходов этих элементов. К примеру, замена одного сложного логического элемента на два более простых означает введение новой переменной в диаграмму состояний автомата и может привести к потере свойства полумодулярности, а значит и самосинхронности.

Используют два основных проектированию самосинхронных схем в зависимости от назначения: при проектировании систем управления использует описание в виде диаграмм переходов или сетей Петри [8], а для представления конечных автоматов используют модель Хаффмана. Проектирование с помощью диаграмм переходов или сетей Петри в основном выполняют вручную. Такие известные инструменты, как Petrify и Workcraft [10], автоматизируют лишь этап логического синтеза и поэтому позволяют только частично автоматизировать проектирование. Высокая вычислительная сложность логического синтеза не позволяет этим инструментам проектировать схемы, графические спецификации более содержат 50 вершин. проектировании самосинхронных автоматов по модели применяют искусственное Хаффмана парафазного кодирования сигналов и двух фаз работы автомата. При этом комбинационную часть автомата строят с использованием принципа двухканальной перекрестной реализации [8]. Метод построения комбинационной логики автомата состоит в удвоении входных переменных, в результате чего каждая логическая функция становится монотонной. Известно, что монотонные функции свободны от функциональных состязаний на сравнимых входных наборах. Для того чтобы все наборы сделать сравнимыми, входные наборы перемежаются наборами-разделителями, с которыми сравним каждый входной набор, т.е. организуется двухфазная смена входных наборов. Для индикации моментов окончания переходных процессов каждая логическая приведенная к монотонному функция, реализуется в виде прямого и инверсного каналов, двойственных друг другу, и между этими каналами устанавливаются перекрестные связи, гарантирующие отсутствие логических состязаний. При такой реализации логических функций применяется парафазное кодирование входных наборов, выходов каждого яруса реализации и выходов логической что позволяет строить простые схемы схемы, индикации моментов окончания переходных процессов. Использование двуканальной перекрестной реализации логической схемы и самосинхронных элементов памяти позволяет создавать самосинхронные автоматы большой сложности.

Другой особенностью перекрестной реализации является возможность строить самосинхронные схемы по синхронному прототипу. Недостатками перекрестной реализации являются: увеличение площади логических элементов за счет удвоения числа элементов логики и дополнительной схемы индикации окончания переходных процессов, а также уменьшение производительности схемы, поскольку при большом

числе параллельных процессов к задержке логики добавляется задержка схемы индикации. В некоторых случаях целесообразно сократить схему индикации, индицируя, к примеру, лишь окончание переходных процессов в элементах памяти на выходах автоматов. Такие схемы называются квази-самосинхронными (квази-СС) и являются более производительными и компактными, чем самосинхронные. При правильном проектировании топологии квази-самосинхронные схемы сохраняют свойство инвариантности задержкам, но лишены свойства полной самопроверяемости [7].

Таким образом, проектирование цифровых схем для экстремальных температур представляется одинаково сложным как при выборе синхронного подхода к проектированию, так и самосинхронного. В этой связи целесообразно провести сравнение трех реализаций устройства, спроектированного с использованием синхронной, самосинхронной и квазисамосинхронной схемотехники в условиях вариации температуры и напряжения питания.

#### II. ПРОЕКТИРОВАНИЕ САМОСИНХРОННЫХ СХЕМ

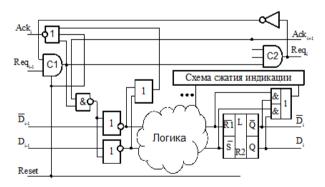

В НИИСИ РАН разработана методика схемной синхронных трансляции конвейерных подход самосинхронные [11]. Новый позволяет осуществлять перекрестную реализацию использованием в качестве исходных данных нетлиста синхронной конвейерной схемы, полученной в САПР синтеза Synopsys Design Compiler [12]. При этом осуществляется автоматическая трансляция блоков логики, синхронные триггеры заменяются индикации самосинхронные, строится схема переходных процессов, а вместо дерева синхронизации используется глобально асинхронное (ГАЛП, GALA) [13] управление, основанное на модульном принципе (так называемый синхростратум). Упрощенная схема самосинхронного автомата с управлением показана на рис. 1 [14].

Рис. 1. Упрощенная схема самосинхронного автомата с модулем синхростратума для использования в конвейерных схемах

Для сброса схемы в начальное состояние используется сигнал Reset. Управление осуществляется с помощью сигналов запроса ( $Req_{i-1}$ ,  $Req_i$ ) и ответа ( $Ack_i$ ,  $Ack_{i+1}$ ). Для упрощения показан автомат только с одним элементом памяти ( $D_i$ ,  $\bar{D}_i$ ) и с

одним парафазным информационным входом ( $D_{i-1}$ ,  $\bar{D}_{i-1}$ ) логического блока. Входы логики блокируются элементами 2ИЛИ-НЕ с помощью фазового сигнала с выхода элемента 2И-НЕ. Также в целях упрощения схема автомата не содержит обратной связи по данным, в результате чего используется защелка (L) в качестве элемента памяти. С-элементы Маллера [15] С1 и С2 являются триггерными устройствами, выход которых сохраняет состояние входов при условии, что логические сигналы на всех входах одинаковы. Схема индикации сжимает выходы индикации окончания переходных процессов в логике и элементах памяти. В квази-самосинхронных схемах индикация окончания переходных процессов в логике не используется, в результате чего теряется свойство самопроверяемости.

# III. МЕТОДИКА ТЕСТИРОВАНИЯ

Для получения наиболее точных результатов сравнения необходимо провести spice-моделирование с использованием экстракции паразитных емкостей и сопротивлений проводов из готовой топологии исследуемых схем. Поскольку возможности spiceмоделирования ограничены существенно вычислительными мощностями, было решено взять разрядного исследования схему 8-ми целочисленного умножения с накоплением (FMA -Fused Multiply Add), содержащую порядка 10 тыс. транзисторов. В разработке использован алгоритм Уоллеса, позволяющий получить наилучшую по быстродействию схему. Проектирование производилось для проектных норм TSMC 65нм с применением стандартных элементов библиотеки, а также дополнительно разработанных С-элементов Маллера и самосинхронных RS-защелок. Разработка элементов проводилась В САПР Virtuoso, характеризация в САПР Silicon Smart.

Спроектирована топология трех реализаций схемы FMA для проведения исследований: синхронная, самосинхронная и квази-самосинхронная. Последние две реализации получены с помощью методики схемной трансляции, где в качестве прототипа использована синхронная схема FMA. Синтез синхронной схемы производился в САПР Synopsys Design Compiler, проектирование топологии всех трех схем проведено в САПР Encounter, экстракция паразитных емкостей и сопротивлений осуществлялась в САПР Calibre. В результате подготовлено три топологии (GDS-II) схем, три spice-нетлиста и три verilog-нетлиста с подключаемыми задержками, экстрагированными из топологии.

Для проведения исследований разработано единое тестовое использующееся окружение, верификации каждой из трех схем, включающее генератор псевдослучайных входных наборов и проверку результатов вычислений. Временное моделирование verilog-нетлиста с подключаемыми задержками производилось c вычислением переключательной активности элементов (формат необходимой для расчета потребления исследуемых схем в САПР Encounter. В результате

получены потребление энергии исследуемых схем и их производительность, рассчитанные с использованием Liberty-моделей элементов И экстрагированием паразитных емкостей, также статического временного анализа САПР Encounter. Для В статического временного анализа квазисамосинхронной И самосинхронной схем Liberty-модели использованы измененные асинхронных элементов, позволяющие привести орграф схемы к ациклическому виду [16].

Spice-моделирование осуществлялось в среде Cadence AMS с симулятором Spectre, что позволило использовать то же тестовое окружение, что и при временном моделировании verilog-нетлиста. Поскольку временное моделирование производиться только для температуры и напряжения, ДЛЯ которых проводилась характеризация библиотечных элементов, сравнение полученных результатов со spice-моделированием проведено только для нормальных условий эксплуатации: температура +25°C и напряжение питания 1.0 В. Для производительности И потребления исследуемых схем в широком диапазоне температур и напряжений питания использовалось только spiceмоделирование.

#### IV. ВАРИАЦИИ ТЕМПЕРАТУРЫ

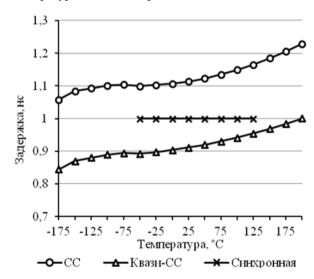

Ѕрісе-моделирование производилось при напряжении питания 1 В и температуре в диапазоне от -175°С до +200°С, с шагом 25°С. На информационные входы подавались псевдослучайные тестовые наборы, одинаковые для всех трех схем. Измерялось два параметра: задержка одной фазы работы схемы, и затраченная энергия. График зависимости производительности исследуемых схем от температуры показан на рис. 2.

Рис. 2. Производительность цифровых КМОП-схем при вариации температуры

Квази-самосинхронная и самосинхронная схемы показали работоспособность во всем диапазоне температур. Поскольку самосинхронные схемы

используют в работе две фазы, задержка сигнала в логике получается примерно в два раза больше, чем в синхронной схеме. На практике двукратную потерю производительности компенсируют удвоением числа стадий самосинхронного конвейера по отношению к синхронной схеме. Но поскольку повышение производительности не являлось целью исследований, то при проектировании самосинхронной и квазисамосинхронной схем удвоение числа стадий не проводилось, и на графике показана усредненная задержка рабочей и спейсерной фазы.

Синхронная схема спроектирована для диапазона, использованного при характеризации библиотек фабрикой: от -40°C до +125°C. Работоспособность схемы на -50°C объясняется запасом по Hold, заложенным при проектировании. Вне расчетного диапазона схема оказалась не работоспособна. При увеличении температуры выше +125°C нарушается время установки (Setup) сигналов и для сохранения работоспособности схемы необходимо тактовую частоту. Заметим, что при температуре ниже -50°C схема работать не булет, поскольку нарушается время удержания (Hold) сигналов, не зависящее от тактовой частоты. Проектирование синхронной схемы для более широкого диапазона температур приведет к увеличению разброса задержек и, как следствие, к снижению тактовой частоты. Работоспособность самосинхронных схем, напротив, инвариантна к изменению производительность задержек, a определяется текущими условиями, а не наихудшей задержкой во всем диапазоне работы.

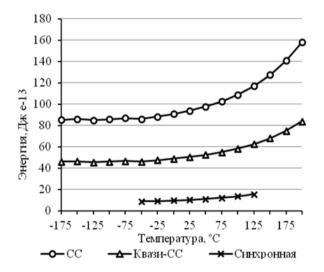

Зависимость энергии потребления одной фазы (или такта) работы схемы показана на рис. 3. Энергия потребления за одну фазу является показателем эффективности работы схем при разных значениях температуры.

Рис. 3. Зависимость энергии потребления одной фазы (или такта) от температуры

Как видно из графика, энергозатраты синхронной схемы в разы ниже, чем у квази-самосинхронной и самосинхронной схем. Это объясняется двумя

факторами: большей площадью и большей переключательной активностью элементов квазисамосинхронной и самосинхронной схем. Сравнение площади элементов в исследуемых схемах приведено в табл. 1.

Таблица 1 Площадь элементов исследуемых схем

| Реализация | Синхр. | CC   | Квази-СС |

|------------|--------|------|----------|

| Кол-во     | 595    | 2116 | 1160     |

| элементов  | 373    | 2110 | 1100     |

| Площадь    |        |      |          |

| элементов, | 1512   | 6773 | 4262     |

| кв. мкм    |        |      |          |

Ток утечки составляет лишь малую (3-6%) долю потребления схем при нормах 65 нм и пропорционален площади элементов схемы, поэтому он в 4.5 раза больше у самосинхронной схемы и в 3 раза больше у квази-самосинхронной. Основной ток потребления приходится на перезаряд паразитных емкостей в проводах при переключении выходов элементов.

Для объяснения представленных на рис. 3 зависимостей затраченной энергии синхронной, квазисамосинхронной и самосинхронной схем можно провести следующую грубую оценку. Согласно результатам моделирования, В исследуемой синхронной схеме каждый такт переключается около 20% элементов, в самосинхронной схеме за одну фазу переключается около 71% элементов, а в квазисамосинхронной – около 63%. Это связано с парафазным кодированием сигналов и двухфазной дисциплиной работы схем. Каждую фазу срабатывает самосинхронных схемах половина элементов логики (ввиду парафазного кодирования), 100% элементов хранения с индикацией (перезапись информации и/или индикация переходных процессов), а также 100% элементов индикации окончания переходных процессов в логике (в исследуемой квазисамосинхронной схеме эти элементы отсутствуют). Очевидно что энергия, затрачиваемая в одной фазе работы схемы, пропорциональна произведению числа элементов в схеме на долю переключаемых элементов. Таким образом, значительно увеличение расхода энергии самосинхронных и квази-самосинхронных схем объясняется их сложностью И высокой переключательной активностью.

Сравнивая потребление синхронных асинхронных схем, часто указывают на отсутствие у асинхронных схем дерева тактового сигнала, на которое приходится, по разным оценкам, от 20 до 50% потребления синхронных схем. Схема самосинхронного автомата на рис. 1 использует фазовый сигнал (выход элемента 2ИЛИ-НЕ) для управления блокировками информационных входов автомата. Этот сигнал имеет самую большую нагрузку, поскольку число входов автомата может быть большим, и на практике заменяется деревом инверторов в целях распределения нагрузки и повышения производительности схемы. При этом дополнительной индикации дерева фазового сигнала в принятой конструкции автомата не требуется. В результате применение GALA подхода и метода трансляции синхронных конвейерных схем в самосинхронные не дают выигрыша в потреблении энергии за счет отсутствия тактового дерева, поскольку цепь тактового сигнала заменяется на схему синхростратума [5] и инверторное дерево фазового сигнала в каждом из автоматов.

Для напряжения питания 1.0 В и температуры +25°С проведено сравнение мощности потребления и производительности исследуемых схем. Результаты были получены тремя различными путями: с помощью анализа потребления и статического временного анализа в САПР Encounter, с помощью временного моделирования с задержками в САПР Incisive, а также с помощью моделирования на spice (табл. 2).

Таблица 2 Производительность и потребление исследуемых схем

| Релизация                    | Синхр. | CC   | Квази-<br>СС |

|------------------------------|--------|------|--------------|

| Задержка в<br>Spice, нс      | 1.0    | 1.11 | 0.92         |

| Задержка в<br>Incisive, нс   | 1.0    | 1.02 | 0.91         |

| Задержка в<br>Encounter, нс  | 1.0    | 1.06 | 0.93         |

| Потребление в<br>Spice, мВт  | 1.21   | 7.03 | 4.54         |

| Потребление в Encounter, мВт | 1.46   | 7.92 | 4.71         |

Моделирование в Incisive и расчет задержек, а также расчет мощности потребления в Encounter проводились с использованием экстрактора паразитных параметров QRC (Cadence). В spiceмоделировании использовались задержки, полученные при помощи экстрактора PEX (Mentor Gr).

Получено соответствие между измеренной производительностью в Encounter и результатами временного моделирования в Incisive. Результаты статического временного анализа оказались хуже результатов моделирования самосинхронных схем, поскольку статический анализ делает расчет на наихудший случай. В моделировании использован генератор случайных чисел, подаваемых на входы схем, поэтому измеренные задержки в схемах получились меньше максимальных. Работа фактическим задержкам является особенностью самосинхронных схем, и статический временной анализ целесообразно использовать только для оценки ситуации возникновения наибольшей задержки в схеме. Ha практике производительность самосинхронных схем постоянно меняется зависимости от подаваемых входы на информационных наборов.

Результаты измерения задержек и потребления в spice-моделировании отличаются в пределах 5% и 10% от результатов, полученных в САПР Encounter и Incisive. По всей видимости, это связано с точностью измерений в моделировании и различиями в работе экстракторов паразитных параметров схем.

#### V. Вариации напряжения питания

Моделирование при высокой температуре показало значительный рост токов потребления. Наиболее эффективный способ снизить мощность потребления заключается в снижении напряжения питания схемы. В этой связи целесообразно исследовать зависимость производительности и потребления схем в широком диапазоне напряжений питания.

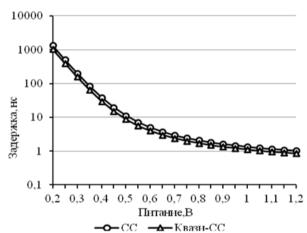

Spice-моделирование проводилось при температуре  $+25^{\circ}$ С и напряжении питания в диапазоне от 200 MB до 1.2 B с шагом 50 MB с тем же тестовым окружением, что и при вариации температуры. Синхронная схема спроектирована с использованием библиотеки элементов для узкого диапазона напряжений питания  $1 \text{ B} \pm 10\%$ , поэтому исследовалась работа только квазисамосинхронной и самосинхронной схем. Во время моделирования измерялись два параметра: задержка и энергия потребления одной фазы. График зависимости производительности исследуемых схем от напряжения питания приведен на рис. 4.

Рис. 4. Производительность цифровых КМОП-схем при изменении напряжения питания

работоспособность Моделирование показало самосинхронных схем при напряжении питания ниже порога открытия транзисторов. Работоспособность схем в этом режиме объясняется зависимостью тока утечки сток-исток от потенциала на затворе, позволяющей переключать выходы элементов без открытия транзисторов. В качестве примера можно рассмотреть поступление положительного фронта сигнала на вход инвертора. При появлении высокого потенциала на затворах входных транзисторов ток сток-исток n-канального транзистора возрастает, а ток утечки р-канального транзистора уменьшается, в результате чего паразитная емкость на выходе инвертора начинает разряжаться – происходит переключение выхода инвертора. Таким образом, при напряжении питания ниже порогового транзисторы работают в режиме управляемых источников тока и сохраняют свою переключательную способность, необходимую для работы цифровой Производительность схемы В ЭТОМ режиме определяется величиной токов утечки и оказалась на три порядка ниже, чем при номинальном напряжении питания (рис. 4).

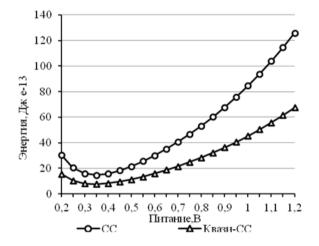

На рис. 5 приведена энергия одной фазы. Использовалось усреднение энергии потребления рабочей фазы и фазы спейсера.

Рис. 5. Зависимость энергии потребления одной фазы от напряжения питания

График иллюстрирует эффективность работы схем при разных напряжениях питания. Наибольшая эффективность соответствует напряжению питания 350 мВ, где достигается наилучшее отношение динамической мощности потребления производительности схемы. Этот эффект объясняется различным соотношением тока потребления задержкой схемы выше и ниже напряжения порога открытия транзисторов. При снижении напряжения порогового потребления питания ниже ток утечками только меняется опрелеляется и незначительно, а энергия растет за счет роста задержек в схеме. При повышении напряжения выше порогового начинает существенно сказываться растущий ток потребления на фоне незначительного уменьшения задержек.

Таблица 3 Наиболее энергоэффективное напряжение питания

| Температура, °С        | -75 | 25  | +125 |

|------------------------|-----|-----|------|

| Напряжение питания, мВ | 300 | 350 | 400  |

Порог открытия транзисторов зависит от температуры; с помощью spice-моделирования получены значения наиболее энергоэффективного напряжения питания исследуемых квази-

самосинхронной и самосинхронной схем для рабочих температур -75°C, +25°C и +125°C (табл. 3).

Таким образом, уменьшение напряжения ниже номинального 1.0 В (для тех. процесса TSMC 65 нм) позволяет не только снизить потребление схемы, но и повысить ее эффективность. При этом максимум эффективности достигается при напряжении питания вблизи порога открытия транзисторов, значение которого меняется с температурой.

Самосинхронные схемы ввиду инвариантности к задержкам элементов сохраняют работоспособность при питании ниже порога открытия транзисторов. Синхронные схемы в таких условиях использовать нецелесообразно, поскольку при напряжении питании ниже порогового даже небольшие отклонения питания приводят к значительным изменениям задержек в схеме (рис. 4).

# VI. Выводы

Результаты spice-моделирования подтверждают работоспособность исследуемых схем в диапазоне температур от -175°C до +200°C, за исключением синхронной схемы, которая спроектирована и работает только в диапазоне от -40°C до +125°C. Расширение температурного диапазона эксплуатации синхронной схемы без перепроектирования возможно только в сторону увеличения температуры за счет снижения тактовой частоты. При этом работоспособность синхронной схемы, спроектированной для более температур, широкого диапазона может гарантироваться, поскольку используемые модели транзисторов (TSMC 65 нм) не точны ниже -40°C и выше +125°C. В то же время исследуемые квазисамосинхронная И самосинхронная схемы инвариантны к задержкам элементов, поэтому точность используемых моделей на краях исследуемого диапазона может сказаться только на количественных результатах моделирования, но не на работоспособности схем.

Проведено сравнение производительности синхронной, квази-самосинхронной и самосинхронной схем. Самосинхронные схемы используют две фазы работы и для получения близкой к прототипу производительности должны проектироваться удвоенным числом стадий конвейера. Поскольку повышение производительности не являлось целью исследований, стадий удвоение числа самосинхронной и квази-самосинхронной схемах не производилось. По этой причине для опенки быстродействия при удвоении числа самосинхронного конвейера бралась усредненная задержка рабочей и спейсерной фазы. Согласно полученным результатам, квази-самосинхронная схема обладает наиболее близкой к синхронной схеме производительностью, в то время как самосинхронная работает схема значительно медленнее. Производительность самосинхронной схемы оказалась на 20% меньше, чем у квази-самосинхронной схемы, объясняется задержкой схемы индикации

окончания переходных процессов в логике, которая у квази-самосинхронной схемы отсутствует.

Исследование затраченной энергии за одну фазу (или такт) работы проводилось с использованием усредненной задержки фаз и выявило значительную между потреблением спроектированных самосинхронных синхронной И схем. самосинхронная и самосинхронная схемы потребляют больше как за счет большего тока утечек (ввиду многократно большей площади элементов), так и за счет динамического потребления, зависящего от числа элементов в схеме и их переключательной активности. При этом потребление энергии за одну фазу работы самосинхронной схемы оказалось, в среднем, в два раза выше, чем у квази-самосинхронной схемы.

снижения потребления температурах целесообразно понижать напряжение питания. Исследована работа квази-самосинхронной и самосинхронной схем в диапазоне напряжений питания от 200 мВ до 1.2 В. Согласно результатам моделирования, понижение напряжения питания ниже номинала (1.0 В) сопровождается снижением затрат одну фазу работы. Максимум достигается вблизи напряжения эффективности порога открытия транзисторов, которое меняется в зависимости от температуры. Моделирование также показало, что квази-самосинхронная и самосинхронная схемы сохраняют работоспособность при напряжении питания ниже порога открытия транзисторов вплоть до границы исследуемого диапазона (200 мВ).

Таким образом, при проектировании для широкого диапазона температур целесообразно контролировать напряжение питания, с помощью которого можно добиться, к примеру, одинаковой производительности во всем диапазоне, либо одинаковой потребляемой мощности. Проектирование синхронных схем требует использования моделей транзисторов гарантированной точностью во всем диапазоне Фабрика **TSMC** температур и напряжений. предоставляет моделей транзисторов для тех. процесса 65 нм и диапазона температур шире -40°...+125°С или напряжений шире, чем 1.0 B  $\pm 10\%$ , поэтому работоспособность невозможно гарантировать синхронных схем в более широком диапазоне Таким образом, температур И напряжения. спроектированные квази-самосинхронная самосинхронная схемы оказались наиболее приспособлены для работы в исследуемом диапазоне температур и напряжений питания, но в диапазоне работы синхронной схемы имеют меньшую значительно производительность большее И потребление, чем синхронная схема, а также занимают значительно большую площадь. Сравнение самосинхронных И квази-самосинхронных схем что последние показывает, оказываются предпочтительными в том случае, если не требуется самопроверяемость, поскольку самосинхронные схемы менее производительны и больше потребляют.

# Поддержка

Исследование выполнено при финансовой поддержке РФФИ в рамках научных проектов № 14-29-09238 офи м и № 14-29-09284 офи м.

# Литература

- [1] Yao Y., Ma D., Dai F. A 12-bit interleaved opamp-sharing pipeline ADC for extreme environment applications // 10th IEEE International Conference on Solid-State and Integrated Circuit Technology. 2010. P. 394–396.

- [2] Woo D., Yun J., Jun Y. et al. Extremely high temperature and high pressure (x-HTHP) endurable SOI device & sensor packaging for deep sea, oil and gas applications // IEEE 16th Electronics Packaging Technology Conference. 2014. P. 16–21.

- [3] Rahman A., Shepherd P., Bhuyan S. et al. A family of CMOS analog and mixed signal circuits in SiC for high temperature electronics // 2015 IEEE Aerospace Conference, 2015, P. 1–10.

- [4] Clark W.F., El-Kareh B., Pires R.G. Low Temperature CMOS - A Brief Review // IEEE Transactions on Components, 1992. V. 15, I. 3, P. 397–404.

- [5] Мараховский В.Б., Мелехин В.Ф. Проектирование средств синхронизации блоков глобально асинхронных систем с произвольной локальной синхронизацией // Информационно-управляющие системы, 2010. No. 1. C. 29–38.

- [6] Muller D., Bartky W.S. A theory of asynchronous circuits. // In Proceedings of an International Symposium on the Theory of Switching. 1959. P. 204–243.

- [7] Астановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. / Под ред. В.И. Варшавского – М.: Наука. 1976. 423 С.

- [8] Мараховский В. Б., Розенблюм Л. Я., Яковлев А. В. Моделирование параллельных процессов. Сети Петри. // Санкт-Петербург: Профессиональная литература, АйТи-Подготовка. 2014. 400 С.

- [9] Варшавский, В.И. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / В.И. Варшавский, М.А.Кишиневский, В.Б. Мараховский и др.; под ред. В.И. Варшавского. Москва: Наука. 1986. 400 С.

- [10] Poliakov I., Khomenko V., Yakovlev A. Workcraft A Framework for Interpreted Graph Models // PETRI NETS. 2009. P. 333–342.

- [11] Власов А.О., Сурков А.В., Маршрут проектирования самосинхронных конвейерных схем с использованием возможностей САПР // Программные продукты и системы. 2015. No. 4. C. 110–115.

- [12] Сурков А.В. Использование Synopsys Design Compiler для синтеза самосинхронных схем // Программные продукты и системы. 2014. No. 4. C. 24–30.

- [13] Мараховский В.Б., Мелехин В.Ф. Проектирование глобально асинхронных систем с произвольной локальной синхронизацией // Информационно-управляющие системы. 2011. No. 1. C. 41-49.

- [14] Бобков С.Г., Мараховский В.Б, Сурков А.В. Модуль синхростратума для волновой обработки данных. Заявка на патент РФ, No. 2015112523 от 07.04.2015 г.

- [15] Muller D.E. Asynchronous logics and application to information processing // Symposium on the Application of Switching Theory to Space Technology. 1962. P. 289–297.

- [16] Сурков А.В., Использование статического временного анализа для проектирования самосинхронных схем // Информационные технологии. 2016. No. 2. T. 22. C. 139—145.

# Design of digital CMOS circuits for extreme temperatures

A.O. Valsov<sup>1</sup>, V.B. Marakhovsky<sup>2</sup>, A.V. Surkov<sup>1</sup>

<sup>1</sup>Department of Russian Academy of Sciences Institute of System Researches, {vlaalex, surkov}@cs.niisi.ras.ru

<sup>2</sup>Saint-Petersburg Polytechnic University of Peter the Great, vbmarak@gmail.com

Keywords — extreme environments, self-timed circuits, GALA, EDA.

#### **ABSTRACT**

The article concerns the complexity of digital circuits design for extended temperature ranges. TSMC 65GP process was used in research. We developed physical layouts of three different implementations of 8-bit integer Fused Multiply-Add (FMA) circuit: synchronous, self-timed and self-timed with partial acknowledgement. GALA approach and early developed approach of direct translation of synchronous pipeline into self-timed one were used in design of both self-timed circuits.

Comparative analysis in typical corner was made on the results of three different approaches, i.e. spice-level simulations (Cadence Spectre), time- and power-estimation in Cadence Encounter, and functional simulations with delays. All three approaches reveal matching results within 5-10% deviation.

Spice simulations of three implementations of FMA under condition of 1.0 V supply and temperature variations from -175°C till +200°C show us the lack of performance and higher consumption of self-timed implementation in comparison with synchronous one. Disadvantages of synchronous approach are lack in performance with temperature range expansion and unpredictable behavior of circuit, designed using existing transistor models (which are intended to use within -40°C .. +125°C range). In addition we provide simulations of both self-timed circuits under condition of +25°C temperature and supply variations from 200 mV till 1.2 V. Simulation results show operability of self-timed circuits with under-threshold voltage supply. The self-timed circuit with partial acknowledgement shows the better performance and lower consumption than the self-timed circuit with full acknowledgement.

# REFERENCES

- [1] Yao Y., Ma D., Dai F. A 12-bit interleaved opamp-sharing pipeline ADC for extreme environment applications. 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, 2010, pp. 394–396.

- [2] Woo D., Yun J., Jun Y. et al. Extremely high temperature and high pressure (x-HTHP) endurable SOI device & sensor packaging for deep sea, oil and gas applications. IEEE 16th Electronics Packaging Technology Conference, 2014, pp. 16-21

- [3] Rahman A., Shepherd P., Bhuyan S. et al. A family of CMOS analog and mixed signal circuits in SiC for high

- temperature electronics. 2015 IEEE Aerospace Conference, 2015, pp. 1–10.

- [4] Clark W.F., El-Kareh B., Pires R.G. Low Temperature CMOS A Brief Review. IEEE Transactions on Components, 1992, Vol. 15, Issue 3, pp. 397–404.

- [5] Marakhovsky V.B., Melekhin V.F. Proektirovanie sredstv synchronizatsii blokov global'no asynchronnyh system s proizvol'noi lokal'noi synchronizatsyei, Informatsionno-upravlyayuschie systemy. Programmnye i apparatnye sredstva, 2010, № 1, pp. 29–38 (in Russian).

- [6] Muller D., Bartky W.S. A theory of asynchronous circuits. In Proceedings of an International Symposium on the Theory of Switching, 1959, pp. 204–243.

- [7] Astanovsky A.G., Varshavskij V.I., Marakhovsky V.B., Peschansky V.A., Rosenblum L.Y., Starodubtsev N.A., Finkelstein R.L., Tsirlin B.S. Aperiodicheskie avtomati, Moskva, Nauka, 1976, 424 p (in Russian).

- [8] Varshavskij V.I., Kishinevsky M.A., Marakhovsky V.B., Peschansky V.A., Rosenblum L.Y., Taubin A.R., Tsirlin B.S. Avtomatnoe upravlenie asynhronnimy processami v EVM, Moskva, Nauka, 1986, 400p (in Russian).

- [9] Marakhovsky V.B., Rosenblum L.Y., Yakovlev A. Modelirovanie parallelnyh processov. Seti Petry. Saint-Peterburg: Professionalnaya literatura, AiTi-Podgotovka, 2014, 400 p (in Russian).

- [10] Poliakov I., Khomenko V., Yakovlev A. Workcraft A Framework for Interpreted Graph Models. PETRI NETS, 2009, pp. 333–342.

- [11] Vlasov A.O., Surkov A.V. Automated design flow of self-timed pipelines using EDA tools. Programmye produkty i systemy, 2015, No. 4, pp. 110–115 (in Russian).

- [12] Surkov A.V. Synthesis of burst-mode asynchronous schemes using Synopsys Design Compiler. Programmnye produkty i systemy, 2014, No. 4, pp. 24–30 (in Russian).

- [13] Marakhovsky V.B., Melekhin V.F. Proektirovanie global'no asynchronnyh system s proizvol'noi lokal'noi synchronizatsyei. Informatsionno-upravlyayuschie systemy. Programmnye i apparatnye sredstva, № 1, (50) 2011, pp. 41–49 (in Russian).

- [14] Bobkov S.G., Marakhobsky V.B., Surkov A.V. Module of a Synch-stratum for Wave Data Processing, Submitted to Russian Patent Service on 07.04.2015, registration No. 2015112623.

- [15] Muller D.E. Asynchronous logics and application to information processing. Symposium on the Application of Switching Theory to Space Technology. Stanford University Press, 1962, pp. 289–297.

- [16] Surkov A.V. STA algorithms for developing self-timed schemes. Inforamtion Technologies, 2016, No. 2, T. 22, pp. 139–145 (in Russian).