# Структурные преобразования макроблоков СБИС путём перегруппировки их функционально однородных зон

Н.М. Сафьянников $^{1,2}$ , А.К.Фролкин $^{1,3}$

<sup>1</sup> Санкт-Петербургский государственный электротехнический университет "ЛЭТИ" им. В.И. Ульянова (Ленина),

## <sup>2</sup>000 "ЛЭТИНТЕХ"

<sup>3</sup> ООО "Сенсотроника", sysan@sysan.sp.ru, anfrolkin@gmail.com

Аннотация — Эта статья посвящена структурной оптимизации топологии регулярных макроблоков СБИС. Рассматриваются два подхода, меняющих структурно-топологический план устройства и позволяющих в конечном итоге уменьшить площадь устройства и иногда увеличить скорость снятия результата.

Первый подход — это перегруппировка структурнотопологического плана, суть которого в переносе некоторых функций макроблоков из зон с высокой плотностью упаковки элементов в области с низкой плотностью размещения элементов.

Второй подход – вынесение участков топологии за пределы макроблока, суть которого в пересмотре архитектуры и принципа работы схемы в целом, с возможной универсализацией отдельных частей макроблоков для выполнения типовых операций.

*Ключевые слова* — макроблоки СБИС, структурнотопологическая оптимизация, топологические приемы, умножитель.

### І. Введение

Одним из основных требований, предъявляемых к микроэлектронным проектам, является плотность упаковки схем на кристалле. Наибольшую плотность упаковки обеспечивают топологические конфигурации на основе сборок транзисторов сложной формы с различной пространственной ориентацией. В современных условиях еще одной тенденцией развития микроэлектроники является сокращение цикла проектирования, путем автоматизации этапов и цикла в целом. Поэтому топологической организации ячеек, предполагающим сложную форму и взаимное расположение основных (транзисторов), элементов предпочитают топологические конфигурации, в которых затворы транзисторов ориентированы строго определенным образом, а сборки транзисторов разного типа с объединенными соседними истоковыми/стоковыми областями располагаются параллельно друг другу в две линии. Это топологическое решение, получившее название "схем на диффузионных линейках", стало

одной из основных топологических концепций в современной микроэлектронике, позволяющей разработку оптимальной автоматизировать диффузионных линеек схемы. Сейчас современные схемы топологий строятся на автоматизированных средствах синтеза логики, позволяющих разложить модель поведения устройства на элементарные логические элементы, и на средствах синтеза схем, переводящих логическую схему в библиотечные ячейки на базе транзисторов и связи между ними. Несмотря на существование процесса создания устройств на базе библиотечных элементов, пока рано говорить о существовании оптимальных методик синтеза схем, так как на конечный продукт сильно влияет качество библиотеки стандартных элементов [1].

Часть вычислительных устройств регулярную структуру, которая формируется при создании архитектуры c повторяющимися однотипными операциями. Для таких макроблоков с регулярной структурой особенно важен состав библиотеки, поскольку ячейки выстраиваются не только в ряды, но и в колонки. Такое расположение ячеек в колонки и ряды позволяет быстро менять разрядность и упрощает планирование трассировки. Определив регулярный макроблок функциональных блоков, можно перетасовывая блоки, достичь параметров габаритов требуемых требуемого размещения входных, выходных сигналов и шин.

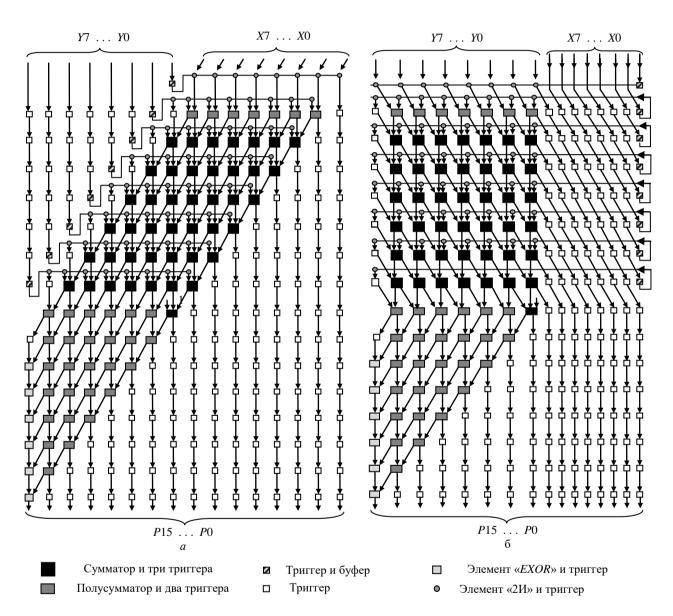

Примером устройства с регулярной структурой выступать хорошо известная схема конвейерного умножителя. Существуют различные варианты схем умножителей, например, устройство для умножения [2] или конвейерный сумматор и умножитель [3], представленный на рис. 1 (а). Структурно представленные устройства содержат ячейки, делящие матрицу на колонки и ряды, где ряды порции частичных произведений соответствии с конвейерным процессом. Благодаря технике помещения защелок между соседними рядами ячеек сильно увеличивается скорость, с которой последовательные произведения появляются на выходе.

Хотя представление устройства в виде матрицы упрощает процесс размещения ячеек и трассировки соединений, возможно возникновение разреженных зон в рядах или колонках. Проработка общего плана макроблока позволяет поместить в каждый ряд матрицы ячейки, имеющие схожую минимальную высоту, а в колонки — схожие по ширине ячейки. Иногда логическая схема макроблока построена таким образом, что сложно создать одну или несколько ячеек, не приводящих в регулярной структуре к

раздвижке в колонке или ряду. Для таких случаев необходимо подобрать другой структурнотопологический план или, возможно, пересмотреть принцип работы макроблока. В статье рассматриваются приемы преобразований регулярных устройств. Представлено две методики:

- 1) перегруппировка структурно-топологического плана;

- 2) вынесение некоторых участков топологии за пределы макроблока.

Рис. 1. Исходная структурно-топологическая схема умножителя (а); та же схема после перестановок ячеек триггеров, сумматоров и сужения ширины правой части (б)

#### II. ПЕРЕГРУППИРОВКА ЭЛЕМЕНТОВ

В статье [4] представлены приемы перегруппировок, в результате этих методик

структурно-топологических преобразований удалось уменьшить площадь сумматора на 25%. Перегруппировки позволяют по возможности перенести некоторые функции макроблоков из зон с

высокой плотностью упаковки элементов в области с низкой плотностью размещения элементов. На примере преобразования умножителя [4] видно, что несмотря на то, что принцип работы не поменялся, изменилась структура и топология большинства ячеек макроблока. В исходной схеме [3], изображенной на рис. 1 (а), линии с битами множителя проходили только непосредственно через ячейки сумматора. На рис. 1 (б) линии с битами множителя из буферного каскада распространяются через всю ширину макроблока, проходя через ячейки сумматора и ячейки триггеров, хранящих биты множителя, и ячейки триггеров, биты частичного результата. Ячейки сумматора теперь имеют перенос, направленный вертикально вниз, а результат суммы направлен позволяет выстроить вправо. что прямоугольник. В прототипе ячейки суммы выстраивались в параллелепипед, что увеличивало ширину всего устройства, так как ячейки сумматора больше всех остальных в ширину, а дополнительные колонки сумматоров увеличивали ширину всего макроблока. Можно уменьшить ширину колонок во всех рядах, в которых расположены только триггеры. Для этого нужно максимально сузить (ширину) ячейки

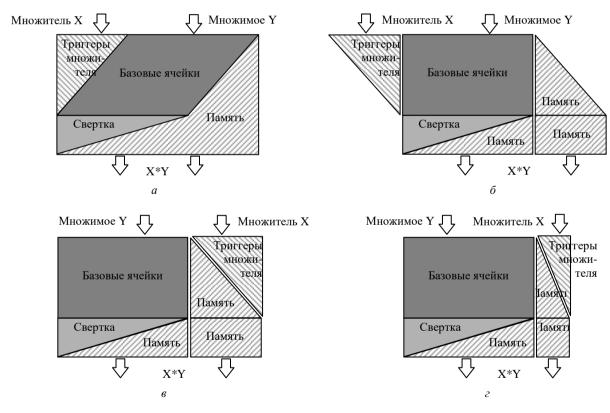

с триггерами, высоту при этом нужно подогнать по высоте ячеек, стоящих в том же ряду. На рис. 1 (б) таким образом уменьшена ширина колонок, на которые подается множитель. Процесс перегруппировки структурно-топологического плана представлен на рис. 2, начиная от исходной схемы и до схемы на рис. 2 (г), аналогичной изображенной на рис. 1 (б).

Особенностью такой методики оптимизации можно назвать то, что оптимизацию можно проводить на регулярных схемах, поскольку топология делится (раскладывается) на функциональные блоки. Каждый из этих блоков может состоять из одинаковых ячеек, связанных или несвязанных между собой, выполняющих единую или одинаковую функцию в логике работы всей микросхемы. В данной статье идет речь как раз о вариантах размещения ячеек. В регулярных схемах вычислительных устройств происходит поиск размещения ячеек из разных блоков в одном ряду или колонке. В зависимости от того, какие ячейки расположены в каждом ряду и от того, как много придется проводить связей между ячейками в одном или разных рядах, будут определяться площадь и быстродействие макроблока.

Рис. 2. Этапы изменения структурно-топологического плана конвейерного арифметического умножителя: исходная структура (а); спрямление параллелепипеда с базовыми ячейками (б); перенос триггеров множителя слева направо (в); определение минимально допустимых ширин ячеек памяти и триггеров стоящих в одной колонке друг над другом и в одном ряду с базовыми ячейками (г)

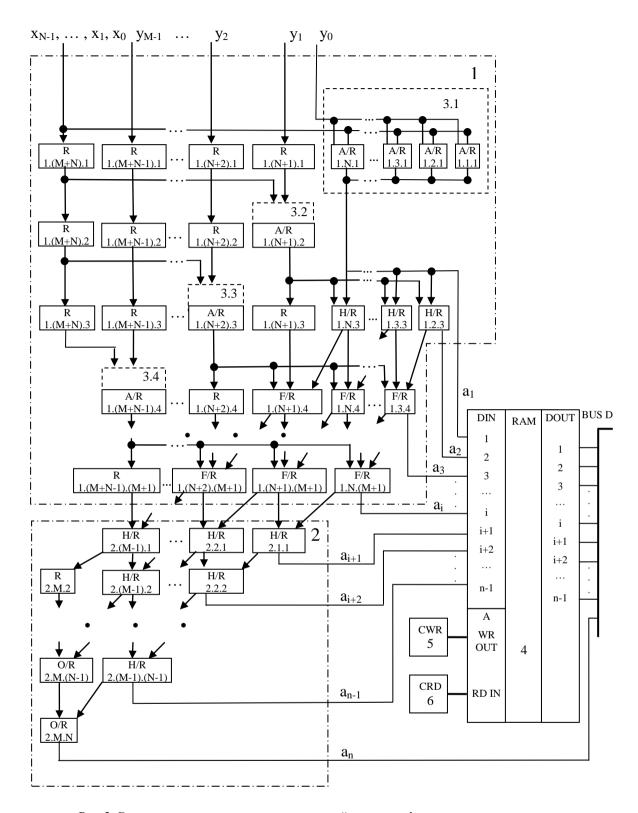

Рис. 3. Структурно-топологическая схема конвейерного арифметического умножителя

В общем виде структурный план топологии можно изобразить как множество горизонтальных рядов с размещенными в них ячейками. Вертикальные связи между ячейками проводят верхними слоями металла: чем меньше будет связей между удаленными

ячейками, тем меньше придется оставлять площадь на трассировку. Поэтому в структурно-топологическом плане связи в верхнем слое металла проводят вертикально без горизонтальных участков, для этого же ячейки размещают колонками. Но если удачно

разместить ячейки, можно проводить значительные связи между ячейками в слое поликремния, а вертикальные связи в верхнем слое металла сделать настолько короткими, что это позволило бы проводить в верхнем слое горизонтальные линии и даже целые шины.

### III. РЕАЛИЗАЦИЯ ЧАСТЕЙ УСТРОЙСТВА В ВИДЕ ОТДЕЛЬНЫХ БЛОКОВ

Еще один способ создания топологий с плотно упакованной структурой – это пересмотр логики работы макроблока с вынесением некоторых функций за пределы макроблока. Так, например, в структуре умножителя [5] на рис. З участок хранения частичного результата умножения был вынесен из макроблока. В топологии умножителя выполняется подсчет как частичной суммы, так и всей суммы, при этом существенно уменьшилась площадь умножителя. Функции хранения результата выполняются отдельном макроблоке, предназначенном для хранения данных и имеющем также высокую плотность размещения элементов. Используя каждый блок как самостоятельную единицу, можно распределять функции между этими блоками и повторно использовать (через обратную связь или циклические связи) на разных этапах вычислений. Уже довольно давно существует практика повторного использования участков топологии для различных функций или различных этапов одной функции. Использование обособленной памяти для выполнения хранения частичного результата как раз укладывается в эту концепцию.

Пример использования одних и тех же блоков для выполнения разных функций можно увидеть в американском патенте [6], в котором в разных режимах можно либо перемножать, либо складывать переменные. Для смены функции умножения на функцию сложения достаточно просто отключить несколько коньюкторов. В представленном патенте [5] было сделано решение, что, во-первых, для высокой скорости срабатывания бывает достаточно и частичной суммы, во-вторых, регистровую память иногда можно иметь общую для нескольких вычислительных макроблоков.

Использование одного и того же блока для разных функций, конечно, приводит к увеличению площади используемой конкретно для одной топологии. умножителя функции. случае площадь, используемая для умножения, площадь топологии с регистрами памяти и плошаль, отведенная на трассировку связей, в сумме больше, чем умножитель с встроенными регистрами. Но сложно представить устройство без элементов памяти или выполняющее только одну арифметическую операцию, поэтому сочетание в устройстве нескольких арифметических операций позволит в итоге уменьшить общую площадь кристалла.

Для решения с использованием обратной связи очевидна потеря быстродействия, поскольку для подсчета одного результата несколько тактов устройство будет занято подсчетом этого числа. Но зато меньше аппаратные затраты, чем если бы для каждого этапа вычислений размещать в топологии однотипные элементы вычислений и хранения.

#### ЗАКЛЮЧЕНИЕ

В результате приведенных примеров структурных удалось преобразований уменьшить площадь В топологии. перегруппировки случае функциональных площадь топологии зон, конвейерного умножителя арифметического уменьшилась на 25 %. При вынесении участков топологии за пределы макроблока принцип работы того же арифметического умножителя немного поменялся, появились новые возможности досрочного снятия частичного результата. Говорить об уменьшении площади топологии для второй методики лучше в каждом конкретном случае отдельно, в для нескольких арифметических совокупности устройств, например с общей памятью.

#### Поддержка

Приведенные в статье результаты исследований в области структурных преобразований макроблоков СБИС получены: в СПбГЭТУ при финансовой поддержке РФФИ в рамках гранта № 14-07-31098, в "Сенсотронике" и "ЛЭТИНТЕХ" при финансовой поддержке Фонда содействия и развития малых форм предприятий в научно-технической сфере в рамках контрактов №168ГС1/6807 и №443ГС3/15263 соответственно.

### Литература

- [1] Рабаи Ж.М., Чардаксан А., Николич Б. Цифровые интегральные схемы. Методология проектирования. Вильямс, 2007. 912 с.

- [2] Пат. 4748583 US, МПК G06F7/52. Cell-Structured Digital Multiplier of Semi-Systolic Construction / Noll Т.; патентообладатель Siemens Aktiengesellschaft; заявл. 05.08.1985; опубл. 31.05.1988.

- [3] Hatamian M., Gash G. L. A 70 MHz 8-bit\*8-bit parallel pipelined multiplier in 2.5 micron CMOS -// IEEE Journal of. Solid-State Circuits. 1986. V. SC-21, № 4. P. 505-513.

- [4] Миронов С. Э., Сафьянников Н. М., Фролкин А. К. Методика структурно-топологической оптимизация регулярных макроблоков СБИС, // Изв. СПбГЭТУ «ЛЭТИ». 2015. Вып. 1. С. 17-23

- [5] Пат. 2546072 С1 РФ, МПК G06F7/527 (2006.01). Конвейерный арифметический умножитель / С.Э. Миронов, Н.М. Сафьянников, А.К. Фролкин; патентообладатель ООО "ЛЭТИНТЕХ". № 2013143270/08; заявл. 24.09.2013; опубл. 10.04.2015, Бюл. №10. 19 с.

- [6] Пат. 4887233 US, МПК G06F7/52; G06F7/50. Pipeline Arithmetic Adder And Multiplier / Cash G.L., Hatamain M., Ligtenberg А.; патентообладатель AT&T Bell Laboratories; заявл. 31.03.1986; опубл. 12.12.1989.

# Converting VLSI macroblock structure by regrouping uniform function blocks

N.M. Safyannikov<sup>1,2</sup>, A.K. Frolkin<sup>1,3</sup>

<sup>1</sup>Saint Petersburg Electrotechnical University "LETI",

# <sup>2</sup>LETINTEH

<sup>3</sup> Sensotronika, sysan@sysan.sp.ru, anfrolkin@gmail.com

Keywords — VLSI macroblocks, structural-layout optimization, layout technique, multiplier.

#### ABSTRACT

The article is devoted to structure optimization of repeating VLSI macroblocks. Two ways, which change the structure-layout design, are considered. They can reduce the layout area and increase the rate of results reading. Two ways, which change the structure-layout design, are considered. They can reduce the layout area and sometimes increase speed result yield.

An one important requirement for VLSI projects is a high elements density on the chip layout.is high elements density on chip layout. The highest elements density on the chip is provided by collection of the transistors with complex shape and with different orientation in space. One more method is optimizing cells placement and routing between cells. Some algorithms of the library cells already exist, but they do not provide optimal results, because the results depend on the cells quality.. Some algorithms of the library cells already exist, but they do not provide optimal results, because the results depend on the cells quality.

The first optimization technique is regrouping structural-layout scheme. The main idea is to divide macroblock into functional blocks and try some different versions of blocks placement or shape. The example presented in the article is a pipelined multiplier. The example presented in the article is a pipelined multiplier. It was divided into blocks, and then some blocks were moved and rotated. The operation allows reducing layout square.

The second technique is to transfer a part of functions out the considered section. The technique means changing device function and device layout. For example transfer of synchronization registers subsection out pipelined arithmetic multiplier allows one to get partial product before full result is computed. This technique reduces the layout area, if the functional section was used by macroblocks, and increases a speed in the mode, where lower bits are sufficient. This technique reduces the layout

area, if the functional section was used by macro-blocks, and increases a speed in the mode, where lower bits are sufficient.

#### **SUPPORT**

The research results in the area of structure optimization layout of VLSI macroblocks provided in this article have been taken with sponsorship grant №14-07-31098 of Russian Foundation for Basic Research in Saint Petersburg Electrotechnical University "LETI". Also research results been taken with sponsorship contract of Foundation for Assistance to Small Innovative Enterprises №168GS1/6807 in "LETINTEH" Ltd and contract of Foundation for Assistance to Small Innovative Enterprises №443GS3/15263 of Foundation for Assistance to Small Innovative Enterprises in "Sensotronica" Ltd.

#### REFERENCES

- [1] Rabaey J.M., Chandrakasan A., Nikolic B. Digital integrated circuits. A design perspective. Williams, 2007, 912 p. (in Russian).

- [2] Patent Number 4748583 US, Int. Cl. G06F7/52. Cell-Structured Digital Multiplier of Semi-Systolic Construction / Noll T.; assignee Siemens Aktiengesellschaft; filed. 05.08.1985; data of patent. 31.05.1988.

- [3] Hatamian M., Gash G. L. A 70 MHz 8-bit\*8-bit parallel pipelined multiplier in 2.5 micron CMOS -// IEEE Journal of. Solid-State Circuits. 1986. V. SC-21, № 4. P. 505-513.

- [4] Mironov S.E., Safyannikov N.M., Frolkin A.K., Metodika strukturno-topologicheskoj optimizacija reguljarnyh makroblokov SBIS. Izv. SPbGETU, "LETI", 2015, no. 1, pp. (in Russian).

- [5] Pat. 2546072 S1 RF, MPK G06F7/527 (2006.01). Konvejernyj arifmeticheskij umnozhitel' / S.E. Mironov, N.M. Safyannikov, A.K. Frolkin; patentoobladatel' OOO "LETINTEH". — № 2013143270/08; zajavl. 24.09.2013; opubl. 10.04.2015, Bjul. №10. — 19 p. (in Russian).

- Pattent Number 4887233 US, Int. Cl. G06F7/52; G06F7/50.

Pipeline Arithmetic Adder And Multiplier / Cash G.L.,

Hatamain M., Ligtenberg A.; assignee AT&T Bell Laboratories; filed. 31.03.1986; data of patent. 12.12.1989.