# Рекуррентная потоковая архитектура: технические аспекты реализации и результаты моделирования

Д.В. Хилько, Ю.А. Степченков, Д.И. Шикунов, Ю.И. Шикунов

Институт проблем информатики РАН Федерального исследовательского центра «Информатика и управление» РАН

#### Содержание

- Введение

- Описание прототипа гибридной двухуровневой архитектуры рекуррентного обработчика сигналов (ГАРОС)

- Архитектурные особенности ГАРОС

- Демонстрация особенностей ГАРОС на примере быстрого преобразования Фурье (БПФ)

- Результаты аппаратно-программного моделирования ГАРОС

- Заключение

#### Введение

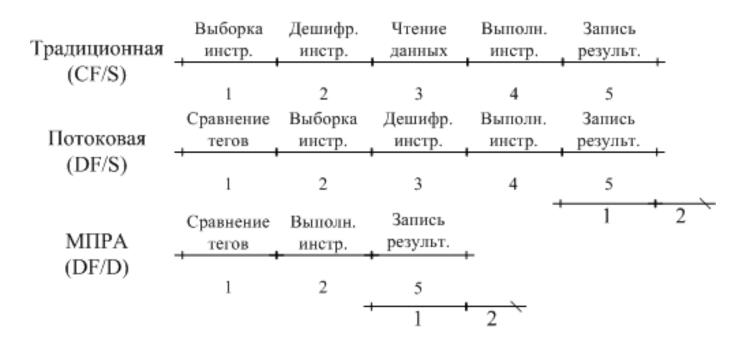

## Ключевые этапы разработки потоковой рекуррентной архитектуры:

- Создание программной и аппаратной моделей, отражающих ключевые особенности и механизмы архитектуры

- Решение ряда проблем, присущих потоковым архитектурам, как классу

- Разработка специализированных средств программно-аппаратного моделирования

- Создание методик программирования и программная реализация целевых задач ЦОС

- Обработка результатов моделирования и оценка эффективности полученной реализации архитектуры

# Основные принципы и преимущества архитектуры

Основные принципы:

- -Самодостаточность данных

- Рекуррентная организация вычислительного процесса

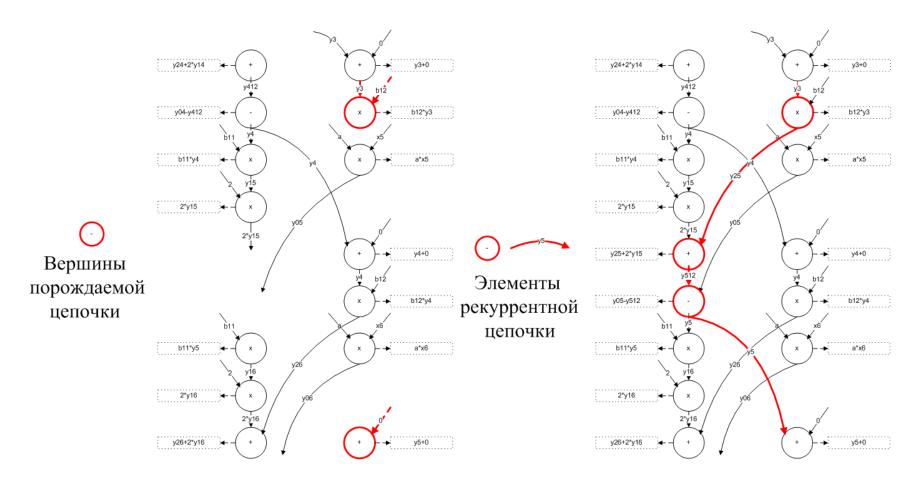

#### Имплементация рекуррентности

Разворачиваемый потоковый граф

Развернутый потоковый граф

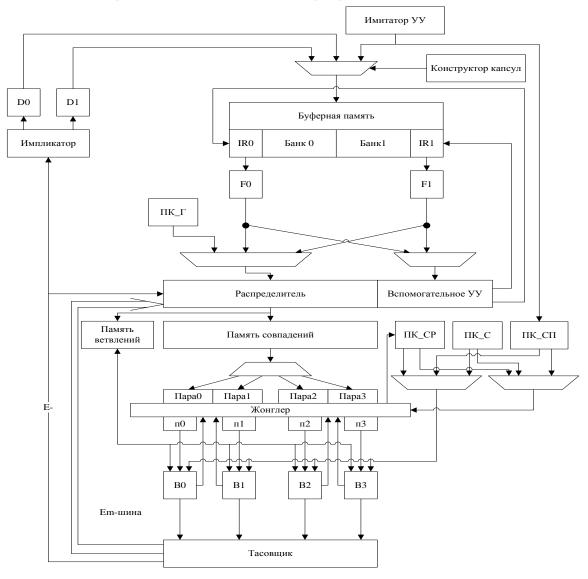

# Прототип многоядерной потоковой рекуррентной архитектуры

Наиболее целесообразным вариантом реализации рекуррентного обработчика сигналов (РОС) на основе ПЛИС является гибридная двухуровневая архитектура рекуррентного обработчика сигналов (ГАРОС):

- ведущий фон-неймановский процессор на управляющем (верхнем) уровне (УУ)

- ряд потоковых процессоров на нижнем уровне рекуррентном операционном устройстве (РОУ)

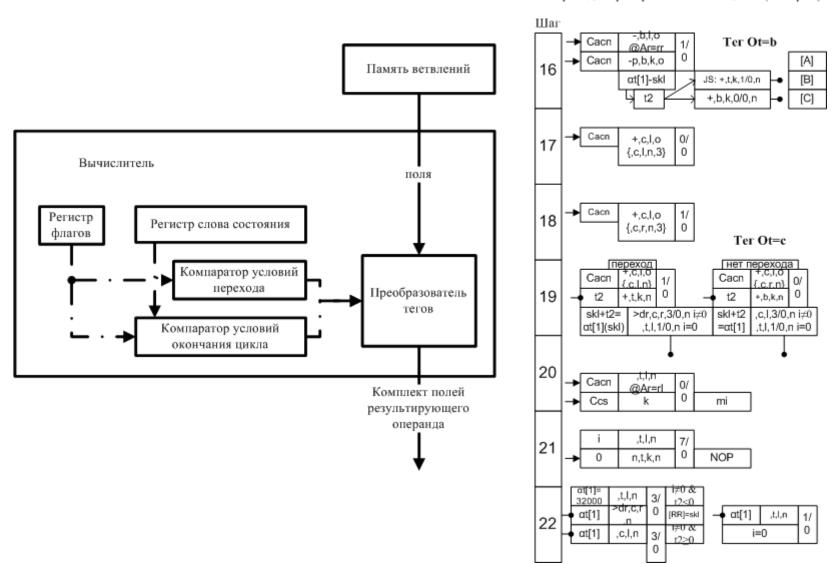

#### Архитектура РОУ

# Организация вычислительного процесса РОУ

- Компонент Распределитель осуществляет выборку операндов из буферной памяти (БП) и их рассылку в соответствующие потоки (секции), заданные в теговых полях;

- Компонент Память совпадений (ПС) осуществляет сравнение теговых полей и формирование пар совпавших операндов;

- Компонент Жонглер осуществляет разделение единого потока самоопределяющихся данных на два потока – данных и инструкций, а также их распределение по входам Вычислителя;

- Компонент Вычислитель осуществляет выборку данных из заданных источников, вычисление результата и рекуррентные преобразования;

- Компонент Тасовщик осуществляет пересылку полученных результатов между параллельными потоками, а также в Импликатор;

- Компонент Импликатор осуществляет запись выходных данных в БП.

## Распределение нагрузки двухуровневой архитектуры

| Задачи УУ                | Задачи РОУ              |  |  |

|--------------------------|-------------------------|--|--|

| Вычисления (10%):        | Вычисления (90%):       |  |  |

| Масштабирование данных   | Фильтр Баттеруорта      |  |  |

| Автоматический контроль  | Логарифмирование        |  |  |

| усиления                 | RASTA-фильтрация        |  |  |

| Определение начала слова | Экспоненцирование       |  |  |

| Определение конца слова  | Косинусное ИДПФ         |  |  |

| Деление                  | Рекурсия Дурбина-Скурра |  |  |

| Подготовка данных        | PLP-параметры           |  |  |

|                          | Дельта-расширение       |  |  |

|                          | Евклидово расстояние    |  |  |

|                          | Витерби                 |  |  |

|                          |                         |  |  |

|                          |                         |  |  |

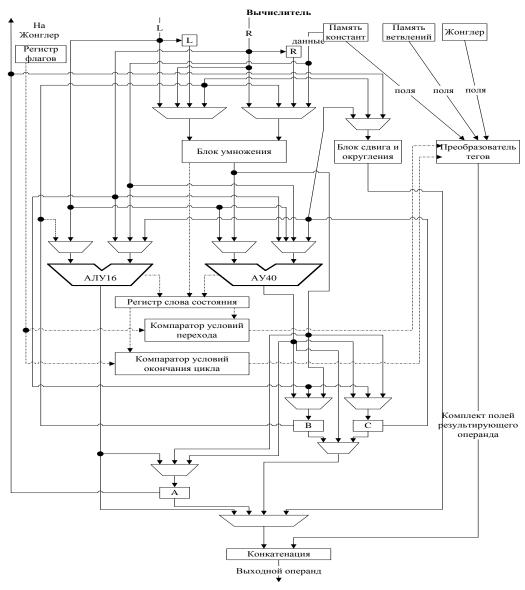

#### Архитектурные особенности ГАРОС

- Суперскалярная архитектура блока Вычислитель и поддержка рекурсии

- Механизмы работы с константными данными

- Поддержка циклических процедур (внутренние циклы)

- Многократное повторение программ и повторное использование выходных данных (внешние циклы)

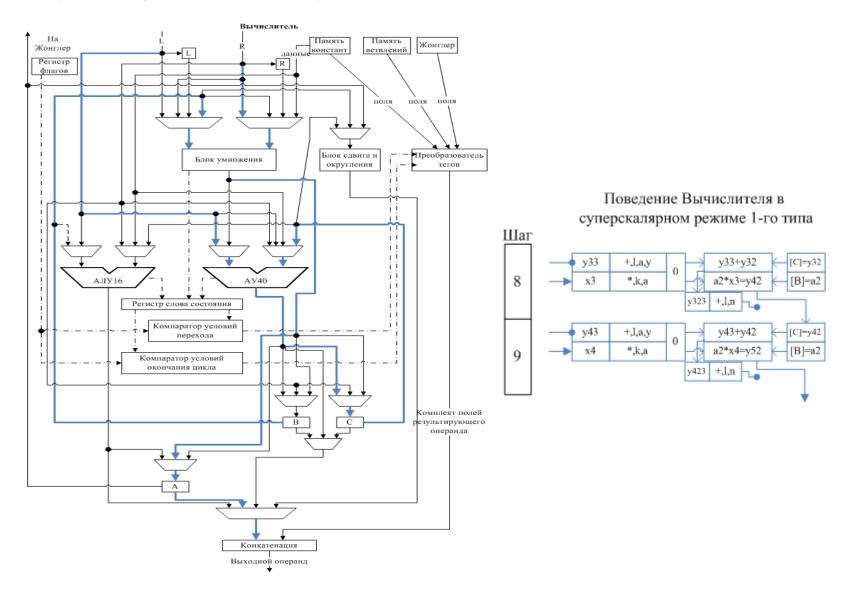

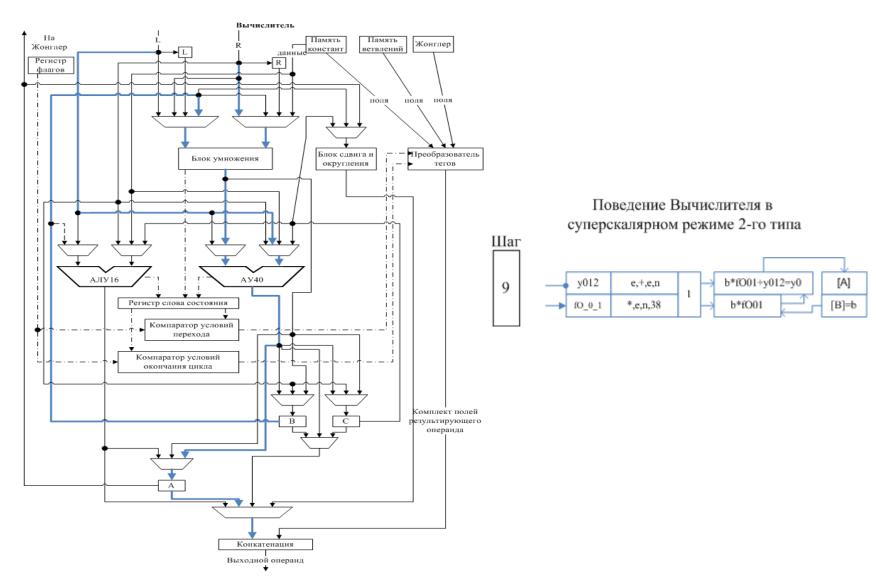

#### Структурная схема модели Вычислителя

#### Суперскалярность Вычислителя

#### Суперскалярность Вычислителя

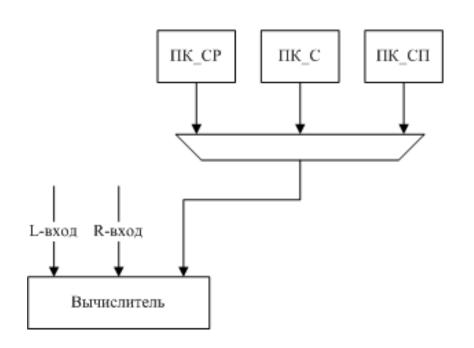

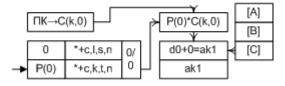

#### Обработка константных данных

Пример инициации ПК\_СР (фильтр Баттеруорта) Тег  $\mathbf{Ot} = \mathbf{r}$

Пример инициации ПК\_С (косинусное ИДПФ)

Тег Ot=s

Пример инициации ПК\_СП (Витерби)

Тег Ot=I

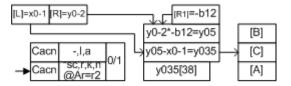

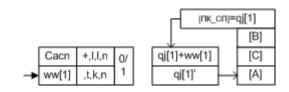

#### Поддержка внутренних и внешних циклов

Переход и проверка окончания цикла (Витерби)

## Имплементация быстрого преобразования Фурье

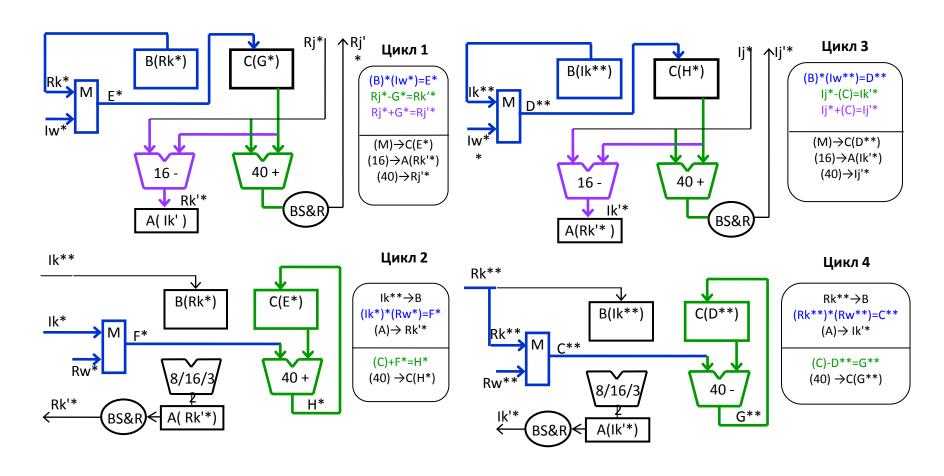

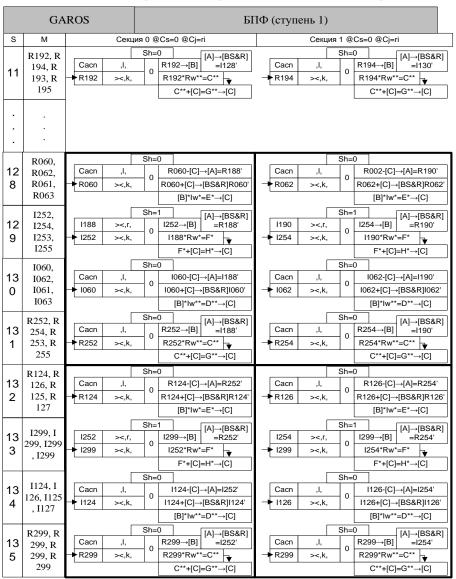

Реализуемый алгоритм — 256-точечный БПФ по основанию 2 с прореживанием по времени.

Суть задачи состоит в вычислении 1024 типовых операций «бабочка». Эффективность реализации БПФ рассчитывалась на основе показателя времени вычисления преобразования (количество логических шагов).

В каждой секции вычисляется четырехцикловая операция «бабочка», поддерживая на аппаратном уровне. При этом за 4 вычислительных шага вычисляется 4 «бабочки». Суммарные временные затраты вычисления 1024 «бабочек» составили 1068 шагов (без учета предварительной загрузки данных).

## Аппаратная поддержка БПФ (команда «бабочка»)

#### Фрагмент граф-капсулы БПФ

### Результаты реализации демонстрационных алгоритмов

| Название алгоритма                      | Кол-во шагов<br>для dsPic30F | Кол-во шагов<br>для РОУ | Коэф. ускорения                               |  |

|-----------------------------------------|------------------------------|-------------------------|-----------------------------------------------|--|

| БПФ2_256                                | ~19000                       | ~1100                   | ~17,2                                         |  |

| Баттеруорт (одна секция)                | 679                          | 299                     | 2,27                                          |  |

| Баттеруорт <sup>*)</sup> (две секции)   | 1360                         | 437                     | 3,11                                          |  |

| Полосовой фильтр (одна полоса)          | 1428                         | 442                     | 3,23                                          |  |

| Натуральный логарифм (вариант 1)        | 36                           | 19                      | 1,89                                          |  |

| Натуральный логарифм х4 (вариант 2)     | 36*4                         | 26                      | 1,38*4                                        |  |

| RASTA фильтр                            | 153                          | 45                      | 3,4                                           |  |

| Экспоненцирование (вариант 1)           | 32                           | 13                      | 2,46                                          |  |

| Экспоненцирование х4 (вариант 2)        | 32*4                         | 20                      | 1,6*4                                         |  |

| Косинусное ИДПФ                         | 36                           | 17                      | 2,12                                          |  |

| Рекурсия Дурбина-Скурра                 | ~800                         | ~300                    | ~2,7                                          |  |

| PLP параметры                           | 144                          | 32                      | 4,5                                           |  |

| PLP параметры <sup>*)</sup>             | 144                          | 30                      | 4,8                                           |  |

| Витерби (расчет решетки для текущего N) | 91*N-143                     | 94*N                    | $\left(1 - \frac{8*N + 143}{94*N}\right) * 4$ |  |

| * модифицированная версия ГАРОС         |                              |                         |                                               |  |

\* модифицированная версия ГАРОС N – количество наблюдений в векторе наблюдений (N>5)

#### Заключение

### В ходе реализации прототипа потоковой рекуррентной архитектуры получены следующие результаты:

- Построены программная имитационная модель, а также аппаратная VHDLмодель

- Найдены технические решения основных проблем, характерных для архитектур из класса потоковых

- В состав реализованного прототипа введены мощные средства поддержки БПФ эталонного алгоритма в классе задач ЦОС. Осуществлена программная реализация данного алгоритма

- Осуществлена реализация программы распознавания слов в среде ГАРОС, как эталона для сравнения с однокристальным исполнением (созданным в рамках совместного проекта с компанией Microchip)

- Произведено программно-аппаратное моделирование комплекса алгоритмов распознавания

- Осуществлена обработка и оценка результатов моделирования, согласно результатам которой, полученные коэффициенты ускорения относительно одноядерного исполнения варьируются в диапазоне от x3 до x17

#### Контакты

Директор: Академик Соколов И. А.

Адрес: Институт проблем информатики Федерального исследовательского центра «Информатика и управление» Российской академии наук (ИПИ РАН), Россия, 119333, Москва, ул. Вавилова, д. 44, корпус 2

- Телефон: +7 (495) 137 34 94

- Fax: +7 (495) 930 45 05

- E-mail: ISokolov@ipiran.ru

- Докладчик: Хилько Д. В., +7(495)381-45-21,

dhilko@yandex.ru