# Разработка RN-моделей аналоговых СФ блоков для верификации смешанных СнК

П.Г. Бобков, К.Р. Брагин

АО "ПКК Миландр", bobkov.p@ic-design.ru

Аннотация — Современные субмикронные системы на кристалле (СнК) содержат все больше аналоговых и функциональных (СФ) аналого-цифровых сложно блоков. Их моделирование на системном уровне средствами SPICE симуляторов занимает огромное количество времени даже при распараллеливании на несколько вычислительных ядер. В связи с чем для функциональной верификации смешанных становится актуальной задача разработки быстрых и точных поведенческих моделей аналоговых блоков. В статье рассмотрен новейший тип таких моделей - real number (RN) модели, значительно превосходящие по скорости моделирования аналоговые Verilog-A модели и являющиеся более точными по сравнению с цифровым Verilog моделями. Кроме того, RN-модели аналоговых СФ блоков могут быть использованы в рамках широко распространенной универсальной верификационной методологии (UVM). В статье проведен сравнительный анализ особенностей синтаксиса цифровой, аналоговой, смешанной и RN-моделей для схемы операционного c цифровым программированием коэффициента усиления. Детально рассмотрен процесс разработки и верификации RN-моделей, описанных на языке Verilog-AMS с применением типа wreal (wire-real), СФ блоков многоканальных LVDS приемника и передатчика c использованием процедуры автоматической калибровки параметров модели.

Ключевые слова — модель, верификация, смешанное моделирование, СФ блок, СнК, Verilog-AMS, RN, wreal, UVM-MS.

#### I. Введение

С повышением степени интеграции современных интегральных микросхем (ИМС) время, затрачиваемое на моделирование и верификацию, оказывает все большее влияние на время выпуска микросхем на рынок. Наличие отклонений в функционировании ИМС может привести к необходимости перезапуска проекта. что требует значительных временных и финансовых Поэтому полнота тестов, обеспечивающих свойств системы на соответствие требованиям спецификации, точность и скорость моделирования играют ключевую роль в процессе ЭТОМ увеличением верификации. При функциональной сложности проектируемых СнК растет количество используемых СФ блоков и аналого-цифрового **УСЛОЖНЯЮТСЯ** алгоритмы взаимодействия. С этой точки зрения на первый план системная верификация. Смешанное моделирование всей системы на транзисторном уровне

занимать несколько недель даже при может использовании высокоскоростных пакетов аналогового моделирования. Анализ предлагаемых решений от различных компаний-производителей САПР [1]-[3] показал, что существует два основных подхода к решению обозначенных проблем верификации. Первый подразумевает усовершенствование программных средств тестирования, а второй заключается в модификации самих методик верификации, а именно обеспечении сквозного маршрута верификации на всех этапах проектирования. При этом в части смешанного моделирования основным направлением является разработка поведенческих моделей аналоговых СФ блоков различного уровня абстракции.

В данной работе рассмотрен тип моделей, ставший наиболее эффективным в области системной верификации, — RN-модели. Их использование значительно сокращает время моделирования, а также открывает широкие возможности для функциональной верификации смешанных СнК, в которых аналоговые блоки представлены RN-моделями. Например, возможно применение современной прогрессивной методологии UVM, использующей для создания тестового окружения и самих тестов библиотеку стандартных классов, разработанную на языках высокого уровня SystemC, SystemVerilog или e [4].

описаны особенности работе преимущества и RN-моделей, ИХ недостатки относительно других уровней абстракции. Проведен сравнительный анализ синтаксиса различных поведенческих моделей на примере операционного усилителя цифровым программированием коэффициента усиления. В заключение рассмотрен процесс разработки и верификации RN-моделей СФ блоков LVDS приемника и передатчика.

## II. МЕТОДЫ РАЗРАБОТКИ МОДЕЛЕЙ АНАЛОГОВЫХ СФ БЛОКОВ. RN-МОДЕЛИ

# А. Уровни абстракции моделей СФ блоков

Общепринятым подходом системной верификации сложных смешанных СнК является иерархически частичная или полная замена аналоговых блоков эквивалентными компактными представлениями.  $\mathbf{B}$ зависимости степени области детализации И применения различают следующие уровни абстракции представлений аналоговых блоков [5].

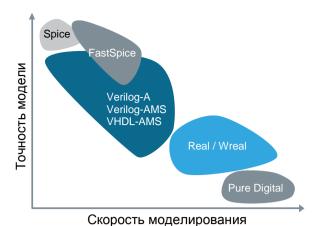

Рис. 1. Зависимость точности моделей СФ блоков от

скорости моделирования [5]

Во-первых, это транзисторный уровень, являющийся эталонным И наиболее точным представлением аналоговых блоков. Электрические схемы в данном случае описываются системой дифференциальных уравнения на основе законов Кирхгофа. Решая эти системы численными методами определяют значения токов и напряжений для каждой электрической цепи и узла. Список цепей может быть дополнен паразитными элементами, экстрагированными из топологии. Моделирование на этом уровне абстракции, выполняемое средствами spice или fast spice симуляторов, является крайне медленным. Возможно применение различных методов ускорения: распараллеливание вычислений на несколько ядер, переменный шаг и т.д.

Во-вторых аналоговые смешанные поведенческие модели, описанные языках на Verilog-A, Verilog-AMS, VHDL-AMS. Поведение аналоговых сигналов описывается в конструкциях analog, моделируется spice симуляторами и носит непрерывный характер. Поведение цифровых логических сигналов описывается конструкциями always и initial, моделируется цифровыми симуляторами и носит дискретный характер. Возможность обращения из аналоговых модулей к цифровым сигналам и наоборот позволяет описывать аналого-цифровой функционал на более понятном уровне. Моделирование в сотни раз быстрее по сравнению с транзисторным уровнем абстракции, что все равно может быть недостаточно для сложных и объемных систем.

В-третьих – полностью цифровые поведенческие модели, описанные на языках Verilog, VHDL, SystemVerilog. Моделирование является наиболее быстрым, однако аналоговые величины интерпретируются только как логические уровни «0» и «1», что является достаточно грубой оценкой и не позволяет описывать большинство аналоговых функций.

В-четвертых, это **RN-модели** – модели в пространстве вещественных чисел, где электрические величины, непрерывные по своей природе,

представлены в виде чисел с плавающей точкой, дискретно изменяющихся во времени на основе дискретных событий. Моделирование использованием RN-моделей не требует решения систем дифференциальных уравнений и выполняется только средствами цифровых симуляторов, поскольку зависимость выходных сигналов напряжений и токов от входных описывается внутри поведенческих модулей простейшими математическими операциями. Поэтому такое моделирование быстрее классического spiceмоделирования на транзисторном уровне в тысячи раз. RN-модели позволяют не только передавать по цепям данные в виде набора логических состояний («0», «1», высокоимпедансное состояние Z, неопределенное состояние X), но и имитировать передачу значений напряжений или токов электрических сигналов, представляя их в виде чисел с плавающей точкой. Этот формат поддерживается следующими языковыми стандартами:

- тип wreal в Verilog-AMS;

- тип real в VHDL;

- тип real в SystemVerilog;

- тип real в е.

**Тип wreal** определен только в стандарте языка Verilog-AMS [6], однако в контексте RN-моделей разница между типом wreal в Verilog-AMS и типом real в остальных языках незначительна. Основные отличия описаны в [6]. Зависимость точности моделей от скорости моделирования приведена на рис. 1 для различных уровней абстракции.

# В. Применение RN-моделей для верификации СнК

Отличительная особенность RN-моделей — совместимость с языками верификации высокого уровня такими, как SystemVerilog и e, которые используется для создания тестов и тестового окружения. Это открывает широкие возможности в области верификации CнK.

Метрическая методология верификации (MDV – Metric Driven Verification) активно применяется в цифровом маршруте верификации и подразумевает запуск большого количества циклов моделирования. Добавление в данную методологию RN-моделей аналоговых СФ блоков позволяет верифицировать смешанные СнК с аналоговыми метриками в цифровом маршруте верификация (MS-MDV) [7]. Расширенная методология поддерживает следующие методы: разработка верификационного плана для аналоговых блоков; разработка направленных или случайноограниченных тестов (constraint random testing); измерение аналоговых параметров (напряжения, токи, частоты, усиление, временные характеристики и т.д.); автоматическая проверка и контроль аналоговых свойств средствами языков утверждений PSL (Property Specification Language) и SVA (SystemVerilog Assertion); сбор и анализ полноты аналоговых метрик покрытия тестами (coverage) покрытие кода, функциональное покрытие.

Использование перечисленных процедур в рамках универсальной верификационной методологии UVM

расширяет возможности тестирования [8]. Такие ключевые особенности UVM, как поддержка ведущими САПР стандартизация И моделирование на уровне транзакций (Transaction Level Modeling), внутренняя база данных, средства диагностики выполнения тестов и возможность многократно компоненты **UVM** использовать (драйверы, мониторы и т.д.) для других проектов, делает эту методология универсальным инструментом верификации. Расширенная структурированная библиотека классов UVM-MS [9], [10] позволяет создавать единую верификационную для функционального тестирования применимую аналоговых СФ блоков. Такое тестовое окружение представлено в виде Verilog-AMS или SystemVerilog модуля на верхнем уровне, который содержит в себе, во-первых, верификационные компоненты UVM-MS библиотеки, написанные на SystemVerilog или e, и, во-вторых, само тестируемое устройство, аналоговые которого представлены эквивалентными RN-моделями. Примеры использования UVM-MS методологии для верификации систем, в которых различные аналоговые СФ блоки заменены RNмоделями, приведены в [11]-[13].

#### III. СРАВНЕНИЕ МОДЕЛЕЙ НА ПРИМЕРЕ ОУ

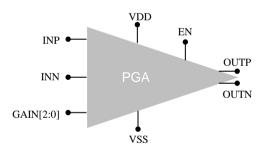

На примере операционного усилителя (ОУ) с цифровым программированием коэффициента усиления, изображенного на рис. 2, проведем сравнение синтаксических особенностей следующих моделей ОУ (табл. 1):

- цифровая модель на Verilog;

- аналоговая модель на Verilog-A;

- смешанная модель на Verilog-AMS;

- RN-модель на Verilog-AMS.

Рис. 2. Модель операционного усилителя с цифровым программированием коэффициента усиления

Основной функционал описываемой модели ОУ: коэффициент усиления контролируется трех-битной шиной GAIN; дифференциальный выходной сигнал центрирован относительно середины питания; если сигнал разрешения EN не равен "1", выход находится в Z-состоянии; если напряжения VDD и VSS не соответствуют требуемым уровням, выход равен 0.

**Цифровая модель** описывается только в терминах цифрового домена: дисциплина logic, блоки always/initial. В этом случае аналоговые сигналы напряжений и токов представлены «0» и «1», что сильно ограничивает возможности модели. Для цифровой

модели ОУ это значит, что, во-первых, напряжения питания и земля определяются как логические уровни, во-вторых, передаточная функция есть прохождение входного сигнала на выход, что не совсем корректно и лишь частично соответствует реальной схеме ОУ (листинг 1).

Листинг 1. Фрагмент цифровой модели

Аналоговая модель, наоборот, описывается в аналогового домена: дисциплина терминах electrical, блок analog. Дискретные цифровые сигналы в данном случае представляются непрерывные величины, что значительно замедляет скорость моделирования, поскольку расчет каждого изменения логического состояния в данном случае большого количества шагов. конвертирования дискретных значений в непрерывные используется оператор transition. Для присвоения посредством функций I() используется оператор <+. Кроме того, в рамках аналоговой модели нет возможности напрямую обращаться к логическому состоянию цифровых сигналов, поэтому требуется дополнительно описывать некоторые операции преобразования (макрос define в Листинге 2).

Листинг 2. Фрагмент аналоговой модели

```

electrical OUTP, OUTN, INP, INN, VDD, VSS, EN;

electrical [2:0] GAIN;

'define L(pin) (V(pin,VSS) > V(VDD,VSS)/2)

analog begin

Active = `L(EN)==1 && V(VDD,VSS)>=2.0;

Gout = transition(`L(EN)? 1/Rout : 1n,0,Tr);

I(OUTP,VSS) <+ (V(OUTP,VSS) - (Vcml+Vdiff/2))*Gout;

I(OUTN,VSS) <+ (V(OUTN,VSS) - (Vcml-Vdiff/2))*Gout;

end

```

Смешанная модель сочетает в себе свойства аналоговых и цифровых доменов, за счет чего возможно обращение к цифровым сигналам внутри блока analog, и наоборот – обращение к аналоговым сигналам внутри блоков always/initial (листинг 3). Синтаксис таких моделей наиболее понятен. Однако смешанные модели не позволяют добиться существенного ускорения моделирования, достаточного для их использования в цифровом маршруте верификации.

Листинг 3. Фрагмент смешанной модели

```

electrical OUTP, OUTN, INP, INN, VDD, VSS;

logic EN;

logic [2:0] GAIN;

analog begin

Active = (EN===1'b1) && V(VDD,VSS)>=2.0;

Gout = transition((EN===1'b1) ? 1/Rout : ln,0,Tr);

I(OUTP,VSS) <+ (V(OUTP,VSS) - (Vcml+Vdiff/2))*Gout;

I(OUTN,VSS) <+ (V(OUTN,VSS) - (Vcml-Vdiff/2))*Gout;

end</pre>

```

RN-модель, описанная на языке Verilog-AMS, использует переменные типа wreal. Сигналы. объявленные в смешанной и аналоговой моделях как electrical, в RN-модели объявлены как wreal. При wreal не является какой-либо дисциплиной, это тип переменной, который, по умолчанию, так же как типы wire и reg, относится к Но в отличии от дисциплине logic. интерпретируется не как бит или шина, а как число с плавающей точкой, аналогично типу Переменные, являющиеся входными/выходными портами модуля, могут быть объявлены как wreal, для выходных портов при этом необходимо использовать непрерывного присваивания оператор assign. Несмотря на то, что в основном такие сигналы являются аналоговыми по своей природе, применение функций V() и I() не требуется, работать с ними можно внутри блоков always/initial. В отличии от типа real, тип wreal поддерживает Z и X состояния. Для этого в Verilog-AMS предусмотрены константы wrealZState и `wrealXState, соответственно (Листинг 4).

Листинг 4. Фрагмент RN-модели

ОУ описанной модели нагрузочное сопротивление и время нарастания выходного сигнала не учитываются. Однако данный недостаток легко устраняется настройкой параметров интерфейсных элементов R2E (из типа real в тип electrical) и E2R (из типа electrical в тип real), которые генерируются автоматически в процессе моделирования смешанных схем, если RN-модель взаимодействует с электрической схемой или другой аналоговой моделью. Для RNмоделей отсутствует проблема сходимости, зачастую присущая аналоговым моделям. Также разрешен конфликт нескольких драйверов: возможно соединения нескольких выходов между собой с применением функций разрешения.

Результатом моделирования RN-моделей является набор чисел с плавающей точкой. Уровень детализации и точность модели настраивается путем выбора шага дискретизации, определяющего количество точек, в которых происходит расчет нового значения. Этот шаг задается либо непосредственно в синтаксисе самой модели, либо передается в интерфейсных элементах параметрами vdelta и idelta. Они могут быть заданы константами, либо параметрами, рассчитываемыми на основе свойств системы — максимальная амплитуда сигналов, напряжение питания и т.д.

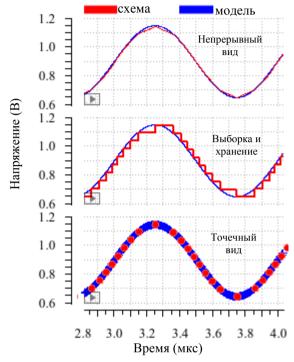

Различия электрических сигналов и сигналов типа wreal наглядно продемонстрированы на примере простого аналогового буфера на рис. 3, где показан

выходной синусоидальный сигнал для трех типов представлений результатов моделирования. Видно, что графики для схемы и модели достаточно идентичны несмотря на то, что для RN-модели потребовалось значительно меньше расчетных точек. Надо отметить, что представление в виде непрерывной кривой подходит для визуализации сигналов произвольной формы, а тип выборка и хранение – для сигналов прямоугольной формы.

Рис. 3. Выходной сигнал аналогового буфера – сравнение схемы и RN-модели для разных типов представления графика

## IV. РАЗРАБОТКА И ВЕРИФИКАЦИЯ RN-МОДЕЛЕЙ СФ БЛОКОВ LVDS ПРИЕМНИКА И ПЕРЕДАТЧИКА

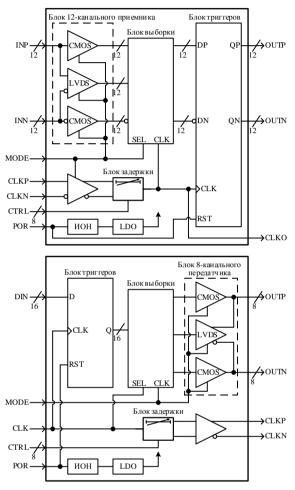

СФ блок приемника (рис. 4) предназначен для приема LVDS сигналов данных и синхросигнала с аналого-цифрового преобразователя (АЦП) обеспечивает их трансфер в блок цифровой обработки сигнала. Блок состоит из двух симметричных каналов, обеспечивающих одновременную обработку данных с двух АЦП. СФ блок передатчика (рис. 4б) предназначен для передачи обработанных данных и синхросигнала внешнему устройству. В состав СФ блоков входят: непосредственно схемы LVDS приема и передачи сигналов; блок регулируемой задержки синхросигнала; выборки режима; блоки триггеров синхронного приема-передачи данных; источник опорных напряжения и токов; регулятор напряжения с низким падением напряжения для запитывания блока задержки стабильным уровнем питания.

Разработанные RN-модели обеспечивают воспроизведение всех временных характеристик и формы выходного сигнала каждого из блоков с учетом заложенных режимов работы. Соблюдены все

требования спецификации, предъявляемые к уровням входных и выходных напряжений. Учтено влияние технологического разброса углов, разброса напряжений питания и разброса температур для типовых и краевых (максимальное и минимальное быстродействие) случаев. Разработанные RN-модели имеют следующий функционал, отличающий их от цифровых моделей:

- воспроизведение LVDS-режима;

- учет влияния напряжения питания на уровни напряжений выходных сигналов;

- воспроизведение регулятора напряжений.

Рис. 4. Структурная схема СФ блоков LVDS и КМОП приемника (а) и передатчика (б)

Другая особенность – применение процедуры калибровки параметров модели, проводимой в среде Cadence Virtuoso Schematic Model Generator. Данная процедура позволяет точно описать функционал сложных блоков путем подгона параметров модели. Из результатов моделирования электрической схемы выгружаются данные о зависимости выходов блока от его входов в виде табличного файла, который затем используется в коде модели с помощью функции \$table\_model. Такая процедура применена для разработки RN-модели подблока регулируемой задержки синхросигнала, предназначенного для сдвига входного тактового сигнала на величину задержки, определяемой по заданному алгоритму на основе

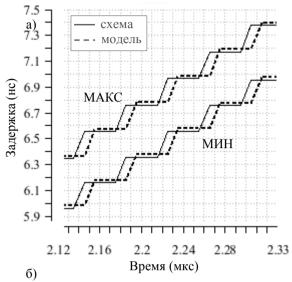

состояния управляющей 8-битной шины CTRL. Фрагмент результатов временного моделирования приведен на рис. 5. Шина CTRL меняет свое состояние последовательно от 0 до 255 каждые 30 нс. С учетом краевых случаев МИН (минимальная задержка) и МАКС (максимальная задержка), обусловленных технологическим разбросом, ошибка модели по сравнению со схемой не превышает 10 пс, что составляет 0.25% от максимальной частоты синхросигнала 250 МГц.

Рис. 5. Параметр задержки подблока регулируемой задержки синхросигнала с учетом технологического разброса

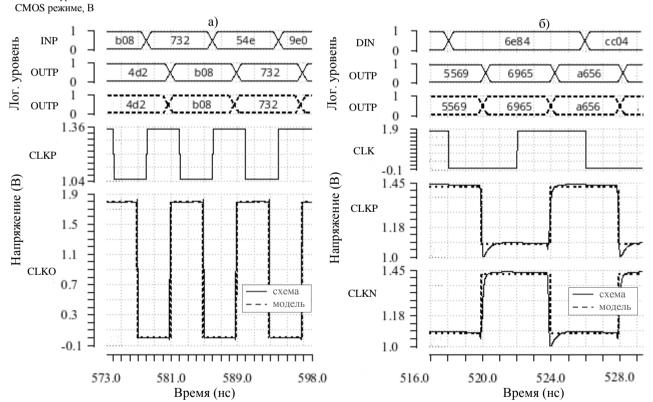

Верификация разработанных моделей проводилась в среде проектирования Cadence Virtuoso: на вход RNмодели и электрической схемы СФ блока подаются тестовые воздействия, в едином тестовом окружении смешанное моделирование, сравниваются результаты. На рис. 6а представлен фрагмент результатов моделирования СФ блока приемника в LVDS-режиме. На входе INP - 12-битная псевдослучайная последовательность данных, на входе СLКР синхросигнал частотой 250 МГц. На выходе OUTP - принятые данные, синхронизованные с задержанной выходной частотой CLKO. На рис. 6б представлен фрагмент результатов моделирования СФ блока передатчика в LVDS-режиме. На входе DIN -16-битная псевдослучайная последовательность данных, на входе CLK - синхросигнал частотой 250 МГц. На выходе OUTP - обработанные данные, синхронизованные с задержанной выходной частотой CLKP/CLKN. Сравнение результатов верификации spice представления и разработанных RN-моделей СФ блоков представлено в табл. 1. Максимальное отклонение временных характеристик выходных сигналов моделей от схемы составляет несколько пикосекунд и не превышает 2.5%. При этом общее время моделирования моделей более чем в 3500 раз моделирования схемы на чем время транзисторном уровне spectre-APS симулятором с распараллеливанием на 10 вычислительных ядер.

режиме, нс

Задержка CLKP/CLKN

относительно СLК, нс

выходное напряжение

Выходное напряжение

Дифференциальное

в LVDS режиме, мВ

высокого уровня в

| Соответствие спецификации                                            |                    |                         |                         |                    | Общая ошибка моделей |                                                                                                                                                                                                                                              |                                     |                                                                   |                                        |  |

|----------------------------------------------------------------------|--------------------|-------------------------|-------------------------|--------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------|----------------------------------------|--|

| Параметр                                                             | По ТЗ              | Схема                   | и<br>RN-<br>модель      | Усло<br>вия        |                      | Тип<br>Максимальная<br>Ү-ошибка, %                                                                                                                                                                                                           | Значение < 0.1                      |                                                                   | Описание<br>нение уровней<br>кения     |  |

| Задержка OUTP/OUTN относительно CLKO,                                | Приемни<br>≤ 1     | 0.091<br>0.134          | 0.089<br>0.132          | мин<br>тип         |                      | Максимальная<br>Х-ошибка, %                                                                                                                                                                                                                  | < 2.5                               | Отклонение временных<br>характеристик при<br>максимальной частоте |                                        |  |

| нс<br>Задержка СLKО<br>относительно                                  | ≤ 10               | 0.174<br>2.190<br>2.754 | 0.172<br>2.189<br>2.756 | макс<br>мин<br>тип | _                    | Этап                                                                                                                                                                                                                                         | Время моделирования  RN- Примечание |                                                                   |                                        |  |

| СLКР/СLКN, нс Выходное напряжение высокого уровня, В                 | ≥ 1.62             | 3.585<br>1.79           | 3.585<br>1.8            | макс<br>—          |                      | Лоиск<br>начальных                                                                                                                                                                                                                           | 34.5                                | модель<br>0.1                                                     | - при максимальной                     |  |

| Выходное напряжение низкого уровня, В                                | ≤ 0.18<br>Передатч | 0.01                    | 0                       | -                  | •                    | условий, с<br>Временной                                                                                                                                                                                                                      | 2597.2                              | 0.7                                                               | частоте - распараллеливание на 10 ядер |  |

| Задержка ОUTP/OUTN<br>относительно<br>CLKP/CLKN в CMOS<br>режиме, нс | ≤1                 | 0.040<br>0.051<br>0.311 | 0.041<br>0.049<br>0.311 | мин<br>тип<br>макс | -                    | анализ 1 мкс, с       9.7         Условия моделирования:       - мин VDD=1.98B, T=-60°C, Corner=ff         - тип VDD=1.8B, T=+27°C, Corner=st       - макс VDD=1.62B, T=+125°C, Corner=ss         Все функциональные режимы работы и парамет |                                     |                                                                   |                                        |  |

| Задержка OUTP/OUTN относительно CLKP/CLKN в LVDS                     | ≤ 1                | 0.076<br>0.223<br>0.560 | 0.076<br>0.223<br>0.562 | мин<br>тип<br>макс |                      |                                                                                                                                                                                                                                              |                                     |                                                                   |                                        |  |

мин

тип

макс

мин

тип

макс

1.341

1.762

2.378

350

350

350

3.3

1.339

1.765

2.383

330

352

375

3.28

≤ 10

250

-460

$\ge 2.97$

Все функциональные режимы работы и параметры моделей соответствуют электрической схеме и требованиям спецификации, за исключением тока потребления. Также не учитывается резистивноемкостной характер нагрузки выходных сигналов модели - связанная с этим скорость нарастания сигналов задается непосредственно в интерфейсных элементах.

Рис. 6. Результаты моделирования СФ блоков приемника (а) и передатчика (б) в LVDS-режиме

Все функциональные режимы работы и параметры моделей соответствуют электрической схеме

требованиям спецификации, за исключением тока потребления. Также не учитывается резистивноемкостной характер нагрузки выходных сигналов модели — связанная с этим скорость нарастания сигналов задается непосредственно в интерфейсных элементах.

#### V. ЗАКЛЮЧЕНИЕ

Применение поведенческих моделей аналоговых блоков для верификации сложных смешанных СнК является широко распространенной практикой. В статье рассмотрен один из наиболее эффективных типов представления аналоговых блоков - RN-модели, объединяющие достоинства как аналоговых моделей точность, так и цифровых моделей - скорость моделирования. RN-модели представляют напряжения токи в виде чисел с плавающей поддерживаются такими языковыми стандартами как Verilog-AMS, SystemVerilog, VHDL, е и не требуют вычислительно затратных spice симуляторов, они могут быть промоделированы только средствами цифровых симуляторов. За счет этого возможно применение современных методологий верификации таких, как UVM-MS.

Сравнение ключевых особенностей синтаксиса и отличий моделей различного уровня абстракции проведено на примере схемы операционного усилителя цифровым программированием коэффициента усиления. На языке Verilog-AMS с применение типа wreal и процедуры калибровки параметров модели разработаны RN-модели СФ блоков LVDS и КМОП приемника и передатчика, используемые в составе микросхемы обработки данных. Верификация моделей они позволяют характеризовать что функционал блоков и учесть большинство аналоговых свойств - поведение при включении/выключение питания, функции приёма-передачи со сложным механизмом формирования регулируемой задержки, влияние технологического разброса, поддержка LVDSрежимов работы, влияние напряжений питания на уровни выходных сигналов. Режимы работы и характеристики моделей удовлетворяют требованиям спецификации и соответствуют электрической схеме на транзисторном уровне.

Применение подобных RN-моделей позволяет выполнять моделирование сложных высокоинтегрированных схем смешанного сигнала с высокой скоростью и точностью, что значительно сокращает время проектирования.

#### Литература

- Balasubramanian S., Hardee P. Solutions for Mixed-Signal SoC Verification Using Real Number Models // Cadence Design Systems.

- [2] Nunn G., Delguste F., Khan A., Verma A., Geden B. Using Digital Verification Techniques on Mixed-Signal SoCs with CustomSim and VCS // Synopsys.

- [3] Complex Mixed-Signal Functional Verification with Questa ADMS // Mentor Graphics.

- [4] Chen J., Henrie M., Mar M., Nizic M., Bailey B. Mixed-Signal Methodology Guide. Advanced Methodology for AMS IP and SoC Design, Verification, and Implementation // Cadence Design Systems. August 2012.

- [5] Verilog-AMS Real Valued Modeling Guide // Cadence Design Systems, Product Version 15.2, Feb 2016.

- [6] Verilog-AMS Language Reference Manual. Analog & Mixed-Signal Extensions to Verilog HDL. // Accellera. Version 2.4. June 2014.

- [7] Khan N., Kashai Y., Fang H.. DVCon Metrics Driven Verification of Mixed Signal Design. 2011.

- [8] Universal Verification Methodology (UVM) 1.2 Class Reference // Accellera, June 2014

- [9] Bishnupriya B., John D., Gary H., Nick H., Yaron K., Neyaz K., Zeev K., Efrat S. Advanced Verification Topics // Cadence Design Systems, 2012.

- [10] Rosenberg, S. and Meade, K. A Practical Guide to Adopting the Universal Verification Methodology (UVM) // Cadence Design Systems, 2010.

- [11] Khan. N., Kashai Y. From Spec to Verification Closure: a case study of applying UVM-MS for first pass success to a complex Mixed-Signal SoC design // Cadence Design Systems.

- [12] Das P. Exploration of Real Value Modelling for Complex Mixed Signal Verification. June 2015.

- [13] Khan N. Mixed Signal Verification of Dynamic Adaptive Power Management in Low Power SoC // Cadence Design Systems.

# Development of Real Number Models of Analog IP Blocks for Mixed Signal SoC Verification

P.G. Bobkov, K.P. Bragin

JSC "ICC Milandr", bobkov.p@ic-design.ru

Abstract - Due to increasing complexity of very-large-scale integration (VLSI) circuits, standard SPICE and Fast SPICE full chip simulation cannot deliver a verification arrangement on time. This leads to growing necessity of methodology for accurate and fast verification of mixed signal (AMS) designs.

The article focuses on modern approaches based on using behavioral model of IP blocks for mixed signal system-on-chip (SoC) verification on system level. A novel approach for AMS simulation, which uses Real Number Modeling (RNM) concepts, is considered. RNM is a special technique used to model electrical signals by representing them as floating-point real values based on discrete event. It i allows to describe analog block as a signal-flow model and then to simulate it in a digital solver. RNM is available in the Verilog-AMS, SystemVerilog, VHDL, etc. So complex mixed signal IP blocks

can be integrated into common verification environment as real-number models, which can be used in metric-driven verification bringing its techniques such as randomization, coverage and asserts.

Developed behavioral models of typical analog block with simple digital control logic – programmable gain amplifier – are presented in this article in terms of different abstract levels of abstraction. Syntactic features, main advantages and disadvantages are analyzed in comparison with RN-model in Verilog-AMS language, named wreal model. Its key benefits are a much faster simulation speed relative to analog models and higher accuracy relative to digital models. This significantly reduces the verification time for mixed signal full chip simulations.

In addition, the advantages of this approach are illustrated by taking complex analog IP blocks of CMOS/LVDS receiver and transmitter as examples, which are parts of a real SoC design. RN-models using wreal type have been designed successfully with comparison of its spice electrical model. The calibration procedure was used to adjust the model parameters within Cadence Virtuoso design environment Schematic Model Generator (SMG) and AMS Design & Model Validation (amsDmv). The functionality of IP has been verified by using different functionality check test cases. Developed RN models makes it possible to behaviorally model analog effects, such as supply ramp behavior, PVT variations, complex mechanism for the formation of adjustable delay. output impedance, influence of supply voltage on output CMOS and LVDS levels, shutdown behavior using event driven digital simulators.

RNM shown in this work is compatible with existing digital verification techniques. Modern UVM methodology can be extended for supporting analog verification. The extended methodology, named UVM-MS, include verification planning for analog blocks, analog signal generation, checking and assertion techniques for analog properties and analyzing analog functional coverage. These features in combination with high-level modeling of analog circuits using RNM are the

powerful reusable instruments for the complex mixed signal IP level and SoC level verification.

Keywords — model, verification, mixed signal simulation, IP, SoC, Verilog-AMS, RNM, wreal, UVM-MS.

#### REFERENCES

- [1] Balasubramanian S., Hardee P. Solutions for Mixed-Signal SoC Verification Using Real Number Models // Cadence Design Systems.

- [2] Nunn G., Delguste F., Khan A., Verma A., Geden B. Using Digital Verification Techniques on Mixed-Signal SoCs with CustomSim and VCS // Synopsys.

- [3] Complex Mixed-Signal Functional Verification with Questa ADMS // Mentor Graphics.

- [4] Chen J., Henrie M., Mar M., Nizic M., Bailey B. Mixed-Signal Methodology Guide. Advanced Methodology for AMS IP and SoC Design, Verification, and Implementation // Cadence Design Systems. August 2012.

- [5] Verilog-AMS Real Valued Modeling Guide // Cadence Design Systems, Product Version 15.2, Feb 2016.

- [6] Verilog-AMS Language Reference Manual. Analog & Mixed-Signal Extensions to Verilog HDL. // Accellera. Version 2.4. June 2014.

- [7] Khan N., Kashai Y., Fang H.. DVCon Metrics Driven Verification of Mixed Signal Design. 2011.

- [8] Universal Verification Methodology (UVM) 1.2 Class Reference // Accellera, June 2014

- [9] Bishnupriya B., John D., Gary H., Nick H., Yaron K., Neyaz K., Zeev K., Efrat S. Advanced Verification Topics // Cadence Design Systems, 2012.

- [10] Rosenberg, S. and Meade, K. A Practical Guide to Adopting the Universal Verification Methodology (UVM) // Cadence Design Systems, 2010.

- [11] Khan. N., Kashai Y. From Spec to Verification Closure: a case study of applying UVM-MS for first pass success to a complex Mixed-Signal SoC design // Cadence Design Systems.

- [12] Das P. Exploration of Real Value Modelling for Complex Mixed Signal Verification. June 2015.

- [13] Khan N. Mixed Signal Verification of Dynamic Adaptive Power Management in Low Power SoC // Cadence Design Systems.