# Метод экстракции паразитных сопротивлений для раннего анализа цепей питания с нерегулярной топологией

К.К. Малинаускас

Silvaco Inc., kostas.malinauskas@silvaco.com

Аннотация — В работе представлен оригинальный метод экстракции паразитных сопротивлений плоских проводников со сложной топологией и построения эквивалентных резистивных схем, основанный на применении диаграммы Вороного и медиального осевого преобразования. Построенные электрические схемы компактны и в то же время легко отображаются на исходную геометрию трассировки, что удобно для моделирования цепей питания с подробной визуализацией падений напряжения. Реализация метода показала высокую эффективность при достаточной точности экстракции в промышленной системе анализа целостности питания на ранних этапах проектирования.

*Ключевые слова* — экстракция паразитных сопротивлений, целостность питания, падение напряжения, диаграмма Вороного, медиальная ось.

#### I. Введение

Обеспечение целостности питания (power integrity) является существенной частью проектирования современных электронных устройств [1]-[2]. Ведь стабильность работы и быстродействие транзисторов зависят от напряжений, переданных по сетям питания, сложность которых постоянно растёт.

Анализ падений напряжений (IR-drop) на ранних стадиях физического проектирования позволяет заблаговременно принимать правильные решения и избежать массы ошибок до окончательной верификации. Средства раннего анализа должны быть быстрыми и достаточно точными, что является непростой задачей, учитывая растущую степень интеграции схем. Востребована детальная визуализация результатов анализа на исходной топологии в виде карты падений напряжения, позволяющая локализовать проблемные участки.

Существенным этапом раннего IR-drop анализа является быстрая экстракция эквивалентных схем со сосредоточенными паразитными сопротивлениями с разумной точностью. Их дальнейшее статическое и динамическое моделирование предполагает решение соразмерных систем линейных уравнений. Поэтому для сокращения времени анализа важно, чтобы экстрагированные схемы были предельно компактными. В совокупности требования к экстракции становятся трудновыполнимыми, если цепи питания имеет сложную нерегулярную топологию (неоднородные ширины и направления, разнообразие форм проводников), что до сих пор встречается в трассировке некоторых СБИС и печатных

плат. Несмотря на общую тенденцию к упрощению геометрий, связанную с ограничениями современной фотолитографии, трассировка в различных направлениях (обычно с шагом 90°, 60°, или 45° [3]) по-прежнему допустима в верхних слоях металлизации и на старых технологических процессах. Неоднородные ширины и изломы шин питания появляются в системах на кристалле (system on chip) при компоновке блоков с разными архитектурами. В аналоговых схемах с большой долей ручного проектирования могут возникать и более экзотические формы проводников.

Большинство известных подходов к экстракции сопротивлений можно разделить на две группы: условно точные и эвристические (см. [1], [4]). В первых сопротивления вычисляются путём численного решения уравнений электромагнетизма (метод конечных разностей, метод конечных элементов, метод граничных элементов, методы Монте-Карло) [5]. Такая экстракция наиболее точная, но требует применения мелких сеток для проводников сложной формы, что ведёт к росту вычислений и необходимой памяти и непрактично для быстрого анализа больших схем. Эквивалентные схемы часто редуцируют, но при этом теряется их детальное соответствие исходной топологии проводника [6]. Эвристические подходы используют аналитические формулы сопротивлений для предопределённых шаблонов, на которые разбиваются проводники [7]-[9]. Точность экстракции зависит от способа разбиения, который может быть нетривиальным и неоднозначным, а применимость ограничена набором шаблонов (как правило прямоугольной формы).

В данной работе предлагается новый эвристический метод экстракции паразитных сопротивлений плоских проводников произвольной многоугольной формы, основанный на применении диаграммы Вороного и медиального осевого преобразования. Геометрические определения приведены в части ІІ данной статьи. В части ІІ предлагается детерминированный способ построения резистивной схемы оптимального (линейного) размера, позволяющий подробно моделировать падения напряжений в различных участках исходной топологии. В части ІV обсуждается применение предложенного метода для анализа падений напряжения. Часть V посвящена результатам практического использования метода, также в ней обозначены дальнейшие направления работы.

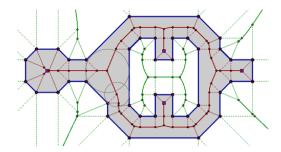

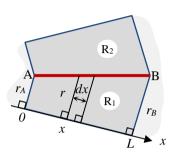

Рис. 1. Диаграмма Вороного и медиальная ось многоугольника (внутренние сплошные линии)

#### II. ГЕОМЕТРИЧЕСКИЕ ОПРЕДЕЛЕНИЯ

Диаграммой Вороного VD(S) (ДВ) для набора плоских объектов S называется разбиение плоскости на ячейки Вороного VR(s) — локусы точек, расположенных ближе к одному из объектов  $s \in S$ , чем к остальным [10]. ДВ является графом на плоскости, вершины которого равноудалены от трёх или более объектов, а рёбра суть участки биссектрис между соседними объектами.

Диаграммой Вороного VD(P) простого многоугольника P называется диаграмма для отрезков — сторон многоугольника. Для простоты построения каждая сторона представляется тремя объектами — открытым отрезком и концевыми точками [11]. Тогда в евклидовой метрике все рёбра имеют прямолинейную либо параболическую форму. Биссектрисы между открытыми отрезками и их концами порождают вспомогательные рёбра Вороного (пунктирные линии на рис. 1).

Медиальная (срединная) ось простого многоугольника (medial axis) — это геометрическое место точек — центров окружностей, содержащихся внутри многоугольника и касающихся его границы минимум в двух точках [11]. Радиусы окружностей задают радиус-функцию (radius function) вдоль оси. Срединная ось совместно с радиус-функцией называется медиальным осевым преобразованием (medial axis transform, MAT). Его можно получить из диаграммы Вороного путём удаления её внешней относительно многоугольника части и вспомогательных рёбер (рис. 1). Определения применимы к фигуре с дырками, если её внешний и внутренние контуры — простые многоугольники.

# III. МЕТОД ЭКСТРАКЦИИ ПАРАЗИТНЫХ СОПРОТИВЛЕНИЙ С ИСПОЛЬЗОВАНИЕМ ДВ

#### А. Основная идея

Будем считать, что все геометрии в отдельных проводящих слоях объединены в непересекающиеся простые многоугольники (возможно с дырками). Эта классическая задача вычислительной геометрии решается за время  $O(n \log n)$ , например, методом заметания плоскости (сканирующей линии) [10].

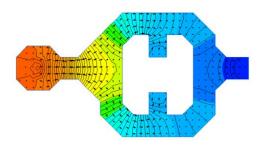

Заметим, что направления линий электрического тока между отдалёнными контактами в одномерном приближении примерно соответствуют направлениям линий медиальной оси (см. рис. 1 и рис. 2). Данное наблюдение легло в основу метода экстракции сопротивлений, включающего в себя следующие этапы.

Рис 2. Эквипотенциальные поверхности и направления электрического тока в проводнике сложной формы

- 1. Построение ДВ и медиального осевого преобразования многоугольного проводника.

- 2. Назначение терминальных вершин на оси.

- Декомпозиция многоугольника вдоль медиальной оси и построение резистивной схемы.

- 4. Вычисление сопротивлений элементов схемы.

ДВ, а значит, и медиальную ось можно построить за время  $O(n \log n)$  с использованием O(n) памяти, где n – число сторон многоугольника. В частности, широко применяется алгоритм заметания плоскости [10].

Назначим терминальные вершины в точках медиальной оси, ближайших к центрам контактных площадок (межслойных переходов). Если ближайшая точка попадает внутрь ребра, то ребро разбивается на части, и новая вершина степени 2 становится терминальной.

## В. Декомпозиция многоугольного проводника и построение эквивалентной схемы

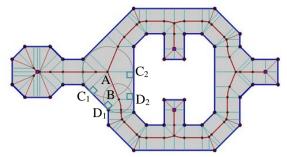

Каждое ребро АВ медиальной оси отделяет ячейки Вороного пары объектов границы многоугольника –  $s_1$ и  $s_2$  (рис. 3). Соединим концы A и B ребра с ближайшими точками на  $s_1$  и  $s_2 - C_1$ ,  $D_1$ ,  $C_2$ ,  $D_2$ . Причём  $C_i$  и  $D_i$ различаются, если  $s_i$  – сторона многоугольника, и совпадают, если  $s_i$  – вогнутая вершина. Ассоциируем с каждым ребром АВ в общем случае шестиугольник  $AC_{1}D_{1}BD_{2}C_{2}$ . Получим разбиение проводника на неперекрывающиеся элементарные многоугольники (рис. 3). Причём их смежные отрезки являются радиусами вписанных в проводник окружностей и приблизительно соответствуют эквипотенциальным линиям при типовом расположении контактов (достаточном их удалении друг от друга). Отрезки  $AC_1$  и  $AC_2$  и отрезки  $BD_1$ и  $BD_2$  равновелики, их длины равны значениям радиусфункции  $r_A = r(A)$  и  $r_B = r(B)$ .

Эквивалентную схему построим естественным образом из медиальной оси и декомпозиции проводника на её основе (рис. 4). А именно, вершины и рёбра оси станут узлами и сосредоточенными сопротивлениями схемы. Приближённая модель предполагает, что границы смежных многоугольников декомпозиции эквипотенциальны и являются протяжёнными контактами элементарных резисторов. При этом вогнутые вершины исходного проводника «выкалываются», чтобы исключить замыкание смежных контактов. Рёбра оси, примыкающие к границе проводника, исключаются из схемы

Рис. 3. Декомпозиция проводника вдоль медиальной оси

Рис. 4. Граф резистивной схемы

Рис. 5. Элементарный проводник: две трапеции

Рис. 6. Элементарный проводник: два треугольника

Рис. 7. Элементарный проводник: «трапеция» и «треугольник»

как имеющие бесконечное сопротивление, а соответствующие элементарные области считаются эквипотенциальными. Отметим, что построенная схема, как и медиальная ось, имеет линейный размер: O(n+m), где n – число сторон многоугольника, m – число контактов.

#### С. Вычисление сопротивлений

Рассмотрим элементарный проводник, порождённый ребром медиальной оси AB со значениями радиусфункции  $r_A$  и  $r_B$  в концевых точках и разбиваемый ребром на две части  $C_1D_1BA$  и  $D_2C_2AB$  (рис. 3). Возможны конфигурации: 1) две трапеции, 2) два треугольника, 3) «трапеция» и «треугольник» с общей параболической стороной. Оценим сопротивление каждой конфигурации, используя следующие допущения:

- а) проводник есть однородная тонкая плёнка с удельным сопротивлением  $\rho = 1 \, \text{Ом/квадрат}$  (опустим в формулах);

- б) сопротивление элементарного проводника эквивалентно сопротивлению его частей, соединённых параллельно:  $R=R_1 \parallel R_2=R_1R_2/(R_1+R_2)$ .

#### 1) Две трапеции

Симметричные трапеции образуются, если ребро медиальной оси AB порождено двумя сторонами исходного многоугольника. Оценим сопротивление путём интегрирования вдоль оси x, проходящей через одну из сторон (рис. 5). Проекция точки A задаёт начало отсчёта x=0.

Из свойств подобия следует, что радиус-функция изменяется вдоль ребра AB линейно:

$$r = r_A + \frac{r_B - r_A}{L} x,$$

где  $L=\sqrt{|A{\bf B}|^2-(r_{\!\!B}-r_{\!\!A})^2}$  – длина проекции ребра AB на границу исходного проводника. Тогда

$$dR_{1} = \frac{dx}{r} = \frac{dx}{r_{A} + \frac{r_{B} - r_{A}}{L}x} = \frac{L \cdot dx}{(r_{B} - r_{A})x + r_{A}L};$$

$$R = \frac{R_{1}}{2} = \frac{1}{2} \int_{0}^{L} \frac{L \cdot dx}{(r_{B} - r_{A})x + r_{A}L} =$$

$$= \left(\frac{L \cdot \ln|(r_{B} - r_{A})x + r_{A}L|}{2(r_{B} - r_{A})}\right) \Big|_{0}^{L}.$$

$${

m R} = rac{L \cdot \ln^{r_B} \! / r_A}{2 (r_B - r_A)}$$

, где  $L = \sqrt{|A {

m B}|^2 - (r_B - r_A)^2};$   ${

m R} = rac{L (r_A + r_B)}{4}$ , при  $r_A pprox r_B.$

Последняя формула является предельной и разрешает неопределённость 0/0 при равных значениях  $r_A$  и  $r_B$ , а также при их близких значениях даёт более точные результаты вычисления на ЭВМ.

#### 2) Два треугольника

Два симметричных треугольника образуются, если ребро AB медиальной оси порождено двумя вогнутыми вершинами исходного многоугольника. Найдём сопротивление путём интегрирования вдоль оси x, проходящей через ребро, или вдоль полярного угла  $\alpha$  вокруг вогнутой вершины многоугольника (рис. 6). Перпендикуляр, опущенный из вогнутой вершины на ребро, задаёт начало отсчёта: x=0 ( $\alpha=0$ ).

Для начала выразим пределы интегрирования  $x_{A,B}$  ( $\alpha_{A,B}$ ) через известные значения радиус-функции  $r_{A,B}$  и длину ребра L = |AB|. Из теоремы Пифагора следует:

$$\begin{cases} r_A^2 = r_0^2 + x_A^2 \\ r_B^2 = r_0^2 + x_B^2 \end{cases} \Rightarrow r_B^2 - r_A^2 = x_B^2 - x_A^2.$$

Тогда с учётом  $L = x_B - x_A$ , можно вывести:

$$x_{A,B} = \frac{r_B^2 - r_A^2 \mp L^2}{2L}$$

;  $\sin \alpha_{A,B} = \frac{x_{A,B}}{r_{A,B}} = \frac{r_B^2 - r_A^2 \mp L^2}{2Lr_{A,B}}$ .

Учитывая, что  $r=r_0/\cos\alpha$  и  $x=r_0\tan\alpha$ , определим дифференциал сопротивления:

$$dR_1 = \frac{dx}{2r} = \frac{r_0 \cos \alpha \cdot d\alpha}{2r_0 \cos^2 \alpha} = \frac{d\alpha}{2 \cos \alpha}.$$

Следовательно,

$$R = R_1/2 = \frac{1}{2} \int_{\alpha_A}^{\alpha_B} \frac{d\alpha}{2\cos\alpha} = \left(\frac{1}{8} \ln \left| \frac{\sin\alpha + 1}{\sin\alpha - 1} \right| \right) \Big|_{\alpha_A}^{\alpha_B}.$$

$$R = \frac{1}{8} \ln \left| \frac{(r_B^2 - r_A^2 + L^2 + 2Lr_B)(r_B^2 - r_A^2 - L^2 - 2Lr_A)}{(r_B^2 - r_A^2 + L^2 - 2Lr_B)(r_B^2 - r_A^2 - L^2 + 2Lr_A)} \right|,$$

где  $L = |AB|.$

#### 3) «Трапеция» и «треугольник»

Конфигурация образуется, если параболическое ребро AB медиальной оси порождено стороной и вогнутой вершиной исходного многоугольника. Найдём сопротивление путём интегрирования вдоль оси x, проходящей через сторону многоугольника (рис. 7). Проекция вогнутой вершины (фокуса параболы) задаёт начало отсчёта x=0, проекции концов ребра — пределы интегрирования  $x_A$  и  $x_B$ , ось y направлена к вогнутой вершине. Заметим, что y=r. Имея координаты многоугольника, несложно вычислить расстояние D от вогнутой вершины до оси x (удвоенное фокусное расстояние параболы).

Из уравнения параболы следует, что радиус-функция изменяется вдоль ребра AB квадратично:

$$r = (x^2 + D^2)/2D$$

;  $dr = (x \cdot dx)/D$ .

Найдём сопротивление «трапеции»:

$$R_1 = \int_{x_A}^{x_B} \frac{dx}{r} = \int_{x_A}^{x_B} \frac{2D \cdot dx}{x^2 + D^2} = \left(2 \tan^{-1} \frac{x}{D}\right) \Big|_{x_A}^{x_B}.$$

Учитывая, что приращение длины параболы равняется  $\mathrm{d}t = \sqrt{(dx)^2 + (dr)^2} = \sqrt{x^2 + D^2}\,dx/D$ , оценим сопротивление «треугольника»:

$$R_2 = \int_{x_A}^{x_B} \frac{dt}{2r} = \int_{x_A}^{x_B} \frac{dx}{\sqrt{x^2 + D^2}} = \left(\sinh^{-1} \frac{x}{D}\right)\Big|_{x_A}^{x_B}.$$

Таким образом,

$$R = 2 \left[ \tan^{-1} \frac{x_B}{D} - \tan^{-1} \frac{x_A}{D} \right] \| \left[ \sinh^{-1} \frac{x_B}{D} - \sinh^{-1} \frac{x_A}{D} \right],$$

где  $D -$ удвоенное фокусное расстояние параболы.

#### IV. ИСПОЛЬЗОВАНИЕ ПОСТРОЕННЫХ СХЕМ ДЛЯ АНАЛИЗА ПАЛЕНИЙ НАПРЯЖЕНИЯ

Отметим следующие преимущества нашего метода экстракции для использования в программах раннего анализа сетей питания. Во-первых, полученные схемы достаточно компактны, поскольку для композиции проводника не использовались детализированные сетки. Это позволяет существенно ускорить численные решатели линейных систем и уменьшить потребление памяти. Во-вторых, наш метод сохраняет точное геометрическое соответствие экстрагированной резистивной схемы исходной топологии, что важно проектировщику для визуального анализа падений напряжения и локализации проблемных мест. Действительно, каждому экстрагированному резистору соответствует в точности один элементарный проводник декомпозиции.

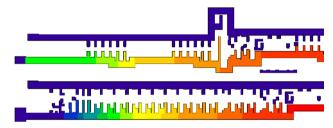

Рис. 8. Пример участка карты падений напряжений

IR-drop карта раскрашивается согласно значениям падений напряжения в нашей модели (рис. 8). Смежные границы элементарных многоугольников декомпозиции эквипотенциальны, их цвет определяется падением напряжения в узлах резистивной схемы. К раскраске внутренних областей элементарных многоугольников применяется градиент таким образом, чтобы изохроматические линии соединяли точки рёбер медиальной оси с ближайшими точками на контуре проводника. Вдоль ребра цвет определяется линейной интерполяцией падения напряжения между узлами. Для простоты вычислений параболические рёбра можно спрямить. Аналогичным образом раскрашивается карта эквивалентных сопротивлений от источников напряжения.

#### V. РЕЗУЛЬТАТЫ

Предложенный метод экстракции сопротивлений реализован в составе промышленного средства раннего анализа целостности питания Silvaco Invar ® Prime [12], применяемого при разработке аналоговых и смешанных цифро-аналоговых СБИС, сенсоров, микросхем высокой мощности и плоскопанельных дисплеев. Разработанная модель резистивной схемы опробована для анализа и визуализации падений напряжения, а также значений эквивалентных сопротивлений от источников напряжения.

Экспериментальные результаты доказали эффективность метода в сравнении с опробованным ранее эвристическим методом плиточного разбиения горизонтальными и вертикальными линиями [1], обобщённого на многоугольные проводники. Как видно из табл. 1, использование нашего метода позволило на порядок снизить число экстрагированных резисторов и время анализа тестовой схемы со сложной топологией, а также значительно уменьшить расход памяти.

Таблица 1 Сравнение эффективности методов экстракции на тестовой схеме со сложной топологией

|                       | Плиточная де-<br>композиция | Декомпозиция по медиальным осям |  |

|-----------------------|-----------------------------|---------------------------------|--|

| Узлов                 | 471 533                     | 110 149 (-77%)                  |  |

| Резисторов            | 880 323                     | 127 360 (-86%)                  |  |

| Время IR-drop анализа | 163 сек                     | 17 сек (-90%)                   |  |

| Расход памяти         | 1,27 GB                     | 0,6 GB (-40%)                   |  |

В настоящее время автор продолжает исследовать точность нового метода экстракции. Детальное сопоставление эквивалентных схем, полученных разными способами, затруднено, т.к. их структура может сильно различаться. Однако визуальное сравнение карт эквивалентных сопротивлений от источников напряжения на реальных схемах показало в целом неплохую корреляцию с результатами метода плиточной декомпозиции, также эвристического. Локально, однако, наблюдались расхождения до 5–15%. В дальнейшем планируется подробный анализ погрешности и уточнение формул элементарных сопротивлений на основе результатов численного моделирования уравнений электродинамики для типовых конфигураций. Также планируется улучшение моделей контактных площадок.

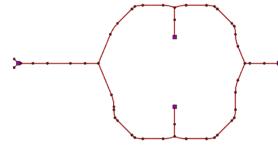

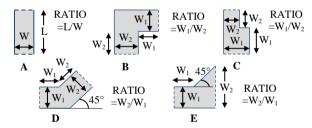

Рис. 9. Тестовые проводники [8]

На данном этапе метод протестирован на наборе проводников (рис. 9), точные сопротивления которых известны [8]. В результате погрешность составила менее 10% (табл. 2). Отметим, что при удлинении прямых участков изогнутых проводников В-Е, например в 10 раз, общая погрешность на порядок уменьшится.

#### VI. ЗАКЛЮЧЕНИЕ

Разработан оригинальный метод быстрой экстракции сопротивлений плоских проводников сложной формы, отличающийся компактностью полученных эквивалентных схем. Область его применения – системы анализа целостности питания аналоговых и смешанных СБИС, а также печатных плат и других электронных устройств с нерегулярной плоской топологией. Точность метода является достаточной для его использования на ранних этапах топологического проектирования, когда главным требованием выступает скорость анализа и возможность быстрой оценки качества множества вариантов топологии.

Таблица 2 Погрешность экстракиии на тестовых проводниках

| Тест | Ratio | R <sub>точн</sub> [8] | $\mathbf{R}_{\mathfrak{I}_{\kappa e \tau p}}$ | Ошибка |

|------|-------|-----------------------|-----------------------------------------------|--------|

| A    | 1     | 1                     | 1                                             | 0%     |

| A    | 5     | 5                     | 5                                             | 0%     |

| В    | 1     | 2.5                   | 2.53                                          | 1%     |

| В    | 1.5   | 2.55                  | 2.54                                          | 0%     |

| В    | 2     | 2.6                   | 2.56                                          | -2%    |

| В    | 3     | 2.75                  | 2.6                                           | -5%    |

| С    | 1.5   | 2.1                   | 1.96                                          | -7%    |

| C    | 2     | 2.25                  | 2.07                                          | -8%    |

| C    | 3     | 2.5                   | 2.27                                          | -9%    |

| C    | 4     | 2.65                  | 2.41                                          | -9%    |

| D    | 1     | 2.2                   | 2.26                                          | 3%     |

| D    | 1.5   | 2.3                   | 2.3                                           | 0%     |

| D    | 2     | 2.3                   | 2.42                                          | 5%     |

| D    | 3     | 2.6                   | 2.67                                          | 3%     |

| Е    | 1.5   | 1.45                  | 1.34                                          | -8%    |

| Е    | 2     | 1.8                   | 1.68                                          | -7%    |

| Е    | 3     | 2.3                   | 2.17                                          | -6%    |

| Е    | 4     | 2.65                  | 2.52                                          | -5%    |

#### Благодарности

Автор признателен разработчикам САПР компании Silvaco А.Ф. Самойлову, В.В. Давыдову и В.Н. Мартынчику за высказанные ценные замечания и практические рекомендации, а также А.М. Марченко (Mentor Graphics), ранее побудившему автора к изучению диаграмм Вороного и их использованию в САПР.

#### Литература

- Stark D. Analysis of Power Supply Networks in VLSI Circuits. Ph.D. Dissertation. Stanford University, Stanford, CA, USA, 1991.

- [2] Мороз Я.Н. Особенности методов проектирования систем питания высокопроизводительных микропроцессоров на этапе физического проектирования кристалла // МЭС-2012. Сб. трудов. М.: ИППМ РАН, 2012. С. 501–506.

- [3] Kahng A.B., Lienig J., Markov I.L., Hu J. VLSI Physical Design: From Graph Partitioning to Timing Closure. Springer, Dordrecht, 2011.

- [4] Безруков А.Е., Русаков А.С., Ткачев Д.Ф., Хапаев М.М. Методы экстракции паразитных элементов в интегральных схемах // МЭС-2005. Сб. трудов. М.: ИППМ РАН, 2005. С. 45-50.

- [5] Yu W., Wang X. Advanced Field-Solver Techniques for RC Extraction of Integrated Circuits (1st ed.). Tsinghua University Press, Beijing and Springer-Verlag Berlin Heidelberg, 2016.

- [6] Sheehan B.N. Realizable Reduction of RC Networks // IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2007. V. 26, No. 8. P. 1393–1407, Aug. 2007.

- [7] Hall P.M. Resistance Calculations for Thin Film Patterns // Thin Solid Films, 1967/68. V. 1, No. 5, P. 277-295.

- [8] Horowitz M., Dutton R.W. Resistance Extraction from Mask Layout Data // IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 1983. V. 2, No. 3. P. 145-150.

- [9] Spataro V. Counting Squares: A Method to Quickly Estimate PWB Trace Resistance. EDN Network, 2013. URL: https://www.edn.com (дата обращения: 01.02.2018).

- [10] Berg M., Cheong O., Kreveld M., Overmars M. Computational Geometry: Algorithms and Applications (3rd ed. ed.). TELOS, Santa Clara, CA, USA, 2008.

- [11] Lee D.T. Medial Axis Transformation of a Planar Shape // IEEE Transactions on Pattern Analysis and Machine Intelligence. 1982. Vol. PAMI-4, No. 4. P. 363-369.

- [12] InVar Power EM/IR Thermal. URL: https://www.silvaco.com/products/analog\_mixed\_signal/in Var/invar.html (дата обращения 01.02.2018).

### A Parasitic Resistance Extraction Method for Early Analysis of Complex Shaped Power Delivery Networks

#### K.K. Malinauskas

Silvaco Inc., kostas.malinauskas@silvaco.com

Abstract — With growing complexity and transistor density of modern electronic devices power integrity has become a key design factor [1]-[2]. Power supply constraints such as IR drop should be considered well before the signoff in physical design flow. In early design experiments essential is to use fast but reasonably accurate verification tools. Such requirements become tough for early IR-drop analysis when power delivery networks (PDN) with irregular topologies are considered. This is because traditional resistance extraction approaches apply either heavy field solvers on fine meshes or analytical heuristics with non-trivial and ambiguous polygon decomposition [5]-[9]. This work presents a novel method of parasitic resistances extraction from arbitrary shaped 2D interconnects. It includes a new approach to resistor network construction based on medial axis transform [11] and a simple set of analytical formulas for resistance values estimation. The extracted circuits are compact enough though are naturally mapped to the original complex layout. That is useful for early power delivery modeling with voltage drop or equivalent resistance maps visualization. The method is implemented within early design stage power integrity analysis system Silvaco Invar Prime [12]. It showed high efficiency in terms of runtime and memory consumption of the whole simulation flow while keeping sufficient accuracy. The extraction itself generates circuits of O(n) size in  $O(n \log n)$  time where n is the number of points describing the input geometry plus the number of interlayer contacts. We benchmarked our extractor against the tiling heuristics [1] adapted to complex polygons and observed the equivalent resistances correlation within 5-15%. At once the circuit sizes and IR-drop simulation runtimes reduced by an order of magnitude, the consumed memory – around 2x. The new approach can be applied to a variety of designs with complex PDN layout such as analog and mixed signal VLSI or printed circuit boards.

Keywords — resistance extraction, power integrity, voltage drop, Voronoi diagram, medial axis.

#### REFERENCES

Stark D.. Analysis of Power Supply Networks in VLSI Circuits. Ph.D. Dissertation. Stanford University, Stanford, CA, USA, 1991.

- [2] Moroz Ya.N. Osobennosti metodov proektirovaniya sistem pitaniya vysokoproizvoditel'nyh mikroprocessorov na etape fizicheskogo proektirovaniya kristalla (Peculiarities in methods of designing power supply systems in highperformance microprocessors at the stage of physical design of the crystal) // MES-2012. Sb. trudov. M.: IPPM RAN, 2012. S. 501–506.

- [3] Kahng A.B., Lienig J., Markov I.L., Hu J. VLSI Physical Design: From Graph Partitioning to Timing Closure. Springer, Dordrecht, 2011.

- [4] Bezrukov A.E., Rusakov A.S., Tkachev D.F., Hapaev M.M. Metody ekstrakcii parazitnyh elementov v integral'nyh shemah (IC parasitic elements extraction methods) // MES-2005. Sb. trudov. M.: IPPM RAN, 2005. S. 45-50.

- [5] Yu W., Wang X. Advanced Field-Solver Techniques for RC Extraction of Integrated Circuits (1st ed.). Tsinghua University Press, Beijing and Springer-Verlag Berlin Heidelberg, 2016.

- [6] Sheehan B.N. Realizable Reduction of RC Networks // IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2007. V. 26, No. 8. P. 1393–1407, Aug. 2007.

- [7] Hall P.M. Resistance Calculations for Thin Film Patterns // Thin Solid Films. 1967/68. V. 1, No. 5. P. 277-295.

- [8] Horowitz M. Dutton R.W. Resistance Extraction from Mask Layout Data // IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 1983. V. 2, No. 3. P. 145-150.

- [9] Spataro V. Counting Squares: A Method to Quickly Estimate PWB Trace Resistance. EDN Network, 2013. URL: https://www.edn.com (access date: 01.02.2018).

- [10] Berg M., Cheong O., Kreveld M., Overmars M. Computational Geometry: Algorithms and Applications (3rd ed. ed.). TELOS, Santa Clara, CA, USA, 2008.

- [11] Lee D.T. Medial Axis Transformation of a Planar Shape // IEEE Transactions on Pattern Analysis and Machine Intelligence. 1982. Vol. PAMI-4, No. 4. P. 363-369.

- [12] InVar Power EM/IR Thermal. URL: https://www.silvaco.com/products/analog\_mixed\_signal/in Var/invar.html (access date: 01.02.2018).