# Схемотехника устройств синхронизации в сетях высокоскоростной передачи данных

А.Л. Макаревич, С.М. Соковнич, М.С. Токарь

Приднестровский государственный университет им. Т.Г. Шевченко,

г. Тирасполь, Молдова, Приднестровье, mccar-bendery@mail.ru

Аннотация — Правильность передаваемой информации инфокоммуникационных систем и сетей в значительной степени определяется качеством работы системы схемотехнические синхронизации. Оптимальные решения при построении устройств синхронизации и всей системы поддержания синхронной работы в этом случае имеют принципиальное значение. В работе приводится анализ и результаты схемотехнического моделирования вариантов построения устройств синхронизации, реализуемых в рамках классической КМОП технологии и схемотехники. предлагаемых решений транзисторах с субмикронными проектными нормами потребовала лишь использования новых моделей транзисторов, параметры которых определяются совокупностью технологических операций процесса их изготовления конструктивно-технологическими ограничениями.

Ключевые слова — Фазовая автоподстройка частоты (ФАПЧ), компоненты ФАПЧ, фазовый детектор (компаратор), SPICE модели компонентов ФАПЧ, синхронизация.

## І. Введение

В работе исследуются схемотехнические решения созданию компонентов систем ФАПЧ обеспечивающих стабильность работы цифровых устройств в системах связи, реализуемых на основе классической КМОП технологии с проектными нормами в единицы и доли микрона. Обычно в инфокоммуникационных системах функцию поддержания синхронной работы всех устройств, передатчика, после выполняют установленных выделители тактовой частоты, извлекая ее принимаемого сигнала. Особую роль синхронизация цифровых системах радиосвязи радионавигации [2]. Варианты схем ФАПЧ различны, но решаемая с их помощью задача одна и та же - она заключается в правильной привязке синхросигнала к битовым интервалам принимаемых данных [3, 4].

В последние годы достаточно интенсивно проводятся исследования в области цифровых систем синхронизации (ЦСС), что обусловлено совершенствованием электронно-компонентной базы и существенным увеличением рабочих частот. Современные приемники в сетях мобильной связи

используются в достаточно сложной электромагнитной обстановке, обусловленной как ростом индустриальных помех, так и особенностями условий многопутевого распространения радиоволн в соответствующем диапазоне частот [2].

В работе рассмотрены ранее известные и некоторые усовершенствованные варианты реализации компонентов систем ФАПЧ (фазовых детекторов и формирователя сигналов), предназначенных использованию в узлах и блоках ЦСС. Приведенные результаты получены моделированием в пакете LTSpice с использованием характеристик КМОП устройств и блоков с микронными и субмикронными Параметры размерами элементов. моделей транзисторов изначально были настроены стандартный технологический процесс изготовления КМОП БИС с проектными нормами в единицы микрон. данные c параметрами субмикронных транзисторов (проектные нормы 90 и 45 нм) взяты на официальном сайте компании Microwind [5, 6]. Тип используемых моделей level = 3.

## II. Компоненты устройства ФАПЧ

Генератор с фазовой автоподстройкой частоты (устройство ФАПЧ) обычно содержит фазовый PD, (компаратор) инвертор инвертирующий усилитель, фильтр нижних частот и генератор, управляемый напряжением VCO. В данной работе были рассмотрены два схемотехнических варианта построения фазовых детекторов и одного формирователя сигналов UP и DOWN. Оценка их работоспособности проведена с использованием пакета LTSpice. На начальном этапе параметры моделей МОП транзисторов были настроены на технологический процесс изготовления КМОП БИС на БМК серии М (аналог БМК серии 1537), которые были получены по результатам выпуска специализированных КМОП БИС самого разного назначения в течение примерно 10 лет и учетом статистической обработки разброса технологических параметров условиях мелкосерийного производства. Было проведено схемотехническое моделирование для проверки правильности функционирования компонентов ФАПЧ и оптимизации соотношений длины и ширины каналов используемых транзисторов, на которых реализованы базовые библиотечные элементы

Полученные нами схемотехнические модели были необходимы для исследований работоспособности элементов в широком диапазоне напряжений питания, которые, если совпадают с реальными, являются дополнительным подтверждением правильности настройки используемых моделей. Так, если рабочее напряжение питание устройств на КМОП транзисторах с проектными нормами в единицы мкм обычно равнялось 5 В, а диапазон рабочих напряжений составлял 3 – 7,5 В, то устройства, работающие на транзисторах с субмикронными проектными нормами, вынуждены работать при пониженных напряжениях питания начиная с величин порядка 1 В.

были Схемные решения реализованы транзисторах с проектными нормами 90 и 45 нм, параметры моделей для которых, были заимствованы нами в работе [5] и на сайте [6]. Эти модели показали возможность функционирования исследуемых компонентов ФАПЧ на частотах 4 и 2 ГГи, но наш анализ их работоспособности в широком диапазоне напряжений питания показал, что эти компоненты работают при напряжениях 0,3 В и менее, что физически, т.к. сумма пороговых напряжений п- и р- канальных транзисторов, приведенных в моделях, составила 0,3 В. Поэтому нами были усовершенствованы модели МОП транзисторов, изготовляемых с проектными нормами 90 и 45 нм. Это позволило получить результаты, подтвердившие работоспособность компонентов ФАПЧ в диапазоне напряжений питания от 0,5 до 3,5 В и оценить величину времён переключения и задержек при работе на емкостную нагрузку. В качестве результатов исследований приводятся осциллограммы входных, внутренних и выходных сигналов, отражающих работу устройств на тактовой частоте 4 ГГц (первый вариант компаратора) и 2 ГГц (формирователь сигналов UP и DOWN и второй вариант компаратора).

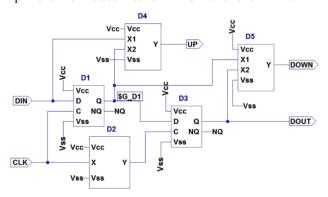

На рис. 1 изображен первый вариант схемы фазового детектора, которая построена на двух D триггерах M-S типа (D1 и D3), инверторе D2 и двух элементах «исключающее ИЛИ» (D4 и D5). Все перечисленные логические элементы выполнены на двунаправленных ключах и инверторах, т.е. с применением классической КМОП схемотехники.

Рис. 1. Схема фазового компаратора (1 вариант)

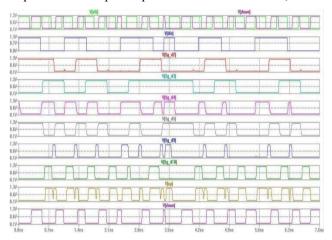

Частота тактового сигнала при проверке работоспособности данного компонента ФАПЧ, спроектированного по проектным нормам 90 и 45 нм, составляла 4 ГГи. Для того, чтобы оценить правильность выработки сигналов UP и DOWN, свидетельствующих о рассогласовании входной частоты и частоты внутреннего генератора устройства ФАПЧ, входным информационным сигналом была задана кусочно-линейная функция PWL.

Сигнал DIN в коде NRZ поступает из линии на вход фазового компаратора. Этот сигнал не должен оставаться в неизменном состоянии 0 или 1 на протяжении длительного времени. Например, в системах передачи данных заранее полагают, что максимальная длительность неизменного состояния информационного сигнала не должна превышать двадцати битовых интервалов [1].

Фазовый компаратор сопоставляет сигнал DIN с синхросигналом CLK от генератора VCO. При правильном фазовом соотношении этих сигналов на выходе фазового компаратора формируется сигнал DOUT, соответствующий данным в линии, при этом битовых интервалов границы его задаются отрицательными фронтами сигнала CLK. Чтобы достичь, а затем и поддерживать правильное фазовое соотношение между сигналами DIN и CLK, фазовый компаратор непрерывно отслеживает ошибку взаимного расположения фронтов этих сигналов и формирует управляющие сигналы ускорения UP или замедления DOWN темпа работы генератора VCO [1].

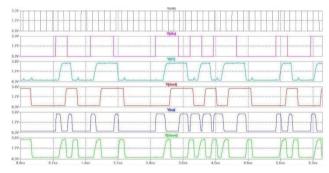

На следующем рисунке приведены результаты моделирования работы первого варианта фазового детектора на тактовой частоте 4  $\Gamma T u$ . Проектная норма 90  $\mu$ , напряжение питания 3,3 В при работе на нагрузку 0,02  $\mu$  на каждый выход, что на порядок выше реальной нагрузки. Все сигналы фазовый детектор отрабатывает, заметны искажения фронтов импульсов, обусловленные большой емкостью нагрузки. Уменьшение емкости нагрузки на порядок, т.е. до 0,002  $\mu$ , убирает эти искажения сигналов и уменьшает время задержки с 52 до 34  $\mu$ .

Рис. 2. Временные диаграммы входных и выходных сигналов

Подробные исследования работоспособности всех трех компонентов системы ФАПЧ, построенных на транзисторах с проектной нормой 90 и 45 *нм*, при напряжениях питания менее 1 В показали отсутствие

искажений выходных сигналов и практически отсутствие возрастания времени задержки распространения сигналов. Это указало на несовершенство моделей транзисторов, предлагаемых в [5, 6].

Известно, что каждая модель МОП транзистора окончательно может быть «настроена» только фирмой изготовителем или, в современной терминологии фабрикой. Но по опыту реального производства микросхем на КМОП транзисторах каждая «фабрика», владевшая КМОП технологией, выпускала микросхемы отличающимися статическими и динамическими параметрами, которые были обусловлены различием в используемом оборудовании И особенностями реализации технологических процессов. Конечно, технологический процесс изготовления КМОП БИС с помощью 12 фотолитографий при проведении порядка 200 операций не может быть сопоставим с технологией микросхем производства C субмикронными проектными нормами, требующих ло фотолитографий и проведения порядка 2 - 3 тысяч технологических операций. Однако физические принципы работы МОП транзисторов, как с микронными, так и субмикронными проектными нормами сохранились [8]. В предлагаемых моделях [5, 6] отсутствуют такие важные параметры, сопротивления стока и истока транзисторов, а также емкости переходов подложка-сток и подложка-исток. При этом, по умолчанию, классический SPICE, к которому и относится используемый нами пакет LTSpice, приравнивает их к 0. Дополнительным аргументом в пользу продолжения использования параметров моделей транзисторов с микронными и субмикронными проектными нормами, т.е. моделей, использующих 42 параметра (level = 1, 2, 3 и 4), являются модели, рекомендуемые к применению в [6, 7]. При этом предлагаемая в [7] модель level = 54 оперирует примерно 400-500 параметрами и требует использования лицензируемых версий совместимых программ, таких как HSPICE или Spectre-RF и др.

Производство использованием c микронными проектными нормами еще сохраняется. Главное, в чем мы видим смысл нашей работы, заключается в возможности проектирования микросхем на КМОП транзисторах, как с субмикронными, так и микронными проектными нормами при реализации их виде специализированных БИС (ASIC), разрабатываемых для конкретных устройств аппаратуры самого различного назначения. А переход к моделям «фабрики» при этом никто не отменяет, но уже на следующем этапе, когда компоненты системы, или вся ЦСС схемотехнически проработаны.

Поэтому, отталкиваясь от многократно проверенных данных по транзисторам с проектными нормами в единицы микрон нами были скорректированы указанные недостатки моделей из [5, 6] с учетом реальных геометрических размеров элементов, что позволило получить результаты более близкие к реальным. В итоге, нами предлагаются

усовершенствованные модели транзисторов с проектными нормами 90 и 45 *нм*, дополненные рядом параметров:

- \* Mos models in 45nm

- \* n-MOS Model 3:

- .MODEL MN45N NMOS LEVEL=3 VTO=0.18 UO=160.000

- + TOX= 3.5E-9 LD =0.005U THETA=0.300 GAMMA=0.400

- +RD=93 RS=143 PHI=0.150 KAPPA=0.350 VMAX=180.00K +CGSO=100.0p CGDO=100.0p L=45n W=450n

- +CGBO= 60.0p CJSW=240.0p CBD=.61F CBS=.61F

- \* p-MOS Model 3:

- .MODEL MP45N PMOS LEVEL=3 VTO=-0.15 UO=120.000

- +TOX= 3.5E-9 LD =0.005U THETA=0.300 GAMMA=0.400 +RD=155 RS=155 PHI=0.150 KAPPA=0.350 VMAX=180.00K

- +CGSO=100.0p CGDO=100.0p L=45n W=900n

- +CGBO= 60.0p CJSW=240.0p CBD=.96F CBS=.96F

# III. РЕЗУЛЬТАТЫ ИССЛЕДОВАНИЙ РАБОТОСПОСОБНОСТИ КОМПОНЕНТОВ ФАПЧ

В результате моделирования с использованием предлагаемых моделей транзисторов были получены временные диаграммы входных, внутреннего и выходных сигналов первого варианта схемы фазового детектора, построенного на транзисторах с проектными нормами 45 *нм* при напряжении питания Ucc=1,2 B (рис. 3).

Рис. 3. Осциллограммы входных, внутреннего от триггера D1 и выходных сигналов

Время задержки выходного сигнала, измеренное в том же самом месте, составило 69 nc. Далее была исследована работоспособность формирователя сигналов UP и DOWN (рис. 4), который совместим с аналогичными компонентами устройства ФАПЧ, но способен работать на более низкой тактовой частоте 2  $\Gamma \Gamma \mu$ .

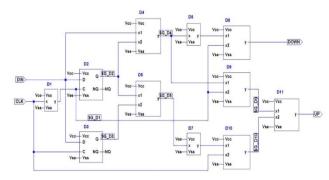

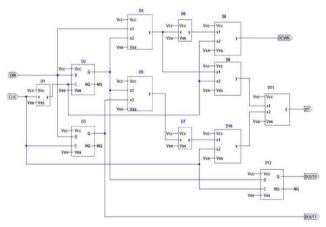

Рис. 4. Схема формирователя сигналов

Здесь потребовалось увеличение нагрузочной способности выходных каскадов D триггеров M-S типа для того, чтобы обеспечить достаточную мощность

выходных сигналов. Кроме этого, в схему добавлены два инвертора D6 и D7, три элемента 2И (D8, D9 и D10) и элемент 2 ИЛИ (D11). Элементы D6 – D11 формируют сигналы UP и DOWN на основе сигналов с выходов элементов D4 и D5, а также прямого и инверсного сигналов CLK.

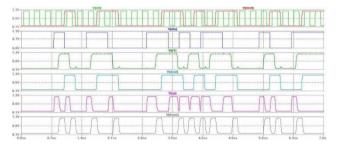

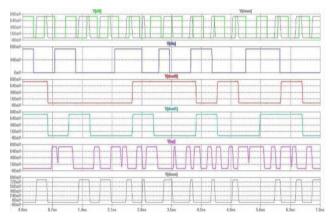

На рис. 5 приведены осциллограммы входных, внутренних и выходных сигналов формирователя, построенного на КМОП транзисторах с проектными нормами 45 *нм* при напряжении питания Vcc = 1,2 B.

Рис. 5. Входные, внутренние и выходные сигналы формирователя

Время задержки распространения сигнала DOWN, полученное в результате моделирования работы формирователя, составило 49 *пс*. Данный формирователь был использован для построения схемотехнической модели второго варианта фазового детектора. Схема этого детектора приведена на рис. 6.

Рис. 6. Схема фазового детектора (второй вариант)

В данной схеме к формирователю добавлен еще один триггер D12. Главное преимущество этой схемы в том, что при той же скорости поступления данных она способна работать с синхросигналом, частота которого уменьшена в два раза. Кроме того, биты данных, поступающие по линии DIN, удается разделить на 2 потока DOUT1 и DOUT0. А это позволит в дальнейшем

обрабатывать данные параллельно, но вдвое медленнее, чем при одноканальной обработке [2].

Схема проверки работоспособности фазового детектора, реализованного по второму варианту, приведена на рис. 7.

Рис. 7. Схема исследований работоспособности фазового детектора

Результаты исследований приведены на рис. 8. Время задержки сигнала DOWN при напряжении питания Ucc = 1.2 В составило 54 nc.

Рис. 8. Осциллограммы входных и выходных сигналов второго варианта фазового детектора

Полученные нами результаты исследований работоспособности компонентов ФАПЧ в широком диапазоне изменения напряжения питания показали, что правильное функционирование всех элементов имеет место в диапазоне Ucc от 0,8 до 1,2 B, что соответствует данным, имеющимся в литературе [6, 8]. Время задержки распространения сигналов при минимальном значении напряжения увеличилось до 80-90 пс. Приведенные выше времена задержек были получены при напряжении питания 1,2 В. Дальнейшее повышение значений напряжения питания приведет к улучшению динамических параметров, т.е. к снижению задержек, однако это повышение нежелательно, т.к. в случае большого числа транзисторов на кристалле микросхемы возможен перегрев из-за утечек тока в транзисторах длиной канала менее 100 нм.

# IV. ЗАКЛЮЧЕНИЕ

Полученные результаты позволят в дальнейшем создавать модели различных вариантов

схемотехнического решения устройств ФАПЧ и определять их основные параметры, такие как: полоса удержания, полоса захвата, время вхождения в синхронизм и скорость настройки. А это, в свою очередь, позволит оценить возможность применения данных устройств в системах различного назначения. Определяющую роль в современных ЦСС играют выделители тактовой частоты, реализация которых также требует применения КМОП транзисторов с субмикронными проектными нормами и способных работать на предельных частотах.

Время, затрачиваемое на моделирование исследованных компонентов ФАПЧ, при использовании пакета LTSpice не превышало десятков секунд.

### Литература

[1] Сухман С.М., Берман А.В., Шевкопляс Б.В. Синхронизация в телекоммуникационных системах.

- Анализ инженерных решений. М.: Эко-Трендз, 2003. 272с.

- [2] Шахтарин Б.И., Сизых В.В., Сидоркина Ю.А., Андрианов И.М., Калашников К.С. Синхронизация в радиосвязи и радионавигации: Учебн. пособие / М.: Горячая линия-Телеком, 2011. 278с.

- [3] Шевкопляс Б.В. Синхронизация в телекоммуникационных системах. Сборник задач. Учеб. пособие. М.: Радиософт, 2012. 368с.

- [4] Шевкопляс Б.В. Элементы схемотехники оптоволоконных систем. Инженерные решения, М.: Радиософт, 2012. 760с.

- [5] Коноплев Б.Г., Рындин Е.А., Приступчик Н.К., Денисенко М.А. Проектирование интегральных схем. – Таганрог: Изд-во ТТИ ЮФУ, 2010. – 76 с.

- [6] http://microwind.net, 28.03.2018

- [7] http://cmosedu.com, 12.05.2018

- [8] Зебрев Г.И. Физические основы кремниевой наноэлектроники: Учебник. – М.: МИФИ, 2008. 280с.

# Circuit Design of Synchronizing Devices Within High-speed Data Services

A.L. Makarevich, S.M. Sokovnich, M.S. Tokar

Pridnestrovian State University of Taras Shevchenko, Tiraspol, Moldova, Pridnestrovye

mccar-bendery@mail.ru

Abstract — The correctness of the information transmitted by information and communications systems and networks is largely determined by the quality of the synchronization system. The optimal circuit design for the construction of synchronizing devices and the entire system for maintaining synchronous operation, in this case, is of a crucial significance. In the research, we analyze and summarize the results of circuit simulation for several variants of the construction of synchronizing devices components, implemented within the framework of classical CMOS technology and circuit technology. The implementation of the proposed solutions on CMOS transistors with submicron design rules will require only the usage of new transistor models, which parameters are determined by a group of technological operations of their manufacturing process and inherent structural technological limitations. This article describes methods of designing PLL components using SPICE models for CMOS transistors with design standards  $1 - 2 \mu m$  (the model proposed by us) and 90 - 45 nm from Microwind. We propose classic circuit solutions to implement PLL components on bidirectional switches and inverters.

**Keywords** — phase-lock-loop frequency control (PLL), PLL components, phase-lock detector (comparer), SPICE models of PLL components, synchronization.

#### REFERENCES

[1] S.M. Sukhman, A.V. Berman, B.V. Shevkoplyas Sinkhronizatsiya v telekommunikatsionnykh sistemakh.

- Analiz inzhenernykh resheniy (Synchronization in telecommunication systems. Analysis of engineering solutions). M .: Eko-Trendz, 2003. 272s.

- [2] Shakhtarin B.I., Sizykh V.V., Sidorkina YU.A., Andrianov I.M., Kalashnikov K.S. Sinkhronizatsiya v radiosvyazi i radionavigatsii (Synchronization in radio communication and radio navigation): Uchebn. posobiye / M.: Goryachaya liniya-Telekom, 2011. 278s.

- [3] Shekoplyas B.V. Sinkhronizatsiya v telekommunikatsionnykh sistemakh (Synchronization in telecommunication systems). Sbornik zadach. Ucheb. posobiye. M.: Radiosoft, 2012. 368s.

- [4] Shekoplyas B.V. Elementy skhemotekhniki optovolokonnykh system Inzhenernyye resheniya (Elements of circuitry of fiber-optic systems. Engineering Solutions). M.: Radiosoft, 2012. 760s.

- [5] Konoplev B.G., Ryndin Ye.A., Pristupchik N.K., Denisenko M.A. Proyektirovaniye integral'nykh skhem (Design of integrated circuits). - Taganrog: Izd-vo TTI YUFU, 2010. - 76s.

- [6] microwind.net

- [7] cmosedu.com

- [8] Zebrev G.I. Phiziceskie osnovi kremnievoy nanoelectroniki (Physical basics of silicon nanoelectronics) – M.: MEPI, 2008. 280p.