# Метод дублирования триггеров в средствах тестирования с компрессией

М.С. Ладнушкин

НИИ системных исследований РАН, Mockвa, maximsl@gmail.com

Аннотация — Предложен метод сокращения времени тестирования неисправностей цифровой СБИС за счёт дублирования отдельных функциональных триггеров. обусловлено Сокращение времени тестирования тестируемости сигналов, а также **у**величением снижением взаимных конфликтов неисправностей в логических путях СБИС. Предложен алгоритм отбора триггеров для дублирования на основе поиска логических путей с наибольшим числом источников сигналов, который был использован проектировании встроенных средств тестирования ряда заказных блоков и систем-на-кристалле. Результаты показали снижение времени тестирования в среднем на 14,4% при аппаратурных затратах, не превышающих 1,2% общей площади СБИС.

Ключевые слова — тестирование, отбраковка микросхем, дублирование триггеров, компрессия тестовых сигналов, моделирование.

#### І. Введение

Внедрение дополнительных тестовых структур контроля и наблюдения внутренних узлов в СБИС позволяет увеличить тестовое покрытие и сократить время тестирования. Создание тестового режима работы, в котором тригтерная подсистема СБИС используется в качестве сдвигового регистра (скансхемы) [1], позволяет полностью контролировать и наблюдать состояние всех триггеров СБИС и использовать их для тестирования комбинационной части СБИС.

Объемы тестовых данных, необходимых для тестирования микросхем, растут, и встраиваемые средства сжатия [2], [3] не всегда позволяют сократить время тестирования до приемлемых величин ввиду многих причин, включая рост длин логических путей, увеличение количества взаимных конфликтов неисправностей, а также необходимость снижения абстракции при создании тестовых последовательностей для СБИС с уровня логических элементов до уровня транзисторов [4], [5].

С ростом длин логических комбинационных путей и ростом количества сходящихся разветвлений снижается наблюдаемость и контролируемость узлов этих путей в режиме тестирования [6], [7], [8]. Для решения данной проблемы в определённые узлы СБИС встраиваются дополнительные тестовые схемы тестовые точки контроля и обзора — дополнительные

триггеры с управляющей логикой, позволяющие увеличить наблюдаемость и контролируемость отдельных узлов комбинационной подсистемы СБИС [9].

Установка тестовых точек приводит к сокращению времени тестирования до 35% [10], [11]. Современный метод установки тестовых точек, снижающий количество взаимных конфликтов неисправностей «залипание», позволяет сократить тестирования в среднем в 2,2 раза для скан-схем с компрессией за счёт увеличения количества неисправностей, тестируемых каждым тестовым вектором [12]. Однако установка тестовых точек уменьшает ресурс трассировки, увеличивает задержки распространения сигналов и увеличивает площадь тестовой логики, которая используется только в режиме тестирования и в рабочем режиме не функционирует. Современные методы создания тестовых используют существующие функциональные триггеры СБИС вместо дополнительных, что позволяет сократить аппаратурные затраты на тестовую логику, однако увеличения задержек критических путей после установки тестовых точек избежать не удается [13], [14]. Увеличение контролируемости и наблюдаемости критических с точки зрения быстродействия путей представляет серьёзную проблему при проектировании средств тестирования.

Метод создания копий отдельных элементов (дублирования) известен как способ сокращения длин проводников при проектировании топологии СБИС, что позволяет сократить задержки распространения сигналов [15]. Триггер и его копия в функциональном режиме находятся в одинаковом логическом состоянии в любой момент времени. Считается, что и в режиме скан-тестирования должно сохраняться равенство состояний этих триггеров, так как загрузка различных значений в дублированные скан-триггеры может привести к выходу микросхемы из строя в случае, если присутствуют логические допускающие сквозные токи [16]. Однако, если таких элементов на кристалле немного или нет вовсе, то использование копий триггеров как независимых переменных при генерации тестовых последовательностей может увеличить тестируемость узлов комбинационной части СБИС.

## II. УВЕЛИЧЕНИЕ ТЕСТИРУЕМОСТИ УЗЛОВ КОМБИНАЦИОННОЙ СХЕМЫ

В режиме скан-тестирования тестируемость логического узла (или вероятность обнаружения неисправности) комбинационной схемы может быть рассчитана как минимальное количество тестовых последовательностей, необходимых для обнаружения неисправности, делённое на максимальное количество уникальных входных воздействий [6]. Рассмотрим комбинационную схему с п входами  $\vec{x} = (x_1, x_2, ..., x_n)$

и m выходами  $\vec{F} = (F_1, F_2, ..., F_m)$ . Пусть  $g(\vec{x})$  – внутренний сигнал схемы, тогда тестируемость неисправностей типа «залипание-в-0» и «залипание-в-1» в сигнале g могут быть соответственно выражены [6],[17]

$$t(g/0) = S\left(g(\vec{x})\sum_{j=1}^{m} \frac{\partial F_{j}}{\partial g}\right), \tag{1}$$

$$t(g/1) = S\left(\overrightarrow{g}(\overrightarrow{x})\sum_{j=1}^{m} \frac{\partial F_{j}}{\partial g}\right), \tag{2}$$

где t(g/0) — тестируемость неисправности типа «залипание-в-0», а t(g/1) - типа «залипание-в-1». S(F) — синдром функции F:

$$S(F) = \frac{K}{2^n} \tag{2}$$

где K — количество минтермов функции F, а n — количество её входов. Произведение функций в скобках — это пересечение множеств входных воздействий, которые задают необходимое значение в сигнале  $g(\vec{x})$  и обеспечивают наблюдение этого значения на выходах  $\vec{F}$ . Если схема содержит сходящиеся разветвления, то это пересечение множеств может оказаться довольно небольшим, что в результате приводит к снижению величин  $t(g/i), i \in \{0;1\}$ .

Входные сигналы, имеющие разветвление на входах, могут быть разделены на отдельные независимые сигналы путём дублирования триггеровисточников, что позволяет сократить число сходящихся разветвлений в схеме, а значит и увеличить тестируемость этой схемы.

Рассмотрим изменение тестируемости узлов комбинационной схемы при дублировании тригтеров в сравнении с использованием стандартных тестовых точек контроля и обзора.

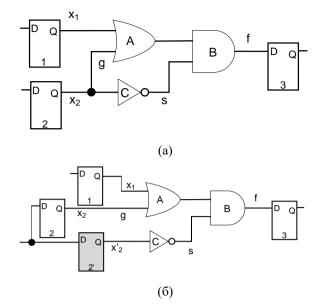

На рис. 1а изображен пример фрагмента скан-цепи (триггеры 1-2) и связанная с ней комбинационная схема. Комбинационная схема имеет два независимых входа, которые обозначены переменными  $x_1$  и  $x_2$ , и один выход — f. Данная комбинационная схема содержит сходящееся разветвление через узел  $x_2$ . Представим, что в сигнале g есть константная неисправность типа «залипание-в-0» (g/0).

Тестируемость сигнала  $\underline{g=x_2}$  согласно формуле (1) будет равна  $t(g/0) = S(x, x_1, x_2) = 0$ .

Рис. 1. Пример увеличения тестируемости в комбинационной схеме: а) исходная схема; б) модифицированная схема с дублированием триггера

Тестируемость неисправности g/0 равна 0, и это значит, что неисправность «залипание-в-0» в данном узле средствами тестирования установить невозможно. Для увеличения тестируемости t(g/0) этого узла необходимо внести аппаратные изменения в данную схему.

Рассмотрим модифицированную схему с дублированием триггера 2 (см. рис. 16). В данной схеме разветвление на выходе триггера 2 было разбито на два независимых логических сигнала, управляемых независимо триггерами 2 и 2. Независимость управления достигается за счёт загрузки различных значений в дублированные триггеры в процессе тестирования. Чтобы комбинационная схема была функционально эквивалентна исходной, входы D триггеров 2 и 2 объединяются. Оценка тестируемости неисправности g/0 для модифицированной схемы с дублированием триггера показала увеличение значения t(g/0), которое составила

$$t(g/0) = S(x_2 \overline{x_1} \overline{x_2}') = 1/8.$$

# III. Сокращение взаимных конфликтов неисправностей

Рассмотрим теперь дублирование триггеров как средство сокращения конфликтов неисправностей. Чтобы сократить количество тестовых векторов, необходимое для тестирования неисправностей СБИС, каждый тестовый вектор должен иметь возможность обнаруживать как можно большее число дефектов, чему препятствуют взаимные конфликты неисправностей. Пусть  $s_0$  — источник разветвления сигналов с ветвями  $s_1, \ldots, s_n$ , тогда величины

конфликтов выставления 0 и 1 в любой ветви  $s_k$ ,  $k \in [1;n]$  могут быть рассчитаны следующим образом [18]:

$$c_{s_h} = \min\{b_{s_h}; F_{s_h}\},$$

(4)

$$C_{s_{k}} = \min\{B_{s_{k}}; f_{s_{k}}\},$$

(5)

где:

- $c_{s_k}$  и  $C_{s_k}$  количество конфликтов выставления логического «0» и «1» в узле  $s_k$ , соответственно,

- $b_{s_k}$  и  $B_{s_k}$  необходимое количество логических состояний ветви  $s_k$  в «0» и «1», соответственно, для обеспечения наблюдаемости неисправностей на всех остальных ветвях разветвления с источником  $s_0$ ,

- $f_{s_k}$  и  $F_{s_k}$  количество логических состояний ветви  $s_k$  в «0» и «1», соответственно, необходимое для наблюдения всех неисправностей, являющихся источником для сигнала  $s_0$ , причем

$$F_{s_{t}} = F_{s_{0}} + \sum_{i=1}^{n} B_{s_{i}}, i \neq k, \tag{6}$$

$$f_{s_k} = f_{s_0} + \sum_{i=1}^n b_{s_i}, i \neq k, \tag{7}$$

Для разветвления сигнала s на выходе триггера значение  $F_{s_0}=f_{s_0}=0$  , то есть  $F_{s_k}=\sum_{i=1}^n B_{s_i}, i\neq k$ , ,  $f_{s_k}=\sum_{i=1}^n b_{s_i}, i\neq k$ , . Тогда, если число ветвей разветвления сократить до n = 1, то  $F_{s_k}=f_{s_k}=0$  . Отсюда  $C_{s_k}=c_{s_k}=0$  в данном разветвлении, то есть конфликтов неисправностей в нём не будет. Более того, для любого сигнала x в путях от  $s_0$  до конечных приёмников сигнала (тригтеров или портов вывода), значения  $f_x$  и  $F_x$  всех разветвлений будут сокращены на  $\sum_{i=1}^n b_{s_i}$  и  $\sum_{i=1}^n B_{s_i}$  , соответственно. Отсюда по формулам (4) и (5) получаем, что количество конфликтов  $c_x$  и  $C_x$  любого сигнала x может быть сокращено на  $\sum_{i=1}^n B_{s_i}$  и  $\sum_{i=1}^n b_{s_i}$  , соответственно.

Дублирование триггера-источника разветвления позволяет сократить число ветвей разветвления до 1, что приведет к снижению числа взаимных конфликтов во всех логически путях от этих триггеров.

На рис. 2а показан пример комбинационной схемы с взаимным конфликтом неисправностей в сигнале s. Отдельные части комбинационной схемы отмечены треугольниками, в которых количество неисправностей составляет  $M_i$ . По формулам (4)-(7) рассчитаем величины конфликтов в узлах  $s_1$  и  $s_2$ , получим:

$$\begin{split} c_{s_1} &= \min\{b_{s_1}; F_{s_1}\} = \min\{0; \min\{M_2; M_1\}\} = 0, \\ C_{s_1} &= \min\{B_{s_1}; f_{s_1}\} = \min\{M_3; M_4\}, \end{split}$$

$C_{s_{2}} = \min\{b_{s_{2}}; F_{s_{2}}\} = \min\{M_{4}; \min\{M_{1}; M_{2}\} + M_{3}\},$   $C_{s_{2}} = \min\{B_{s_{2}}; f_{s_{2}}\} = \min\{0; 0\} = 0.$   $M_{1} \longrightarrow G_{1} \longrightarrow G_{2} \longrightarrow G_{3} \longrightarrow G_{4} \longrightarrow G_{5} \longrightarrow G_{5$

Рис. 2. Пример сокращения конфликтов неисправностей в комбинационной схеме: а) исходная схема; б) модифицированная схема с дублированием триггеров

**(б)**

Согласно оценке возникает конфликт выставления «0» в узле  $\mathbf{s}_2$  и конфликт выставления «1» в узле  $\mathbf{s}_1$ . Для разрешения данного конфликта авторами [18] предлагается установить тестовую точку контроля ИЛИ-типа на сигнал  $\mathbf{s}_2$ , что приводит к снижению до 0 в данной схеме величин  $c_{s_1}$  и  $C_{s_1}$ .

Рассмотрим эквивалентную модифицированную схему с дублированием триггеров 1 и 2 (см. рис. 2б). Получается следующий набор выражений, характеризующий сигналы  $s_1$  и  $s_2$  в схеме:

$$c_{s_1} = \min\{0;0\} = 0,$$

$$C_{s_1} = \min\{M_3; M_4\},$$

$$c_{s_2} = \min\{M_4; M_3\},$$

$$C_{s_2} = \min\{0;0\} = 0.$$

Сравнивая результаты оценок конфликтов неисправностей модифицированной и исходной схемы можно заключить, что величина конфликта

выставления «0» в узле  $s_2$  теперь не зависит от переменных  $M_1$  и  $M_2$ , что приводит к снижению  $c_{s_2}$  на величину до  $\min\{M_2;M_1\}$ .

Так как предложенный метод дублирования триггера оказывает влияние на любой логический путь от этого триггера до конечных приёмников сигналов за счёт снижения величин взаимных конфликтов разветвления в на выходе этого триггера, то можно сделать вывод, что наибольший эффект от данного метода будет достигнут при дублировании триггеров с наибольшим количеством комбинационных элементов в выходных путях этого триггера.

# IV. АЛГОРИТМ ПОИСКА ТРИГГЕРОВ-ИСТОЧНИКОВ ДЛЯ ДУБЛИРОВАНИЯ

Известны методы поиска всех сходящихся разветвлений по логическому описанию схемы [7], [8]. Вариант дублирования всех тригтеров, имеющих на выходе разветвление, приводит к чрезмерному росту площади. Таким образом целесообразно выделить для дублирования только те тригтеры, которые дают максимальный эффект увеличения тестируемости и сокращения количества конфликтов неисправностей. В данной работе анализируется алгоритм, который основан на поиске логических деревьев с наибольшим числом источников.

Таблица 1 Параметры исследуемых СБИС

| Характеристика                              | BM8    | СМПО           | Обработка-<br>2 | Схема-6 |  |

|---------------------------------------------|--------|----------------|-----------------|---------|--|

| Технология                                  |        | ая 65 нм<br>ЮП | 250 нм КНИ      |         |  |

| Количество<br>триггеров,<br>тысячи          | 513,8  | 344,8          | 103,0           | 76,1    |  |

| Количество комбинационных элементов, тысячи | 2084,7 | 878,0          | 528,3           | 191,2   |  |

| Количество портов ввода/вывода              | 639    | 311            | 353             | 140     |  |

| Количество ОЗУ и заказных блоков            | 1055   | 371            | 110             | 24      |  |

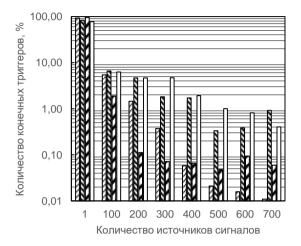

Длинные сходящиеся пути являются, как правило, логическими функциями большого числа переменных. Проведён анализ логических путей ряда СБИС с проектными нормами от 65 до 250 нм путём подсчёта количества конечных источников сигнала для каждого тригтера схемы (см. табл. 1). Анализ показал, что значительная часть (более 70%) триггеров имеет один конечный источник сигнала. Распределение триггеров

по количеству источников сигналов с шагом в 100 единиц дано на рис. 3. В СБИС ВМ8 встречались единицы триггеров с количеством различных источников сигналов вплоть до 7400. Логические функции с таким количеством источников представляют сложность при тестировании, поэтому их дублировать имеет смысл в первую очередь.

Рис. 3. Распределение триггеров по количеству источников сигналов

Алгоритм поиска триггеров-источников критических путей с порогом dmax по количеству элементов содержит следующую последовательность шагов:

- 1) задание количества тригтеров для дублирования  $d_{\text{max}};$

- 2) анализ схемы и получение множества сигналов L с низкой тестируемостью;

- 3) получение множества конечных источников  $S_i$  для каждого сигнала  $L_i$ ;

- 4) исключение из каждого множества  $S_i$  портов ввода-вывода и триггеров без разветвления на выходе;

- 5) сортировка множеств  $S_i$  по убыванию количества элементов;

- 6) последовательное добавление элементов из каждого множества  $S_i$  в множество D до тех пор, пока их количество не превысит  $d_{\text{max}}$ .

Результатом алгоритма является множество триггеров D, которые подлежат дублированию.

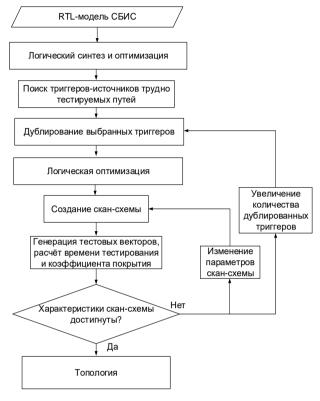

## V. МАРШРУТ ПРОЕКТИРОВАНИЯ СБИС С ДУБЛИРОВАНИЕМ ТРИГГЕРОВ

Дублирование триггеров осуществляется после того, как получена модель СБИС на уровне логических элементов (нетлист). Сначала осуществляется поиск триггеров-источников критических путей с порогом  $d_{max}$ . Триггер, который имеет в выходном логическом

пути элемент. допускающий сквозные исключается из списка. Полученный список триггеров D дублируется, после чего осуществляется логическая оптимизация схемы поскольку дублирование триггеров может привести к изменению задержек распространения сигналов. Ha основе оптимизированной схемы создаётся скан-схема с компрессией.

Рис. 4. Маршрут проектирования

Генерация и моделирование тестовых векторов для полученной схемы позволяют оценить время тестирования и коэффициент тестового покрытия. Если необходимые параметры получены, либо достигнут предел заполнения элементов на кристалле,

то далее проектируется топология устройства. Если же необходимый коэффициент покрытия не достигнут, либо есть необходимость сократить время тестирования и при этом пространство для дополнительных триггеров есть, можно изменить параметры скан-схемы [19], либо дополнительно дублировать триггера в критических путях. Маршрут проектирования согласно изложенной методике приведен на рис. 4.

#### VI. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ СКАН-СХЕМ СБИС

Предложенная методика была использована при проектировании средств тестирования семи ІР-блоков: 64-разрядного микропроцессора ядра (cpu), контроллера 2d графики (2d), контроллера Ethernet 10/100/1000 Мбит/с (eth), контроллера PCI-E 2.0 8x (рсіе 8x), контролера последовательного RapidIO 4X с частотой передачи 3,125 Гбит/с (rio), контролера SATA 3 Гбит/с (sata) и контроллера USB 2.0 (usb). Также согласно методике были спроектированы средства тестирования трёх систем-на-кристалле (SoC): 64разрядного микропроцессора архитектурой КОМДИВ последовательными встроенными каналами RapidIO (proc), шестиканального коммутатора высокоскоростных последовательных каналов RapidIO 10 Гбит/с (smpo) и шестиканального коммутатора PCI Express 2.0 (basis). Вышеперечисленные СБИС отличаются количеством триггеров, объемом ОЗУ, количеством встроенных заказных блоков, количеством доменов синхросигналов, рабочими частотами. площадью комбинационной и триггерной логики. Все СБИС стандартных ячейках синтезировались на библиотеки элементов TSMC с проектными нормами 65 нм, а также со встроенными интерфейсными приёмопередатчиками, заказными блоками и блоками встроенной памяти ОЗУ. Параметры всех схем приведены в табл. 2.

Все вышеперечисленные СБИС были исследованы на предмет трудно тестируемых узлов, в результате были получены множества узлов L с низкой тестируемостью для каждой СБИС.

Таблица 2

Параметры модифицируемых СБИС

| Проект Количество триггеров, тысячи |           | Площадь,                 | Количество портов        |       |              |      |

|-------------------------------------|-----------|--------------------------|--------------------------|-------|--------------|------|

|                                     | Триггеров | Комбинационной<br>логики | ОЗУ и заказных<br>блоков | Общая | ввода/вывода |      |

| cpu                                 | 96,2      | 1,04                     | 2,98                     | 6,58  | 10,59        | 840  |

| eth                                 | 31,2      | 0,33                     | 0,23                     | 2,03  | 2,59         | 602  |

| pcie_8x                             | 98,3      | 1,05                     | 0,90                     | 1,23  | 3,18         | 3241 |

| rio                                 | 65,0      | 0,71                     | 0,91                     | 0,35  | 1,96         | 1638 |

| sata                                | 14,0      | 0,15                     | 0,21                     | 0,11  | 0,47         | 2465 |

| usb                                 | 25,8      | 0,28                     | 0,32                     | 3,51  | 4,11         | 617  |

| 2d                                  | 6,0       | 0,06                     | 0,07                     | 0,65  | 0,79         | 1857 |

| proc                                | 513,8     | 6,21                     | 8,55                     | 43,18 | 57,95        | 639  |

| smpo                                | 344,8     | 3,79                     | 4,06                     | 51,78 | 59,62        | 311  |

| basis                               | 187,6     | 2,20                     | 2,77                     | 22,31 | 27,28        | 226  |

Порог  $d_{max}$  по количеству дополнительно введённых элементов для нужд средств тестирования был задан равным 2% от числа всех триггеров СБИС, что является приемлемым значением роста тестовой логики [20]. После чего, согласно вышеописанному алгоритму, с заданным порогом  $d_{max}$  были получены множества триггеров D для каждой схемы, все элементы которых были дублированы.

Затем в каждой из полученных СБИС были созданы средства скан-тестирования (скан-схемы) с [21]. маршрут компрессией Описанный проектирования системы тестирования СБИС реализован в CAIIP Synopsys DFT Compiler. Параметры полученных схем, такие как количество внутренних скан-цепей и их длина, разрядность внешней шины тестовых данных, а также количество введённых триггеров в процессе дублирования триггеров приведены в табл. 3. Рост площади логики СБИС, вызванный введением дополнительной логики, рассчитан после оптимизаций схем по площади и быстродействию. В среднем рост площади составил 0.38%.

Проведено моделирование полученных скан-схем. Тестовые последовательности были созданы с помощью инструмента ATPG (Automatic Test Pattern Generation) – Synopsys Tetramax.

В итоге определены параметры скан-схем: тестовое покрытие и количество тестовых векторов. Исходя из частоты тестового синхросигнала 10 МГц, длины сканцепей и количества векторов было рассчитана длительность тестирования каждой СБИС (см. табл. 4). тестирования скан-схем с дублированием функциональных триггеров потребовалось 4,8-39,1% меньше тестовых последовательностей достижения заданного тестового покрытия, исходным скан-схемам без дублирования, в среднем по всем исследуемым проектам – на 16,1% меньше. С введением дополнительных триггеров выросли длины скан-цепей в схемах, что привело к увеличению длительности прохождения каждого тестового вектора. Тем не менее за счёт сокращения количества векторов время тестирования сократилось на величины от 3,3% (ІР-блок гіо) до 37,1% (СБИС ргос), в среднем на 14.4%.

Таблица 3 Параметры скан-схем СБИС

| Проект  | Количество скан-<br>цепей | Разрядность шины данных скан-схем, входная/выходная | , ,       | епей скан-схем,<br>геров | Количество<br>введённых | Рост общей площади логики, % |

|---------|---------------------------|-----------------------------------------------------|-----------|--------------------------|-------------------------|------------------------------|

|         |                           |                                                     | без дубл. | с дубл.                  | триггеров               |                              |

| cpu     | 164                       | 6/6                                                 | 586       | 598                      | 1828                    | 0,16                         |

| eth     | 51                        | 5/5                                                 | 612       | 622                      | 505                     | 0,21                         |

| pcie_8x | 164                       | 6/6                                                 | 601       | 609                      | 1411                    | 1,18                         |

| rio     | 111                       | 6/6                                                 | 587       | 598                      | 1276                    | 0,97                         |

| sata    | 23                        | 4/4                                                 | 610       | 622                      | 254                     | 0,09                         |

| usb     | 43                        | 5/5                                                 | 602       | 618                      | 684                     | 0,14                         |

| 2d      | 10                        | 3/3                                                 | 595       | 615                      | 177                     | 0,47                         |

| proc    | 2000                      | 10/10                                               | 346       | 351                      | 7207                    | 0,36                         |

| smpo    | 1000                      | 10/10                                               | 252       | 260                      | 5018                    | 0,09                         |

| basis   | 1000                      | 9/9                                                 | 189       | 193                      | 3725                    | 0,14                         |

Таблица 4

Результаты моделирования скан-схем СБИС

| Проект  | Тестовое<br>покрытие, % | Количество тестовых<br>векторов |         | Время тестирования скан-схем, с |         | Сокращение времени тестирования, % |

|---------|-------------------------|---------------------------------|---------|---------------------------------|---------|------------------------------------|

|         |                         | без дубл.                       | с дубл. | без дубл.                       | с дубл. |                                    |

| cpu     | 93,6                    | 4840                            | 4418    | 0,284                           | 0,264   | 7,0                                |

| eth     | 94,1                    | 1672                            | 1565    | 0,102                           | 0,097   | 4,9                                |

| pcie_8x | 95,3                    | 5365                            | 5077    | 0,322                           | 0,309   | 4,0                                |

| rio     | 96,6                    | 2270                            | 2138    | 0,133                           | 0,128   | 3,8                                |

| sata    | 86,2                    | 816                             | 593     | 0,050                           | 0,037   | 26,0                               |

| usb     | 91,4                    | 504                             | 480     | 0,030                           | 0,029   | 3,3                                |

| 2d      | 79,6                    | 421                             | 261     | 0,025                           | 0,016   | 36,0                               |

| proc    | 91,6                    | 55236                           | 33656   | 1,391                           | 0,875   | 37,1                               |

| smpo    | 90,0                    | 19374                           | 14993   | 0,670                           | 0,526   | 21,5                               |

| basis   | 91,5                    | 10401                           | 10147   | 0,196                           | 0,195   | 0,5                                |

#### VII. ЗАКЛЮЧЕНИЕ

Предложен метод увеличения тестируемости и взаимных снижения конфликтов неисправностей цифровой СБИС. который заключается дублировании триггеров в составе трудно тестируемых путей. Показано, что дублирование триггеров в путях со сходящимися разветвлениями позволяет увеличить тестируемость узлов этих путей, а дублирование триггеров-источников логических путей позволяет снизить число взаимных конфликтов неисправностей во всех узлах этих путей. Предложенная методика дублирования отдельных триггеров была реализована в 3 проектах СБИС и 7 проектах ІР-блоков при проектировании средств скан-тестирования компрессией. Результаты показали снижение времени тестирования в среднем на 14,4% при аппаратурных затратах, не превышающих 1,2% общей площади СБИС.

#### ЛИТЕРАТУРА

- [1] Abramovici M., Breuer M. A. and Friedman A.D. Digital Systems Testing and Testable Design, Computer Science Press, 1990. 364-366 p.

- [2] Touba N. A. Survey of test vector compression techniques // IEEE Design & Test of Computers. – July-August 2006. – Vol. 23. №4. - P. 294–303.

- [3] Kapur R., Historical perspective on scan compression // IEEE Design & Test of Computers. March-April 2008. Vol. 25. №2. P. 114-120.

- [4] Hapke F., Redemund W., Glowatz A., Rajski J., Reese M., Hustava M., Keim M., Schloeffel J., Fast A. Cell-Aware Test // IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.- Sep. 2014. - Vol. 33. - №9. – P. 1396-1409.

- [5] Acero C., Feltham D., Hapke F., Moghaddam E., Mukherjee N., Neerkundar V., Patyra M., Rajski J., Tyszer J., Zawada J. Embedded deterministic test points for compact cell-aware tests // Test Conf ITC 2015 IEEE Int. Oct. 2015. P. 1-8.

- [6] Savir J. Good Controllability and Observability Do Not Guarantee Good Testability // IEEE Transactions on Computers. - 1983. - V. 32. №12. - P.1198-1200.

- [7] Robert M.W., Lala P. K. Algorithm to Detect Reconvergent Fanout in Logic Circuits // IEEE Proceedings. 1987. Vol.134. №2. P.105-111.

- [8] Xu S., Edirisuriya E. A new way of detecting reconvergent fanout branch pairs in logic circuits // Asian Test Symposium (ATS'04). 2004. P. 354-357.

- [9] Pomeranz I., Reddy S.M. Test-point insertion to enhance test compaction for scan designs // Proc. ICDSN. – 2000. - P. 375-381.

- [10] Geuzebroek M.J., Linden J.T., Goor A.J. Test point insertion that facilitates ATPG in reducing test time and data volume // Proc. ITC. 2002. P. 138-147.

- [11] Kumar A., Rajski J., Reddy S.M., Rinderknecht T. On the Generation of Compact Deterministic Test Set for BIST Ready Designs // Asian Test Symposium. – 2013. - P. 201-206.

- [12] Acero C., Feltham D., Liu Y., Moghaddam E., Mukherjee N., Patyra M., Rajski J., Reddy S.M., Tyszer J., Zawada J. Embedded deterministic test points // IEEE Transactions on Very Large Scale Integration (VLSI) Systems. – 2017. - P. 1-13.

- [13] Ren H., Kusko M., Kravets V., Yaari R. Low cost test point insertion without using extra registers for high performance design // Proc. ITC. - 2009. – P. 1-8.

- [14] Yang J., Touba N. A., Nadeau-Dostie B. Test Point Insertion with Control Points Driven by Existing Functional Flip-Flops // IEEE Transactions on Computers. 2012. V. 61. P. 1473-1483.

- [15] Srivastava A., Kastner R., Sarrafzadeh M. Timing driven gate duplication: Complexity issues and algorithms // Proc. ICCAD. - 2000. - P. 447-450.

- [16] Goessel M., Singh A., Sogomonyan E. Scan-path with directly duplicated and inverted duplicated registers // Proceedings 20th IEEE VLSI Test Symposium. 2002. P. 47-52

- [17] Savir J. Syndrome-testable design of combinational circuits // IEEE Transactions on Computers, 1980. V.29. - P. 442-451.

- [18] Liu Y., Moghaddam E., Mukherjee N., Reddy S. M., Rajski J., Tyszer J. Minimal area test points for deterministic patterns // Proc. ITC. Nov. 2016. Р. 1-7

[19] Ладнушкин М.С. Снижение аппаратурных затрат и

- [19] Ладнушкин М.С. Снижение аппаратурных затрат и увеличение коэффициента компрессии средств тестирования константных неисправностей КМОП цифровых СБИС // VII Всероссийская научнотехническая конференция «Проблемы разработки перспективных микро- и наноэлектронных систем 2016». Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2016. Ч.2, С. 68-75

- [20] Acero C., Feltham D., Patyra M. et al. On new test points for compact cell-aware tests // IEEE Des. Test. - Dec. 2016. - Vol. 33 №6. - P. 7-14.

- [21] Wohl P., Waicukauski J.A., Ramnath S. Fully X-Tolerant Combinational Scan Compression // International Test Conference. - 2007. - P. 1-10.

# Register Duplication for Scan Compression Designs

### M.S. Ladnushkin

Department of Russian Academy of Sciences Institute of System Researches of CAD Systems, maximsl@gmail.com

Abstract — Volumes of test data are growing and test compression schemes are not enough for today's challenges such as growth of length of logic paths and higher amount of blocking nonequivalent faults during test. These factors cause not only inflation of test sets and new requirements of storage but also increase test application time. Test point are widely used to improve testability and decrease number of blocking faults by inserting controlling and observing additional logic.

Method of duplicating cells is known as a timing improving approach which is used during topology planning. In this paper it was shown that duplicating of functional register can improve testability if there are reconvergent fanouts on trigger's output. Also it was shown that duplicating of register can reduce number of blocking faults on each combinational cell in all output paths of that register.

Complexity analysis of logic paths of several VLSI's was presented. It was observed that more than 70% of all paths have one source. But there were a few paths with 7400 startpoints in one of the designs. Such paths are the most hard to test paths so duplicating of startpoint triggers of these paths would have maximum effect on testability.

An algorithm of selecting registers for duplication with long output paths was proposed. Experiments on 10 industrial projects show average test time reduction 14,4% while area overhead was less than 1,2%.

Keywords — scan testing, register duplicating, test compression, modeling.

### REFERENCES

- [1] Abramovici M., Breuer M. A. and Friedman A.D. Digital Systems Testing and Testable Design, Computer Science Press, 1990. 364-366 p.

- [2] Touba N. A. Survey of test vector compression techniques // IEEE Design & Test of Computers. – July-August 2006. – Vol. 23. №4. - P. 294–303.

- [3] Kapur R., Historical perspective on scan compression // IEEE Design & Test of Computers. March-April 2008. Vol. 25. №2. P. 114-120.

- [4] Hapke F., Redemund W., Glowatz A., Rajski J., Reese M., Hustava M., Keim M., Schloeffel J., Fast A. Cell-Aware Test // IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.- Sep. 2014. Vol. 33. №9. P. 1396-1409.

- [5] Acero C., Feltham D., Hapke F., Moghaddam E., Mukherjee N., Neerkundar V., Patyra M., Rajski J., Tyszer J., Zawada J. Embedded deterministic test points for compact cellaware tests // Test Conf ITC 2015 IEEE Int. - Oct. 2015. -P. 1-8.

- [6] Savir J. Good Controllability and Observability Do Not Guarantee Good Testability // IEEE Transactions on Computers. - 1983. - V. 32. №12. - P.1198-1200.

- [7] Robert M.W., Lala P. K. Algorithm to Detect Reconvergent Fanout in Logic Circuits // IEEE Proceedings. - 1987. -Vol.134. №2. - P.105-111.

- [8] Xu S., Edirisuriya E. A new way of detecting reconvergent fanout branch pairs in logic circuits // Asian Test Symposium (ATS'04). - 2004. - P. 354-357.

- [9] Pomeranz I., Reddy S.M. Test-point insertion to enhance test compaction for scan designs // Proc. ICDSN. – 2000. - P. 375-381.

- [10] Geuzebroek M.J., Linden J.T., Goor A.J. Test point insertion that facilitates ATPG in reducing test time and data volume // Proc. ITC. – 2002. - P. 138-147.

- [11] Kumar A., Rajski J., Reddy S.M., Rinderknecht T. On the Generation of Compact Deterministic Test Set for BIST Ready Designs // Asian Test Symposium. – 2013. - P. 201-206.

- [12] Acero C., Feltham D., Liu Y., Moghaddam E., Mukherjee N., Patyra M., Rajski J., Reddy S.M., Tyszer J., Zawada J. Embedded deterministic test points // IEEE Transactions on Very Large Scale Integration (VLSI) Systems. – 2017. - P. 1-13.

- [13] Ren H., Kusko M., Kravets V., Yaari R. Low cost test point insertion without using extra registers for high performance design // Proc. ITC. - 2009. – P. 1-8.

- [14] Yang J., Touba N. A., Nadeau-Dostie B. Test Point Insertion with Control Points Driven by Existing Functional Flip-Flops // IEEE Transactions on Computers. 2012. V. 61. P. 1473-1483.

- [15] Srivastava A., Kastner R., Sarrafzadeh M. Timing driven gate duplication: Complexity issues and algorithms // Proc. ICCAD. - 2000. - P. 447-450.

- [16] Goessel M., Singh A., Sogomonyan E. Scan-path with directly duplicated and inverted duplicated registers // Proceedings 20th IEEE VLSI Test Symposium. 2002. P. 47-52.

- [17] Savir J. Syndrome-testable design of combinational circuits // IEEE Transactions on Computers, 1980. V.29. - P. 442-451.

- [18] Liu Y., Moghaddam E., Mukherjee N., Reddy S. M., Rajski J., Tyszer J. Minimal area test points for deterministic patterns // Proc. ITC. Nov. 2016. P. 1-7

- [19] Ladnushkin M.S. Snizhenie apparaturnyh zatrat i uvelichenie kojefficienta kompressii sredstv testirovanija konstantnyh neispravnostej KMOP cifrovyh SBIS (Reducing area and increasing compression ratio of scan compression system for digital VLSI using stuck-at fault model) // VII Vserossijskaja nauchno-tehnicheskaja konferencija «Problemy razrabotki perspektivnyh mikro- i nanojelektronnyh sistem 2016». Sbornik trudov / pod obshh. red. akademika RAN A.L. Stempkovskogo. M.: IPPM RAN, 2016. Ch.2, S. 68-75.

- [20] Acero C., Feltham D., Patyra M. et al. On new test points for compact cell-aware tests // *IEEE Des. Test.* Dec. 2016. Vol. 33 №6. P. 7-14.

- [21] Wohl P., Waicukauski J.A., Ramnath S. Fully X-Tolerant Combinational Scan Compression // International Test Conference. - 2007. - P. 1-10.