# Особенности импульсных помех в КМОП комбинационных логических элементах при сборе заряда с треков одиночных частии

Ю.В. Катунин $^1$ , В.Я. Стенин $^{1,2}$

<sup>1</sup>НИИ системных исследований Российской академии наук, г. Москва <sup>2</sup>Национальный исследовательский ядерный университет "МИФИ", г. Москва katunin@cs.niisi.ras.ru, vystenin@mephi.ru

Аннотация — В работе приводятся результаты ТСАД-SPICE гибридного моделирования импульсных помех, возникающих в комбинационных КМОП элементах И и ИЛИ в составе двух мажоритарных элементов. Средствами ТСАД моделировались процессы генерации носителей заряда на треке частицы в кремнии и процессы сбора заряда транзисторами в логических элементах И и ИЛИ. Даны оценки длительности импульсов помех и их уменьшения в логических элементах по КМОП 65-нм объемной технологии с неглубокой траншейной изоляцией групп транзисторов. Моделирование проведено при линейной передаче энергии частицей на трек 60 МэВ·см<sup>2</sup>/мг с направлением треков по нормали к поверхности кристалла. Когда заряд с трека частицы собирают запертые транзисторы группы И-НЕ (ИЛИ-НЕ), то они переходят в открытое состояние (в частности, в инверсное смещение), что образует импульс помехи на узле И-НЕ (ИЛИ-НЕ), который запирает транзистор выходного инвертора элемента И (ИЛИ). Запертый транзистор инвертора, собирая заряд с того же трека, компенсирует часть длительности импульса помехи при передаче его на выход элемента И (ИЛИ). Дублирование инвертора расположением основных и дополнительных транзисторов инвертора на граничных топологических групп транзисторов И-НЕ (ИЛИ-НЕ) способствует снижению длительности помех при сборе заряда с трека одиночной частицы. С учётом коррекции, длительности помех, возникающих в мажоритарном элементе, находятся в диапазоне 90-350 пс.

Ключевые слова — импульс помехи, комбинационный элемент, мажоритарный элемент, моделирование, одиночная ионизирующая частица, передача энергии, трек частицы.

#### I. Введение

КМОП комбинационные логические элементы являются основой кодирующих, декодирующих устройств и мажоритарной логики. Моделирование эффектов воздействия одиночных ионизирующих частиц с использованием приборных физических моделей (physics-based device models) как двумерных (2D), так и трехмерных (3D) посвящен ряд работ, в которых было, например, предсказано [1] существенное снижение помехоустойчивости КМОП логики по

объемной технологии до уровня линейной передачи энергии частицы (linear energy transfer — LET) на трек 2 МэВ·см²/мг при снижении проектной нормы 100 нм КМОП. Установлен моделированием [2] эффект перехода NМОП транзисторов КМОП инвертора с проектной нормой 0.18 мкм по объемной технологии в инверсный режим смещения при LET > 3 МэВ·см²/мг с увеличением длительности импульса помехи до 300-500 пс при LET = 30 МэВ·см²/мг.

Систематизированные физические, технологические конструктивные результаты исследований [3] направлены частично на учет и подавление импульсов помех, приводящих к ложным сигналам в цепях микросхем. При проектных нормах менее 100 нм КМОП заметно проявилось влияние диффузионного переноса носителей индуцированных на треке, на транзисторы смежных элементов. При этом общий сбор заряда может снизить длительности импульсных помех (effect of quenching), что было показано в работах [4].

Показано [5], что КМОП тройной мажоритарный элемент (Triple Majority Gate – TMG) на основе только элементов И-НЕ при топологии с чередованием транзисторов последовательно соединенных элементов И-НЕ имеет улучшенную помехоустойчивость по сравнению с стандартным вариантом топологии такого элемента.

Целью данной работы является моделирование средствами ТСАО базовых элементов с логикой И и ИЛИ в составе вариантов мажоритарных элементов по проектной норме объемный 65-нм КМОП количественных оценок длительностей получения импульсов реальных помех возможностей сокращения длительности помех за счет совместного сбора заряда транзисторами, выполненными группой в области кремния, окруженной мелкой траншейной изоляцией в КМОП элементах по объемной технологии.

Такие данные необходимы для повышения сбоеустойчивости коммуникационных контроллеров и микропроцессоров высокопроизводительных ЭВМ.

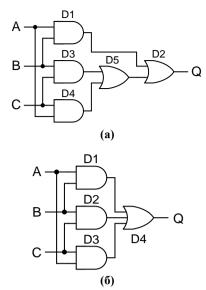

Рис. 1. Функциональные схемы мажоритарных элементов: (а) на логических элементах 2И (D1, D3, D4) и 2ИЛИ (D2, D5); (б) на логических элементах 2И (D1-D3) и 3ИЛИ (D4)

### II. ТРОЙНОЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ НА И И ИЛИ ЭЛЕМЕНТАХ

На рис. 1 приведены два варианта тройного мажоритарного элемента: на рис. 1а на основе схем двухвходовых КМОП элементов И и ИЛИ, а на рис. 1б на основе трех двухвходовых КМОП элементов с логикой И трех входного КМОП элемента ИЛИ.

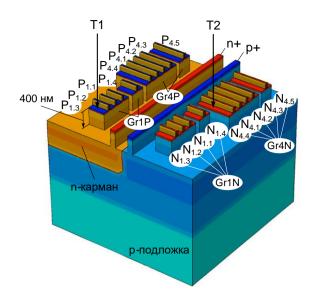

На рис. 2 приведена структура приборной 3D TCAD физической модели КМОП логических элементов D1 (2И) и D4 (3ИЛИ) мажоритарного элемента, схема которого на рис. 1б. Приборная структура использована при моделировании сбора заряда транзисторами с трека; направления треков по нормали к поверхности модели (примеры треков обозначены как T1 и T2).

В работе проведено TCAD-SPICE гибридное моделирование КМОП мажоритарного элемента (рис. 1б), при котором средствами TCAD моделировались процессы генерации носителей заряда при передаче им энергии с трека в кремнии и процессы сбора заряда транзисторами в элементах D1 (И) и D4 (ИЛИ). Средствами SPICE моделировались два элемента D2 и D3, которые обеспечивали передачу входных сигналов на элемент D4 (ИЛИ).

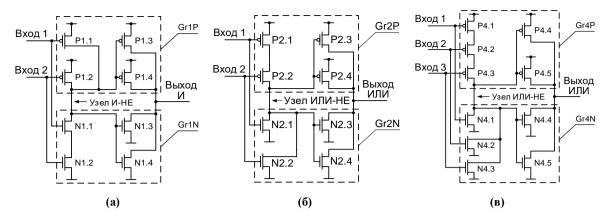

На рис. 3 приведены схемы комбинационных КМОП логических элементов: элемента 2И на рис. 3а, элемента 2ИЛИ на рис. 3б и элемента 3ИЛИ на рис. 3в. Первая цифра в обозначениях транзисторов соответствует номеру логического элемента, а вторая цифра – номеру транзистора в элементах.

На рис. За приведена схема элемента 2И, состоящая из элемента И-НЕ на транзисторах N1.1, N1.2, P1.1, P1.2 и инвертора на транзисторах N1.3, N1.4, P1.3, P1.4. На рис. Зб дана схема 2ИЛИ, которая состоит из элемента

Рис. 2. Приборная 3D TCAD физическая модель КМОП логических элементов D1 и D4 на рис. 16 при моделировании сбора заряда транзисторами с трека одиночной ионизирующей частицы

ИЛИ-НЕ на транзисторах N2.1, N2.2, P2.1, P2.2 и инвертора на транзисторах N2.3, N2.4, P2.3, P2.4. Выход группы ИЛИ-НЕ является внутренним узлом элемента 2ИЛИ и входом инвертора элемента 2ИЛИ. Элемент 3ИЛИ (D4 на рис. 16) состоит из элемента ИЛИ-НЕ на транзисторах N4.1–N4.3, P4.1–P4.3 и инвертора на транзисторах N4.4, N4.5, P4.4, P4.5.

Элементы И и ИЛИ состоят из двух групп транзисторов, одна группа из NMOП транзисторов Gr1N на рис. За (Gr2N на рис. Зб и Gr4N на рис. Зв), а вторая состоит из РМОП транзисторов Gr1P на рис. За (Gr2P на рис. Зб и Gr4P на рис. Зв).

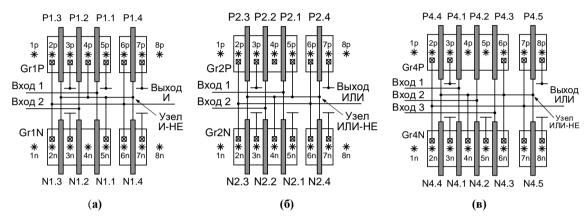

На рис. 4 приведены эскизы топологий элементов 2И, 2ИЛИ и ЗИЛИ. На рис. 4а приведен эскиз топологии элемента 2И (D1 на рис. 1а и рис. 1б), на рис. 4б дан эскиз топологии элемента 2ИЛИ (D2 на рис. 1а), а на рис. 4б приведен эскиз топологии элемента ЗИЛИ (D4 на рис. 1б).

Транзисторы инверторов элементов И и ИЛИ в конструкции элементов продублированы так, что NMOП транзисторы N1.3 и N1.4 и РМОП транзисторы P1.3, P1.4 в элементе И (рис. 4а) расположены симметрично с разных сторон от NMOП транзисторов элемента И-НЕ в группе Gr1N, а также от РМОП транзисторов элемента И-НЕ в группе Gr1P (рис. 4а).

Аналогично расположены пары NMOП транзисторов и РМОП транзисторов инвертора на эскизе топологии элемента 2ИЛИ на рис. 4б и эскизе топологии элемента 3ИЛИ на рис. 4в. Это сделано для повышения эффективности коррекции импульсов помех сбором заряда транзисторами инвертора при разном удалении точек входа треков от транзисторов инвертора.

Рис. 3. Схемы комбинационных КМОП логических элементов: (а) 2И; (б) 2ИЛИ; (в) ЗИЛИ

Рис. 4. Эскизы топологии КМОП логических элементов: (а) 2И; (б) 2ИЛИ; (в) ЗИЛИ

### III. МОДЕЛИРОВАНИЕ СБОРА ЗАРЯДА С ТРЕКА ЧАСТИЦЫ ТРАНЗИСТОРАМИ ЭЛЕМЕНТОВ И И ИЛИ

Моделирование сбора транзисторами заряда с треков одиночных частиц проведено с использованием 3D TCAD физических моделей КМОП транзисторов [6] по проектной норме 65-нм КМОП объемной технологии. Как тестовое воздействие принят сбор заряда с трека, направленного по нормали к поверхности приборной части модели элемента (примеры треков Т1 и Т2 даны на рис. 2).

Все транзисторы на рис. 2 соответствуют транзисторным группам элемента 2И и ЗИЛИ. Ширина каналов транзисторов элемента 2И равна 400 нм, а ширина каналов транзисторов элемента ЗИЛИ равна 800 нм. Конструкция элементов И и ИЛИ состоит из областей объединенных транзисторов, окруженных траншейной изоляцией с глубиной 400 нм (shallow trench isolation — STI), которая убрана на рис. 2 для обеспечения наглядности компоновки транзисторов. Области с обозначениями n+ и p+ на рис. 4 являются фрагментами охранных полос.

Полные размеры 3D приборной структуры составляют 6.4 мкм × 10.9 мкм при толщине подложки 3.0 мкм. Энергетическая составляющая генерации заряда на треке характеризуется линейной передачей энергии частицей на трек – (linear energy transfer – LET).

При моделировании использовались треки с LET =  $60~\text{M}{^{\circ}}\text{B}{^{\circ}}\text{см}^2/\text{м}\text{г}$ . Результаты моделирования получены с использованием симулятора Sentaurus Device при температуре  $25^{\circ}\text{C}$  и питания 1.0~B.

## IV. Результаты моделирования импульсных помех, образующихся на выходах логических элементов И и ИЛИ

### А. Треки через стоки транзисторов группы Gr1P элемента 2И

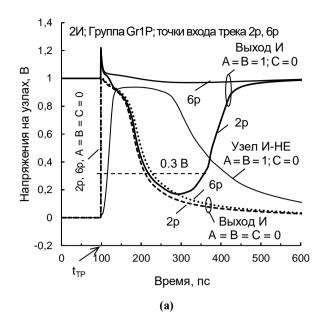

На рис. 5 приведены зависимости напряжений на узлах элемента 2И для точек входа трека в РМОП транзисторы группы Gr1P при сигналах на входах мажоритарного элемента на рис. 1a: A = B = 1; C = 0. Линейная передача энергии на трек LET =  $60 \text{ M} \cdot \text{B} \cdot \text{cm}^2/\text{Mr}$ , начало сбора заряда при  $t_{TP} = 100 \text{ пс}$ . Зависимости на рис. 5а даны для точек входа трека 2р и 6р (рис. 3а) в транзисторы инвертора, на рис. 5б для точек трека 3р, 4р и 5р в транзисторы группы И-НЕ элемента 2И.

Треки через РМОП транзисторы инвертора. Когда треки с точками входа 2р и 6р генерируют заряд в РМОП транзисторы инвертора, часть заряда диффундирует в область общих стоков транзисторов Р1.1, Р1.2 группы И-НЕ, а часть собирает транзистор Р1.3 или Р1.4 инвертора (рис. 3а и 4а).

При входных сигналах ТМG элемента A=B=1; C=0 сбор заряда транзисторами P1.3 и P1.4 инвертора переводит эти транзисторы из исходного открытого состояния в инверсное смещение и заряжает узел выхода И до напряжения 1.2 В (рис. 5а). При входных сигналах A=B=1; C=0 к моменту t=300 пс завершается сбор заряда транзисторами P1.1, P1.2 группы И-НЕ и напряжение на узле И-НЕ начинает снижаться, что приводит к увеличению напряжения на выходе И, что образует импульс помехи на выходе И с амплитудой 0.82 В при t=300 пс, после чего выход элемента И возвращается к уровню 1 В.

На рис. 5а эта зависимость дана сплошной линией с маркером 2р. При треке с точкой входа 6р оба транзистора инвертора до  $t=200\,\mathrm{nc}$  остаются в инверсном смещении (на рис. 5а зависимость с маркером 6р при входах A=B=1; C=0).

При входных сигналах A=B=C=0 в исходном состоянии РМОП транзисторы Р1.1, Р1.2 узла И-НЕ открыты, а РМОП транзисторы Р1.3, Р1.4 инвертора заперты. Сбор заряда с трека с точкой входа 2р и транзистором Р1.4 с трека с точкой входа 6р происходит до момента 300 пс также, как и при A=B=1; C=0. После 300 пс идет возврат выхода И в исходное состояние нуля 0 В.

Треки через РМОП транзисторы группы 2И-НЕ. При возникновении трека с точкой входа 3р (рис. 4а) сбор заряда с него запертыми РМОП транзисторами Р1.2, Р1.1 группы И-НЕ увеличивает напряжение на узле И-НЕ с 0 до 1–1.15 В, что запирает РМОП транзисторы Р1.3, Р1.4 инвертора, а NМОП транзисторы N1.3, N1.4 открывает (см. рис. 3а).

В случае, когда трек с точкой входа 3р проходит через общую область истоков транзистора P1.2 группы И-НЕ и транзистора P1.3 инвертора (рис. 3а), заряд (дырки) с этого трека поступает в область стока транзистора P1.3 инвертора, сразу заряжая емкость выходного узла элемента И до напряжения 0.9 В, что исключает переключение инвертора по затвору транзистора P1.3 (зависимость Выход И с маркером 3р на рис. 56).

Затем узел выхода И начинает разряжаться через открытые NMOII транзисторы N1.3, N1.4 инвертора, одновременно незначительно заряжаясь сбором дырок с трека 3р через обратно смещенный стоковый *pn* переход транзистора P1.3 инвертора. Этот процесс удерживает уровень напряжения на выходе И с небольшим снижением около 40 пс (рис. 56).

Затем напряжение на выходе И снижается до 0.17 В, что соответствует амплитуде импульса помехи отрицательной полярности с маркером 3р. К этому времени завершается сбор заряда, узел И-НЕ начинает разряжаться до напряжения общей шины 0 В, а инвертор повышает напряжение на выходе И до 1 В.

Точки входа треков 4р и 5р отстоят на 0.25 мкм и 0.5 мкм от точки входа 3р (рис. 4а), заряд с трека от этих треков диффундирует с задержкой к транзисторам Р1.3,

Рис. 5. Зависимости напряжений на узлах элемента 2И при сборе заряда с треков с точками входа в группу Gr1P, LET =  $60 \text{ M} \cdot \text{BP} \cdot \text{cm}^2/\text{mr}$ : (a) точки входа 2р и 6р в инвертор при A = B = 1; C = 0 A = B = C = 0; (б) точки входа трека 3р, 4р и 5р в элемент И-НЕ, A = B = 1, C = 0

Р1.4 инвертора, и инвертор в отличие от сбора заряда с трека 3р успевает переключиться. При переключении инвертора напряжение на его выходе снижается до 0.08 В, что образует фронт импульса помехи отрицательной полярности на выходе И (зависимости с метками 4р и 5р на рис. 5б).

Затем запертые транзисторы P1.3, P1.4 инвертора начинают собирать заряд (дырки) с трека, что повышает напряжение на выходе И и образует встроенный импульс положительной полярности после фронта отрицательной полярности. Этот эффект несколько снижает длительность импульса помехи, если отсчитывать длительность на уровне 0.1-0.15 В.

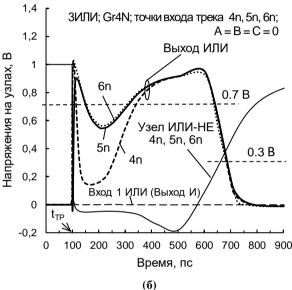

Рис. 6. Зависимости напряжений на узлах элемента 2ИЛИ при сборе заряда с треков с точками входа в группу Gr2N, LET =  $60 \text{ M}_{2}\text{B}_{2}\text{-cm}^{2}/\text{Mr}$ : (a) точки входа трека 2n и 6n при входах A=B=C=0 и A=B=1; C=0; (б) точки входа трека 3n, 4n и 5n в группу ИЛИ-НЕ при входах A=B=C=0

### В. Треки через стоки транзисторов группы Gr2N элемента 2ИЛИ

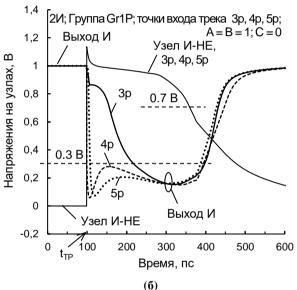

На рис. 6 приведены зависимости напряжений на узлах элемента ИЛИ для точек входа трека в NMOII транзисторы группы Gr1N при сигналах на входах TMG (рис. 16) элемента A = B = C = 0, линейная передача энергии на трек LET = 60~MэB·с $\text{cm}^2$ /мг, начало сбора заряда при  $t_{TP}$  = 100~nc..

Треки через NMOП транзисторы инвертора. Когда треки с точками входа 2n и 6n (рис. 4б) генерируют заряд в NMOП транзисторы инвертора, то сбор заряда транзистором N1.3 или N1.4 инвертора переводит оба

транзистора в инверсное смещение с напряжением - 0.4 В на выходе ИЛИ (рис. 6а). При этом собирают заряд и транзисторы N1.1, N1.2 группы ИЛИ-НЕ, что снижает напряжение на узле ИЛИ-НЕ с 1 В до 0.

Из состояния инверсного смещения транзисторы N1.3 или N1.4 инвертора (рис. 36) начинает выводить ток открытых РМОП транзисторов P1.3, P1.4. К моменту времени t=410 пс сбор заряда прекращается транзисторами N1.1, N1.2 группы ИЛИ-НЕ и напряжение на узле ИЛИ-НЕ начинает возрастать.

При входных сигналах A=B=C=0 после t=410 пс напряжение на узле ИЛИ-НЕ и входе инвертора начинает повышаться, что приводит к снижению напряжения на выходе ИЛИ до уровня 0~B.

При входных сигналах A=B=1; C=0 сбор заряда запертым транзистором P1.3 с трека с точкой входа 2n, так и транзистором P1.4 с трека с точкой входа 6n происходит одинаково до t=400 пс, как и в случае A=B=C=0. После момента времени 400 пс рост напряжения на выходе ИЛИ продолжается до возврата в исходное состояние 1 B.

Треки через РМОП транзисторы группы 2ИЛИ-НЕ. При возникновении трека сбор заряда с него запертыми NМОП транзисторами N1.1, N1.2 группы ИЛИ-НЕ резко снижает напряжение на узле ИЛИ-НЕ с 1 В и переводит эти транзисторы в инверсное смещение, что запирает NМОП транзисторы N1.3, N1.4 инвертора, а РМОП транзисторы P1.3, P1.4 инвертора открываются (схема на рис. 36).

В случае, когда трек с точкой входа 3n проходит через общую область истоков транзистора N1.2 группы ИЛИ-НЕ и транзистора N1.3 инвертора (рис. 46), заряд (электроны) с этого трека сразу поступает в область стока транзистора N1.3 инвертора, удерживая емкость выходного узла элемента ИЛИ при напряжении 0 В до 280 пс (Выход ИЛИ с маркером 3n на рис. 66). Затем напряжение на выходе ИЛИ быстро возрастает до 0.85 В при t=435 пс, что соответствует образованию импульса помехи с маркером 3n на рис. 66.

В случае точек входа треков 4n и 5n, которые отстоят на 0.25 мкм и 0.5 мкм от точки входа 3n (рис. 4б), заряд с трека от этих треков диффундирует с задержкой до транзисторов N1.3, N1.4 инвертора, и инвертор через 15-30 пс после возникновения трека (рис. 6б) успевает переключить напряжение на выходе 2ИЛИ до уровня 0.7-0.9 В в отличие от сбора заряда с трека 3n.

При переключении инвертора напряжение на его выходе резко повышается, образуя фронт импульса помехи на выходе ИЛИ положительной полярности, но затем запертые транзисторы N1.3, N1.4 инвертора начинают собирать электроны с трека, что снижает напряжение на выходе ИЛИ до 0.05-0.06 В и образует импульс отрицательной полярности. Этот импульс укорачивает импульс помехи положительной полярности на выходе ИЛИ, что является коррекцией длительности импульса помехи.

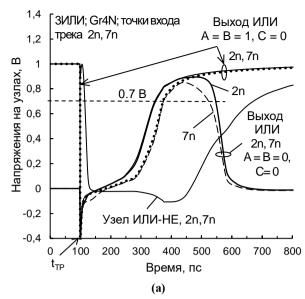

#### С. Треки через стоки транзисторов группы Gr4N элемента ЗИЛИ

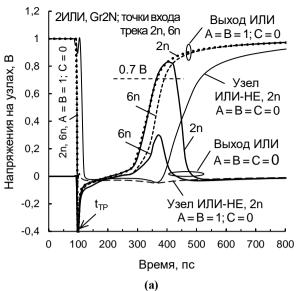

На рис. 7 приведены зависимости напряжений на узлах элемента 3ИЛИ для точек входа трека в группе NMOП транзисторов Gr4N при сигналах на TMG входах A = B = C = 0, линейная передача энергии на трек LET =  $60 \text{ M} \cdot \text{B} \cdot \text{Cm}^2 / \text{Mr}$ .

Треки через NMOП транзисторы инвертора. На рис. 7а приведены зависимости напряжений на узлах элемента ИЛИ для точек входа трека 2n и 7n в транзисторы инвертора. При сигналах на TMG входах A=B=C=0 транзисторы N4.4, N4.5 инвертора открыты, а при входных сигналах TMG A=B=1; C=0 заперты. Как открытые, так и запертые NMOП транзисторы N4.4, N4.5 инвертора при возникновении трека с точкой входа 2n или 7n кратковременно на 50 пс (рис. 7a) переходят в инверсное смещение с напряжением -(0.5-0.4) В.

Изменения напряжений на узле ИЛИ-НЕ и выходе ЗИЛИ на рис. 7 качественно повторяют зависимости на рис. 6а и рис. 6а для таких же узлов элемента 2ИЛИ для точек входа трека в транзисторы инвертора и группы ИЛИ-НЕ.

Треки через NMOП транзисторы группы ЗИЛИ-НЕ. На рис. 76 приведены зависимости напряжений на узлах элемента ЗИЛИ при сборе заряда с треков с точками входа 4n, 5n, 6n в группу ИЛИ-НЕ (группа Gr4N на рис. 4в). В момент начала сбора заряда напряжение на стоках транзисторов N4.1—N4.3 (узел ИЛИ-НЕ) резко снижается, формируя фронт импульса отрицательной полярности, после чего эти транзисторы на 460 пс переходят в инверсное смещение (рис. 7б). Инвертор преобразует этот импульс на выходе ИЛИ в импульс помехи положительной полярности, при этом запертые транзисторы N4.4, N4.5 инвертора начинают собирать заряд (электроны), что приводит к просадке импульса помехи, укорачивая ее длительность (рис. 7б).

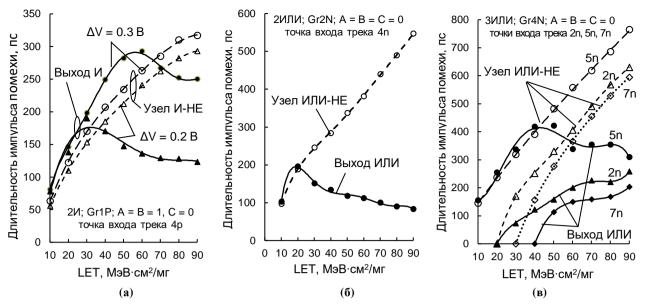

#### V. Эффективность коррекции импульсов помех в элементах И и ИЛИ

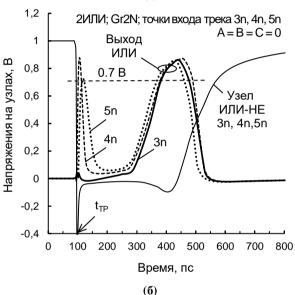

На рис. 8 приведены зависимости длительности импульсов помехи на узлах и выходе элементов 2И, 2ИЛИ и 3ИЛИ в составе ТМG с схемами на рис. 1 как функции линейного переноса энергии на трек в диапазоне от 10 до 90 МэВ·см²/мг. На рис. 8а даны зависимости для точки входа трека 4р в область РМОП транзисторов группы Gr1P при сигналах на входах ТМG A = C = 1, B = 0. Длительности импульсов помех отрицательной полярности на выходе И определенны на уровне  $\Delta V = 0.3$  В относительно напряжения общей шины, что соответствует уровню 0.7 В относительно пьедестала импульса помехи.

При увеличении переноса энергии на трек с точкой входа 4р, роста генерируемого заряда и сбора его РМОП транзисторами группы И-НЕ возрастает длительность импульса на узле И-НЕ (рис. 8а), но одновременно больше заряда диффундирует до РМОП транзисторов инвертора, сбор которого частично компенсирует

Рис. 7. Зависимости на узлах элемента ЗИЛИ при сборе заряда с треков с точками входа в группу Gr4N, LET =  $60 \text{ M} \cdot \text{B} \cdot \text{cm}^2 / \text{M} \cdot \text{I}$ : (a) точки входа трека 2n и 7n в инвертор при A = B = C = 0 и A = B = 1, C = 0; (б) точки входа 4n, 5n, 6n в группу ИЛИ-НЕ, A = B = C = 0

увеличение длительности импульса помехи на выходе И. В итоге при LET  $\geq$  60 МэВ·см²/мг длительность импульса помехи на выходе И снижается с 295 пс до 250 пс при оценке по уроню 0.3 В. Оценка по уровню 0.2 В при LET  $\geq$  30 МэВ·см²/мг дает снижение длительности помехи с значения 190 пс до значения 130 пс (рис. 8а).

На рис. 86 приведены зависимости длительности импульсов помехи для элемента 2ИЛИ, а на рис. 8в - для элемента 3ИЛИ. Зависимости на рис. 8б определены для точки входа трека 4n в область NМОП транзисторов элемента ИЛИ-НЕ группы Gr2N (рис. 46) при входных сигналах ТМG элемента A = C = B = 0. Для элемента 2ИЛИ длительность импульса помехи на выходе ИЛИ начинает снижаться после LET = 20 MэВ·см²/мг с

Рис. 8. Коррекция длительности импульсов помехи на выходах элементов И и ИЛИ в зависимости от линейной передачи энергии на трек в диапазоне от 10 до  $90 \text{ M} \cdot \text{B} \cdot \text{cm}^2/\text{Mr}$ : (а) точка входа трека 4р в группу транзисторов Gr1P элемента И при входах TMG A = B = 1, C = 0; (б) точка входа трека 4n в группу транзисторов Gr2N элемента 2ИЛИ; (в) точки входа трека 5 n, 2 n и 7 n в группу транзисторов Gr4N и в транзисторы инвертора элемента 3 иЛИ

значения 190 пс до значения 150 пс при LET = 30 MэВ·см²/мг и далее до 83 пс при LET = 90 MэВ·см²/мг. При этом снижение длительности импульса помехи на выходе ИЛИ по отношению к длительности импульса помехи на узле ИЛИ-НЕ происходит монотонно и при 30 MэВ·см²/мг составляет 1.6 раза, при 60 MэВ·см²/мг составляет 3.4 раза, а при = 90 МэВ·см²/мг достигает 6.5 раз (рис. 86).

Зависимости длительности импульсов помехи для элемента ЗИЛИ приведены на рис. 8в для точек входа трека 5n в область NMOП транзисторов группы ИЛИ-HE, а также для точек входа 2n и 7n в транзисторы инвертора элемента ЗИЛИ (рис. 4в). Длительности импульсов помехи на выходе ЗИЛИ при точке входа трека 5n практически повторяют длительности импульсов на узле ИЛИ-НЕ в начальном диапазоне LET = 10-40 МэВ·см<sup>2</sup>/мг с последним значением 420 пс. Эффективность укорочения длительности импульса помехи на выходе ЗИЛИ возрастает в диапазоне 50-90 МэВ·см<sup>2</sup>/мг относительно импульса помехи на узле ИЛИ-НЕ так, что длительность помехи для точки трека 5n снижается в 1.2-2 раза, для точки 2n - в 2-2.5 раза, для точки 7n - в 2.4–3 раза. При этом максимальная длительность помехи не превышает 350 пс для трека с точкой входа 5n, 250 пс для трека с точкой входа 2n и 170 пс для трека с точкой входа 7n.

#### VI. ЗАКЛЮЧЕНИЕ

Надежность микропроцессорных систем с цепями резервирования потоков данных зависит помехоустойчивости элементов многоканальных цепей. Совместный сбор заряда транзисторами, расположенными в одной области, окруженной мелкой траншейной изоляцией в КМОП элементах по объемной технологии, способствуют процессам

компенсации длительности помех в 1.5–7 раз. Длительности помех в КМОП мажоритарном элементе с учётом коррекции находятся в диапазоне 90–350 пс.

#### Поддержка

Работа выполнена в рамках Госзадания, проект № 0065-2019-0008 "Архитектурные и схемотехнические методы снижения энергопотребления и повышения сбоеустойчивости микропроцессоров и коммуникационных контроллеров высокопроизводительных ЭВМ".

#### Литература

- [1] Dodd P.E., Shaneyfelt M.R., Felix J.A., Shwank J.R. Production and Propagation of Single-Event Transients in High-Speed Digital Logic ICs // IEEE Transactions on Nuclear Science. 2004. V. 51. № 6. P. 3278–3284.

- [2] Dodd P.E., Massengill L.W. Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics // IEEE Transactions on Nuclear Science. 2003. V. 50. № 3. P. 583–602.

- [3] Ferlet-Cavrois V., Massengill L.W., Couker P. Single-Event Transients in Digital CMOS – A Review // IEEE Transactions on Nuclear Science. 2013. V. 60. № 3. P. 1767– 1790.

- [4] Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W. Layout Technique for Single-Event Transient Mitigation via Pulse Quenching // IEEE Transactions on Nuclear Science. 2011. V. 58. № 3. P. 885– 890.

- [5] Katunin Yu.V., Stenin V.Ya., Prozorova A.G. Simulation of Errors Impulses from Single Ionizing Particles in CMOS Triple Majority Gates // in Proc. of 31st International Conference on Microelectronics (MIEL). 2019, Serbia. P. 201–204.

- [6] Garg R., Khatri S.P. Analysis and Design of Resilient VLSI Circuits: Mitigating Soft Errors and Process Variations. New York: Springer, 2010. P. 194–205.

### Features of Single Event Transients in CMOS Combinational Logic Circuits Caused by Charge Collection from Tracks of Single Particles

Yu.V. Katunin<sup>1</sup>, V.Ya. Stenin<sup>1,2</sup>

<sup>1</sup>Scientific Research Institute of System Analysis of RAS, Moscow

<sup>2</sup>National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Moscow katunin@cs.niisi.ras.ru, vystenin@mephi.ru

Abstract — The results of mixed TCAD-SPICE simulation of single event transients in combinational CMOS AND and OR gates as parts of two majority gates are presented. One of majority gates is implemented on 2-input AND and OR gates, and the other is based on three 2-input AND gates and 3-input OR gate. Generation of charge carriers from the track of a particle in silicon and charge collection by transistors of logic AND and OR gates belonging to one of the logical branches of the majority gate were simulated using TCAD. Other branches of the majority gate were simulated using SPICE models. The layouts of the AND and OR gates in majority gates are optimized so that each element consists of two groups of transistors, one group is the group of NMOS transistors, the other is the group of PMOS transistors. In each group the transistors of the AND gate (OR gate) are surrounded by transistors of inverters on both sides. Each group is a combination of several transistors with a common diffusion region, surrounded by shallow trench isolation with a depth of 400 nm. This increases the efficiency of pulse quenching during charge collection by transistors of inverter for cases of different distances from the input track points to transistors of inverter. During the simulation the duration of noise pulses and the nature of its reduction due to the pulse quenching effect were estimated. Majority gates designed using 65-nm CMOS bulk technology were used for simulation. The simulation was performed for tracks passing along the normal to the chip surface with linear energy transfer by the particle to the track of 60 MeV·cm<sup>2</sup>/mg. For each group 8 track entry points were defined to get the most information about the pulse response of the circuit. When the charge from the particle track is collected by the locked transistors of the group belonging to the NAND (NOR) gate, they pass to the open state (in particular, to the inverse bias). It forms a noise pulse at the NAND (NOR) output node, which locks the transistor of the output inverter, located in the AND (OR) gate. The locked transistor of the inverter, collecting charge from the same particle track, compensates for part of the duration of the noise pulse during its propagation to the output of the AND (OR) gate. Duplication the inverter with the location of the main and additional transistors of the inverter on both borders of the groups of NAND (NOR) transistors helps to reduce the duration of noise pulse when charge is collected from the track of an ionizing particle.

Significant shortening of noise pulses occurs starting from the LET values of 30 MeV·cm²/mg and its efficiency increases with LET increasing. Taking into account the shortening, the duration of noise pulses occurring in the majority gate is in the range of 90-350 ps. Thus, the joint charge collection by transistors located in the same diffusion area (group), surrounded by shallow trench isolation in CMOS 65-nm bulk elements, contributes to reduce the duration of noise pulses by 1.5-7 times. The proposed layout optimization is applicable to CMOS majority gates that remain vulnerable elements of systems implemented triple modular redundancy.

Keywords — fault tolerance, combinational logic, ionizing particle, linear energy transfer, majority voter, noise pulse, simulation, particle track.

#### REFERENCES

- [1] Dodd P.E., Shaneyfelt M.R., Felix J.A., Shwank J.R. Production and Propagation of Single-Event Transients in High-Speed Digital Logic ICs // IEEE Transactions on Nuclear Science. 2004. V. 51. № 6. P. 3278–3284.

- [2] Dodd P.E., Massengill L.W. Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics // IEEE Transactions on Nuclear Science. 2003. V. 50. № 3. P. 583–602.

- [3] Ferlet-Cavrois V., Massengill L.W., Couker P. Single-Event Transients in Digital CMOS A Review // IEEE Transactions on Nuclear Science. 2013. V. 60. № 3. P. 1767–1790.

- [4] Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W. Layout Technique for Single-Event Transient Mitigation via Pulse Quenching // IEEE Transactions on Nuclear Science. 2011. V. 58. № 3. P. 885– 890

- [5] Katunin Yu.V., Stenin V.Ya., Prozorova A.G. Simulation of Errors Impulses from Single Ionizing Particles in CMOS Triple Majority Gates // in Proc. of 31st International Conference on Microelectronics (MIEL). 2019, Serbia. P. 201–204

- [6] Garg R., Khatri S.P. Analysis and Design of Resilient VLSI Circuits: Mitigating Soft Errors and Process Variations. New York: Springer, 2010. P. 194–205.