# Метод повышения быстродействия самосинхронного умножителя

Ю.В. Рождественский, Ю.А. Степченков, Ю.Г. Дьяченко, Н.В. Морозов, Д.Ю. Степченков, Д.Ю. Дьяченко

Институт проблем информатики Федерального исследовательского центра "Информатика и управление" Российской академии наук (ФИЦ ИУ РАН)

{YRogdest, YStepchenkov, YDiachenko, NMorozov, DStepchenkov}@ipiran.ru, diaden87@gmail.com

Аннотация — Быстродействие самосинхронных (СС) схем в значительной степени определяется их индикаторной подсхемой. Особенно остро эта проблема стоит в многоразрядных вычислительных СС-схемах, в том числе, в умножителе. Классическая индикация предполагает формирование общего индикаторного выхода для всей ССсхемы, участвующего в запрос-ответном взаимодействии СС-устройств или ступеней СС-конвейера. Многоразрядные СС-схемы, реализующие алгоритмы обработки данных с высокой степенью параллелизма, допускают использование групповой индикации выходов СС-схемы с формированием поразрядных сигналов управления фазами их входов. Статья описывает метод ускорения работы индикаторной подсхемы применительно к ССумножителю, реализующему модифицированный алгоритм Бута и использующему двухступенчатое "дерево" Уоллеса на сумматорах с избыточным (троичным) и парафазным СС-кодированием их входов и выходов. Поразрядное управление входами обеих ступеней конвейера "дерева" Уоллеса обеспечили повышение быстродействия СС-умножителя 54×54 на 40% за счет увеличения его аппаратных затрат на 2,3-2,5%.

Ключевые слова— самосинхронный умножитель, избыточное кодирование, троичный сумматор, "дерево" Уоллеса, конвейер, индикация.

## I. Введение

Самосинхронные (СС) схемы обладают рядом преимуществ по сравнению с синхронными аналогами [1]. Они характеризуются более широким диапазоном устойчивой работоспособности по напряжению питания и температуре, локализуют константные неисправности, работают с максимальной производительностью, соответствующей текущим условиям эксплуатации. Кроме того, они гораздо устойчивее к кратковременным логическим сбоям, генерируемым ядерными частицами, космическими лучами, электромагнитным импульсом и шумовыми наводками.

Основной недостаток СС-схем – аппаратная избыточность. Например, аппаратные затраты на реализацию комбинационной СС-схемы больше аппаратных затрат на реализацию синхронного аналога. Причинами этого являются избыточное кодирование информационных сигналов, как правило – парафазное со спейсером

(ПФС), и индикаторная подсхема [1], подтверждающая окончание переключения в текущую фазу работы СС-схемы всех ее элементов.

Наличие индикаторной подсхемы имеет еще один негативный эффект - снижение быстродействия ССсхемы из-за необходимости ожидания срабатывания индикаторной подсхемы, прежде чем разрешить ССсхеме начать переключение в противоположную фазу. Это снижение быстродействия усугубляется при увеличении разрядности СС-устройства, поскольку обычно индикаторная подсхема собирает все частичные индикаторные сигналы СС-схемы в один общий индикаторный выход, участвующий в запрос-ответном взаимодействии соседних функционально законченных частей СС-схемы. Чем больше разрядность СС-схемы, тем больше получается частичных индикаторных сигналов и логических каскадов индикаторной подсхемы. В результате длина критического пути индикаторной подсхемы увеличивается.

Однако в СС-схемах с высокой степенью параллелизма обработки данных возможно ускорение работы индикаторной подсхемы. В работе [2] были предложены методы групповой и поразрядной индикации, в которых используются сигналы поразрядного управления комбинационной СС-схемой вместо одного общего сигнала, формируемого общим индикаторным выходом многоразрядной СС-схемы. Чем выше степень параллельности вычислений в СС-схеме и меньше функциональная связность соседних разрядов, тем эффективнее применение указанных методов.

В данной статье рассматриваются особенности реализации методов групповой и поразрядной индикации в 54-разрядном СС-умножителе, излагаются результаты моделирования умножителя и даются оценки эффективности применения ускоренной индикации в СС-устройствах данного класса.

# II. Особенности реализации СС-умножителя

В качестве объекта исследования был выбран умножитель 54×54 из нечувствительного к задержкам блока умножения-сложения-вычитания с плавающей точкой [3], реализующий модифицированный алгоритм Бута.

За счет конвейерной организации вычислений в блоке умножения-сложения-вычитания предварительное кодирование второго операнда методом Бута было перенесено в менее нагруженную ступень конвейера, реализующую входное FIFO. Таким образом, входными данными для рассматриваемой части СС-умножителя служат первый операнд в ПФС коде и результат кодирования методом Бута второго операнда также в ПФС коде. Сам умножитель реализован "деревом" Уоллеса (ДУ) на сумматорах с избыточным троичным [3] или парафазным [4] СС-кодированием входов и выходов.

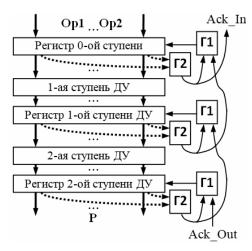

С целью повышения быстродействия умножителя и блока умножения-сложения-вычитания в целом ДУ было разбито на две ступени конвейера, как показано на рис. 1. Здесь Op1, Op2 — сомножители; Р - произведение; Ack\_In, Ack\_Out — входной и выходной сигналы уведомления об окончании текущей фазы работы. Такая организация взаимодействия ступеней конвейера обеспечивается реализацией выходного регистра ступени на гистерезисных триггерах (Г-триггерах, [1]), хранящих спейсер и рабочее состояние информационных сигналов.

Рис. 1. Конвейер ДУ с классической индикацией

Первая ступень троичного варианта ДУ включает формирователь троичных операндов и первый слой ДУ, а парафазного — три первых слоя ДУ. Формирователь троичных операндов реализует принцип преобразования разности двух ПФС операндов в один операнд с троичным СС-кодированием [5]. Сумматоры троичного ДУ имеют троичные входы и выход [3], реализуя сжатие числа слагаемых 2:1 на каждом слое. Сумматоры парафазного ДУ обеспечивают коэффициент сжатия 3:2. Вторая ступень троичного ДУ образована оставшимися тремя слоями ДУ, а парафазного ДУ — четырьмя слоями ДУ.

Элементы, обозначенные на рис. 1 символами "Г1", отображают подсхемы, например, Г-триггеры, формирующие сигналы управления фазой выходных регистров ступеней. Элементы "Г2" представляют индикаторные подсхемы, объединяющие поразрядные индикаторы в один общий индикаторный выход. Штриховыми линиями показаны поразрядные индикаторные сигналы, сплошными линиями — общие индикаторные сигналы многоразрядных частей ДУ.

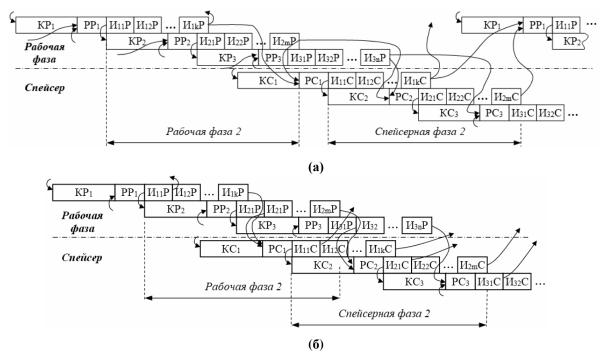

При классической индикации переключение выходного регистра ступени из рабочей фазы (спейсера) в спейсер (рабочую фазу) возможно только в том случае, если все разряды данного регистра и регистра следующей ступени конвейера переключились в рабочую фазу (спейсер). Рис. 2(а) демонстрирует в схематичном виде смену фаз работы трех последовательных ступеней ССконвейера с классической индикацией. Здесь: КРі, КСі – рабочая и спейсерная фазы комбинационной части іой ступени; РРі, РСі – рабочая и спейсерная фазы регистра і-ой ступени; ИіјР, ИіјС – рабочая и спейсерная фазы ј-го каскада индикаторной подсхемы і-ой ступени. Стрелками показаны зависимости между окончанием текущей фазы одной части схемы и началом соответствующей фазы другой части схемы.

Число каскадов индикаторной подсхемы зависит от разрядности комбинационной части ступени и выходного регистра. При использовании трехвходовых Гтриггеров оно оценивается величиной " $log_3M$ [", где М – разрядность индицируемой схемы; "][" – целое число, большее или равное значению внутри скобок.

Переключение регистра i-ой ступени в рабочую или спейсерную фазу разрешает комбинационной части (i+1)-ой ступени начать переключение в ту же фазу работы. Выходы комбинационной части ступени участвуют в регулировании фазовых переходов регистра этой же ступени. В результате, как видно из рис. 2(a), переключение второй ступени в рабочую фазу заканчивается раньше, чем появляется разрешение на ее переключение в спейсер, и наоборот.

В то же время переключение разрядов регистра і-ой ступени конвейера в текущую фазу означает фиксацию в нем значений выходов комбинационной части і-ой ступени. Поэтому в ряде случаев нет необходимости дожидаться подтверждения окончания переключения всех разрядов регистра в текущую фазу, чтобы разрешить регистру предыдущей ступени конвейера переключаться в противоположную фазу работы. Можно ограничиться подтверждением переключения только группы из нескольких разрядов регистра, чтобы разрешить переключение в противоположную фазу отдельным разрядам регистра предыдущей ступени.

Рис. 2. Последовательность переключений ступеней СС-конвейера с классической (a) и групповой (б) индикацией

Тогда индикатор первого каскада индикаторной подсхемы (i+1)-ой ступени формирует сигнал разрешения переключения в противоположную фазу для регистра i-ой ступени конвейера, как показано на рис. 2(б). В результате на фоне продолжающегося переключения индикаторной подсхемы i-ой ступени в рабочую фазу ее комбинационная часть уже может начать переход в спейсер под влиянием нового рабочего состояния на выходах регистра (i-1)-ой ступени. Это создает предпосылки для "перекрытия" интервалов переключения i-ой ступени в рабочую и спейсерную фазы и ускорения конвейера в целом. Чем больше разрядность ступени, тем больше каскадов ее индикаторной подсхемы и больше выигрыш в быстродействии.

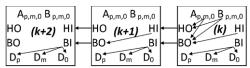

Рис. 3. Взаимосвязь сумматоров слоя троичного ДУ

Возможность использования групповой индикации с поразрядным управлением в ДУ на троичных сумматорах базируется на взаимосвязи входов и выходов сумматоров в соседних разрядах одного слоя ДУ. Эта взаимосвязь определяется схемой одноразрядного сумматора. Для троичных сумматоров [3] она иллюстрируется на рис. 3. Здесь k-ый разряд троичного ДУ суммирует два троичных входных сигнала  $\{A_{p,m,0}, B_{p,m,0}\}$  и входные парафазные переносы НІ и ВІ, пришедшие из (k-1)-го разряда, и формирует выходы троичной суммы  $\{D_p, D_m, D_0\}$  и парафазного переноса  $\{HO, BO\}$ . Выходы  $\{D_p, D_m, D_0\}$  поступают на вход k-го разряда следующего

каскада ДУ, а выходы НО и ВО — на вход (k+1)-го разряда этого же слоя ДУ. Таким образом, входные операнды одного разряда слоя ДУ { $A_{p,m,0}$ ,  $B_{p,m,0}$ } влияют на три разряда этого слоя ДУ.

В результате при реализации ДУ на троичных сумматорах одной ступенью конвейера операнды k-го разряда первого слоя ДУ в наихудшем случае оказывают влияние на значения выходов девяти разрядов последнего (четвертого) слоя ДУ. Следовательно, сигнал управления фазой k-го разряда первого каскада ДУ, можно сформировать на основе индикации (k, k+1, ..., k+8) разрядов выходного регистра ДУ.

В парафазном ДУ используется одноразрядный сумматор с сохранением переноса. Выход переноса k-го разряда в i-ом слое ДУ попадает на вход (k+1)-го разряда (i+1)-го слоя ДУ. В итоге выходы сумматора k-го разряда в i-ом слое ДУ влияют на формирование выходов k-го и (k+1)-го разрядов в (i+1)-ом слое ДУ.

Назовем коэффициентом зависимости L число выходных разрядов СС-схемы, которые в наихудшем случае зависят от входов ее одного разряда. Он определяет сложность индикаторной подсхемы, формирующей сигнал управления для одного разряда данной СС-схемы. Тогда для одноступенчатого троичного ДУ  $L_T=9$ , а для парафазного ДУ  $-L_{\Pi\Phi}=7$ .

При двухступенчатой реализации троичного ДУ, показанной на рис. 1, первая ступень включает только один слой ДУ и коэффициент зависимости для нее  $L_{T1}$  = 3. Во второй ступени конвейера ДУ три слоя троичных сумматоров и для нее  $L_{T2}$  = 7. Для парафазного ДУ

с разбиением на три слоя в первой ступени и четыре слоя во второй ступени:  $L_{\Pi\Phi 1}=3$  и  $L_{\Pi\Phi 2}=4$ .

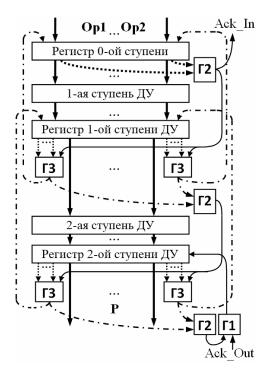

Схема конвейера с ускоренным запрос-ответным взаимодействием ступеней ДУ на основе групповой индикации и поразрядного управления показана на рис. 4. Здесь, помимо индикаторных подсхем "Г1" и "Г2", используются групповые индикаторные блоки "Г3". Число входов в "Г3" равно соответствующему коэффициенту зависимости плюс еще один для общего индикатора регистра, входами которого управляют выходы "Г3", для обеспечения строгой самосинхронной работы. Поскольку регистр первой ступени содержит семь частичных произведений, каждый групповой индикатор регистра второй ступени ДУ управляет его семью разрядами.

Рис. 4. Конвейер ДУ с групповой индикацией и поразрядным управлением

Индикаторные выходы комбинационных частей ступеней конвейера необходимо учитывать при формировании сигналов управления регистром, формирующим их входы. Делать это целесообразно интегрированием их поразрядных индикаторных выходов в поразрядные индикаторы регистра ступени.

# III. Сравнение вариантов ДУ

Моделирование вариантов двухступенчатого конвейера ДУ, представленных на рис. 1 и 4, в базисе библиотеки элементов для промышленной 65-нм объемной КМОП-технологии подтверждает явное преимущество групповой индикации и поразрядного управления в сравнении с классической организацией запрос-ответного взаимодействия ступеней СС-конвейера.

# А. Троичное ДУ

Вариант троичного ДУ с классической индикацией (рис. 1) показывает среднюю длительность рабочего цикла на уровне 1070 пс в типовых условиях (напряжение питания 1В, температура 25°С, типовые модели КМОП-транзисторов). Вариант с поразрядным управлением (рис. 4) демонстрирует среднюю длительность рабочего цикла на уровне 770 пс в тех же условиях.

Таким образом, использование групповой индикации и поразрядного управления ускоряет работу конвейера троичного ДУ почти на 40%. Платой за повышение быстродействие является увеличение аппаратных затрат на реализацию индикаторной подсхемы и увеличение числа сигналов запрос-ответного взаимодействия, что приводит к росту площади топологической реализации схемы и энергопотребления ДУ.

При использовании трехвходовых Г-тригтеров для реализации индикаторной подсхемы СС-схемы с М индикаторными выходами и одним выходом сложность индикаторной подсхемы в КМОП-транзисторах в первом приближении оценивается по формуле:

$$A_{\rm H} = 16 \cdot \left[ \frac{M}{2} \left( 1 - \frac{1}{\log_3 M} \right) \right]. \tag{1}$$

Сложность индикаторной подсхемы с N выходами в первом приближении оценивается по формуле:

$$A_{\text{HM}} = 16 \cdot \left[ \frac{M}{2} \left( 1 - \frac{1}{\log_2 M} \right) - \frac{N}{2} \left( 1 - \frac{1}{\log_2 N} \right) \right]. \tag{2}$$

Регистр первой ступени конвейера троичного ДУ имеет  $M_1=420$  разрядов. Следовательно, сложность реализации классической подсхемы его индикации в соответствии с формулой (1) равна  $A_{\rm UK1}\approx 2750$  КМОПтранзисторов. В регистре второй ступени конвейера ДУ  $M_2=106$  разрядов. Сложность реализации классической подсхемы его индикации равна  $A_{\rm UK2}\approx 650$  КМОПтранзисторов.

Использование групповой индикации (трехразрядной в первой ступени конвейера троичного ДУ) для организации поразрядного управления с учетом общих сигналов управления, участвующих в формировании каждого поразрядного сигнала управления, увеличивает эффективное число объединяемых индикаторных сигналов до величин:

$$M_{1\Gamma} = 3 \cdot (M_1 - 2) + 420 = 1134,$$

$M_{2\Gamma} = 7 \cdot (M_2 - 6) + 106 = 806.$

Тогда сложность индикаторных подсхем поразрядного управления первой и второй ступеней троичного ДУ, показанного на рис. 4, будет равна  $A_{\text{ИГ1}} \approx 7650$  и  $A_{\text{ИГ2}} \approx 5400$  КМОП-транзисторов соответственно. Суммарное увеличение сложности индикаторной подсхемы ДУ на троичных сумматорах равно примерно 9650 КМОП-транзисторам.

Реализацию индикаторной подсхемы второй ступени можно оптимизировать. Индикация семи разрядов требует использования двух каскадов двух- и трехвходовых Г-триггеров. На рис. 5 изображен фрагмент

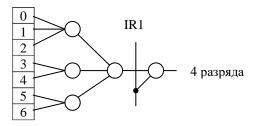

"дерева" Г-триггеров, формирующего сигнал управления четырьмя разрядами регистра первой ступени ДУ. Каждый кружок на нем эквивалентен одному Г-триггеру. Слева показаны разряды регистра второй ступени ДУ. Сигнал IR1 — общий индикатор регистра первой ступени ДУ.

Рис. 5. Схема простого поразрядного управления

Для формирования сигналов управления всеми разрядами регистра первой ступени необходимы сто схем рис. 5, "сканирующих" семерки разрядов регистра второй ступени. К тому же выходы этих "сканеров" должны быть объединены в один индикаторный сигнал для обеспечения самосинхронности запрос-ответного взаимодействия ступеней конвейера ДУ.

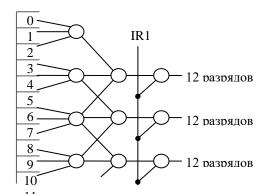

Однако нет необходимости индицировать каждую семерку разрядов независимой схемой из Г-тригтеров. На рис. 6 показана оптимизированная схема реализации группового управления. Четверки трехвходовых Г-тригтеров индицируют девятки разрядов регистра второй ступени ДУ и формируют сигнал, управляющий двенадцатью разрядами регистра первой ступени троичного ДУ.

Рис. 6. Схема группового троичного управления

При таком подходе кардинально сокращается число Г-триггеров в индикаторной подсхеме регистра второй ступени ДУ (с учетом сборки общего индикатора регистра – с 660 до 123) и уменьшаются аппаратные затраты на ее реализацию (с 5400 до 1700 КМОП-транзисторов). Тогда суммарное увеличение сложности индикаторной подсхемы ДУ на троичных сумматорах и умножителя в целом будет равно примерно 5950 КМОП-транзисторам.

Сложность умножителя, реализующего модифицированный алгоритм Бута, с троичным ДУ составляет примерно 260 тысяч КМОП-транзисторов. Таким образом, суммарные дополнительные аппаратные затраты на индикаторную подсхему, обеспечивающие поразрядное управление, составляют менее 2,3% от общей сложности умножителя, обеспечивая при этом повышение быстродействия почти на 40%.

# В. Парафазное ДУ

Моделирование вариантов парафазного ДУ с классической и групповой индикацией также свидетельствует о повышении на 37% быстродействия варианта с поразрядным управлением (средняя длительность рабочего цикла 710 пс) в сравнении с быстродействием классического варианта (970 пс).

Улучшение быстродействия парафазного ДУ достигается также за счет увеличения аппаратных затрат на реализацию его индикаторной подсхемы. Аналогично варианту троичного ДУ, регистр первой ступени парафазного ДУ хранит четыре частичных произведения в избыточном коде: каждый разряд регистра хранит парафазные сумму и перенос. Использование их в качестве входов элементов "исключающее ИЛИ" во второй ступени конвейера ДУ и их единичный спейсер позволяют индицировать оба парафазных выхода разряда регистра одним элементом 4И-НЕ, сокращая тем самым общее число индикаторных сигналов.

Сигналы поразрядного управления задатчиком входов первой ступени ДУ формируются на основе индикации трех соседних разрядов, как и в случае троичного ДУ. Но, в отличие от троичного ДУ, число частичных произведений, записываемых в регистр первой ступени ДУ, равно четырем, и регистр первой ступени ДУ имеет 240 разрядов. Аппаратные затраты на реализацию индикаторной подсхемы регистра первой ступени ДУ: 1530 КМОП-транзисторов для классического управления и 6400 для поразрядного.

Регистр второй ступени парафазного ДУ содержит 106 разрядов, как и троичный вариант. Но каждый из них также содержит парафазные сумму и перенос, которые уже не могут быть проиндицированы одним элементом 4И-НЕ. Поэтому суммарное число индикаторных выходов регистра равно 212. Общий индикаторных выход регистра второй ступени парафазного ДУ в классическом варианте управления конвейером ДУ формируется пятикаскадной схемой на Г-триггерах, имеющей сложность 1700 транзисторов.

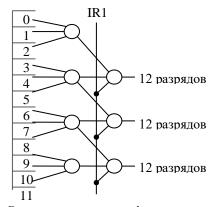

Рис. 7. Схема группового парафазного управления

Для управления одним разрядом четырех частичных произведений в регистре первой ступени ДУ требуется проиндицировать лишь четыре разряда регистра второй ступени. Схема групповой индикации регистра второй ступени парафазного ДУ, оптимизированная по быстродействию, показана на рис. 7. Парные индикаторные выходы разрядов регистра объединяются с индикаторами комбинационной части второй ступени, формируя один индикаторный выход в каждом разряде регистра.

Схема на рис. 7 формирует 34 сигнала группового управления регистром первой ступени ДУ, как и схема на рис. 6. Но ее суммарные аппаратные затраты меньше на 400 КМОП-транзисторов. Тогда суммарное увеличение сложности индикаторной подсхемы ДУ на парафазных сумматорах и умножителя в целом будет равно примерно 5500 КМОП-транзисторам.

Сложность умножителя, реализующего модифицированный алгоритм Бута, с парафазным ДУ составляет примерно 220 тысяч КМОП-транзисторов [4]. Таким образом, суммарные дополнительные аппаратные затраты на индикаторную подсхему, обеспечивающие поразрядное управление, составляют около 2,5% от общей сложности умножителя, обеспечивая при этом повышение быстродействия на 37%.

#### IV. ЗАКЛЮЧЕНИЕ

Метод ускорения конвейера умножителя, представленный в данной статье, основывается на том, что схема управления запрос-ответным взаимодействием ступеней конвейера обеспечивает распараллеливание обработки данных ступенью конвейера и формирования ее общего индикатора. Для этого используется свойство независимости спейсерного состояния от предыдущего рабочего состояния.

Предложенный метод групповой индикации ССумножителя обеспечивает строгую самосинхронность двухступенчатой реализации ДУ и повышение ее быстродействия примерно на 40% в сравнении с классической индикацией как для троичного, так и для парафазного ДУ.

Платой за достигнутый рост быстродействия является увеличение аппаратных затрат на величину не более 2,5% за счет усложнения индикаторной подсхемы и рост числа сигналов запрос-ответного взаимодействия между ступенями конвейера умножителя. Следствием этого является соответствующий незначительный рост энергопотребления.

Моделирование проводилось без учета паразитных параметров, привносимых топологической реализацией

умножителя. Однако столь незначительное усложнение схемы ДУ нивелирует возможную разницу в паразитных параметрах рассмотренных вариантов ДУ и неспособно существенно изменить полученные оценки быстродействия.

Выигрыш в быстродействии вариантов с групповой индикацией и с поразрядным управлением достигается за счет ускорения формирования поразрядных сигналов управления по отношению к общему сигналу управления. Он определяется большой задержкой формирования общего индикатора многоразрядного СС-регистра. С увеличением числа разрядов сомножителей преимущество реализаций СС-схем с поразрядным управлением увеличивается.

Наша дальнейшая работа будет посвящена исследованию эффективности поразрядного управления СС-схемы произвольного класса в зависимости от ее разрядности.

#### Поддержка

Исследование выполнено при финансовой поддержке по Программам фундаментальных исследований Президиума РАН (проект 2019-0054-2.2) в Институте проблем информатики ФИЦ ИУ РАН.

## ЛИТЕРАТУРА

- [1] Варшавский В.И. и др. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах. М.: Наука, 1986. 400 с.

- [2] Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю., Дьяченко Д.Ю. Оптимизация индикации многоразрядных самосинхронных схем / Системы и средства информатики, №4, 2019. С. 14-27.

- [3] Соколов И.А., Рождественский Ю.В., Дьяченко Ю.Г., Степченков Ю.А., Морозов Н.В., Степченков Д.Ю., Дьяченко Д.Ю. Нечувствительный к задержкам блок умножения-сложения-вычитания с плавающей точкой // Проблемы разработки перспективных микро- и наноэлектронных систем 2018. Сб. трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2018. Вып. 2. С. 170-177 (rus). ISSN 2078-7707. DOI 10.31114/2078-7707-2018-2-170-177.

- [4] Y. A. Stepchenkov, Y. G. Diachenko, Y. V. Rogdestvenski, D. Y. Diachenko, Y. I. Shikunov, Self-Timed Multiply-addsubtract Unit Alternates, 2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), 27-30 Jan. 2020, pp.1864-1868. DOI: 10.1109/EIConRus49466.2020.9039039.

- [5] Makino H., Nakase Y., Suzuki H., Morinaka H., Shinohara H., and Mashiko K. 1996. An 8.8 ns 54x54 bit Multiplier with High Speed Redundant Binary Architecture. IEEE Journal of Solid-State Circuits. 31(6): 773-783.

# Self-Timed Multiplier Performance Improvement Technique

Y.V. Rogdestvenski, Y.A. Stepchenkov, Y.G. Diachenko, N.V. Morozov, D.Y. Stepchenkov, D.Y. Diachenko

Institute of Informatics Problems, Federal Research Center "Computer Science and Control" of the Russian Academy of Sciences (IPI FRC CSC RAS), IPI RAS

{YRogdest, YStepchenkov, YDiachenko, NMorozov, DStepchenkov}@ipiran.ru, diaden87@gmail.com

Abstract — Self-timed (ST) circuit's indication subcircuit largely determines its performance. This problem is especially acute in multi-bit computing ST circuits, including multiplier. The classical indication involves generating an entire ST circuit total indication output, which takes part in handshaking ST units or ST pipeline stages. Multi-bit ST circuits that implement data processing algorithms with a high parallelism degree allow the use of group indication of the ST circuit outputs resulting in bitwise signals controlling their inputs' phase. The article describes a method of accelerating the indication subcircuit operation as applied to the ST-multiplier, which implements the modified Booth algorithm and uses the two-stage Wallace tree on adders with redundant (ternary) and dual-rail ST-coding of their inputs and outputs. Group indication and bitwise input control of both Wallace tree pipeline stages provide an increase of ST-multiplier performance by 40% with a penalty of 2.3-2.5% in its hardware.

Keywords — self-timed multiplier, redundant coding, ternary adder, Wallace tree, pipeline, indication.

#### REFERENCES

[1] Varshvskij V.I. i dr. Avtomatnoe upravlenie asinhronnyimi protsessami v EVM i diskretnyih sistemah (Automatic

- control of the asynchronic processes in the computers and discrete systems). M.: Nauka, 1986. 400 p.

- [2] Yu.A. Stepchenkov, DiachenkoYu.G., YuV. Rozhdestvenskij, N.V. Morozov, D.Yu. Stepchenkov, D.Y. Diachenko, Optimizaciya indikacii mnogorazryadnyh samosinhronnyh skhem (Indication optimization in multi-bit self-timed circuits) / Sistemy i sredstva informatiki, No.4, 2019. P. 14-27.

- [3] I.A. Sokolov, Y.V. Rogdestvenski, Y.G. Diachenko, Y.A. Stepchenkov, N.V. Morozov, D.Y. Stepchenkov, D.Y. Diachenko. Delay-Insensitive Floating Point Multiply-Add-Subtract Unit / Problems of Advanced Micro- and Nanoelektronic Systems Development 2019, Issue III, Moscow, IPPM RAS, P. 20-25. DOI: 10.31114/2078-7707-2019-3-20-25.

- [4] Y. A. Stepchenkov, Y. G. Diachenko, Y. V. Rogdestvenski, D. Y. Diachenko, Y. I. Shikunov, Self-Timed Multiply-addsubtract Unit Alternates, 2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), 27-30 Jan. 2020, pp.1864-1868. DOI: 10.1109/EIConRus49466.2020.9039039.

- [5] H. Makino, Y. Nakase, H. Suzuki, H. Morinaka, H. Shinohara, and K. Mashiko, "An 8.8-ns 54x54-bit multiplier with high speed redundant binary architecture" // IEEE Journal of Solid-State Circuits.1996. V. 31. No. 6, pp. 773-783.