# rEDActor – A PDK Cross-platform Integrated Development Environment for Semiconductor Technologies

**Datsuk Anton**

MES2020, Russia

innovations for high performance

microelectronics

## **Motivation**

|                                               | rEDActor | Nedit | Sublime Text | SKILL IDE |

|-----------------------------------------------|----------|-------|--------------|-----------|

| Integration with EDA software (Virtuoso, ADS) |          | ×     | ×            | <b>*</b>  |

| Code auto-formating                           |          | ×     | ×            | ×         |

| Code folding                                  |          | ×     |              |           |

| Keyword auto-completion                       |          | ×     |              |           |

| Embedded syntax checker                       |          | ×     | ×            |           |

| Auto initialization of global variables       |          | ×     | ×            | ×         |

| Code Debugging                                | <b>*</b> | ×     | ×            | <b>~</b>  |

| SKILL to AEL code conversion                  |          | ×     | ×            | ×         |

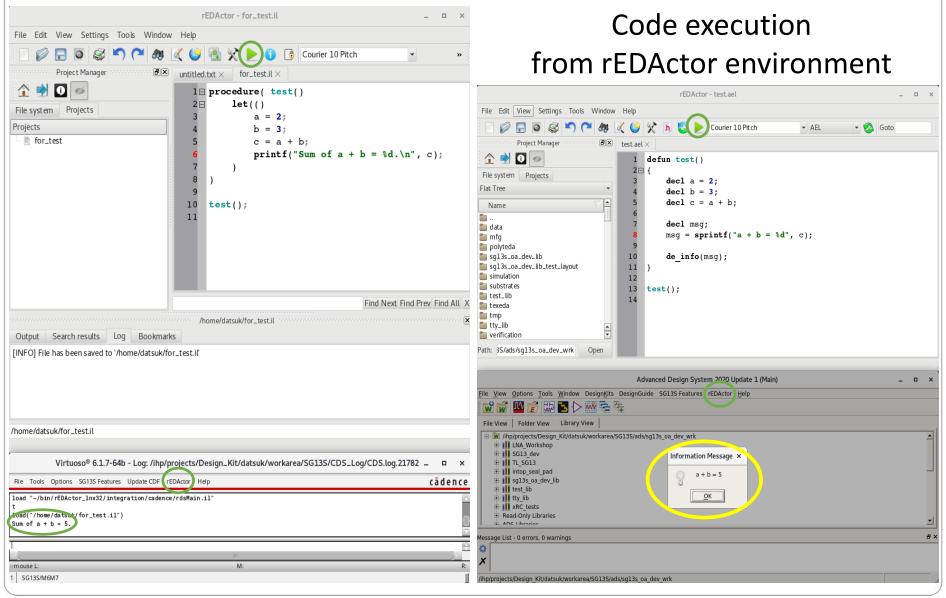

## Integration with leading edge EDA vendors

## **Code autoformating**

## **Code folding**

- IDE rEDActor allows the user to selectively hide and display (fold) sections of a currently edited file.

- This simplifies managing large amounts of text while viewing only those subsections of the text that are specifically relevant at any given time.

```

rEDActor - texedaAvs.ael

File Edit View Settings Tools Window Help

Courier New

~ AEL

texedaAvs.ael ×

defun texedaSaveLvsLibCellView(lvsLibName, lvsCellName, lvsViewN

35⊞ {

42

43

defun texedaGetColor (map, color)

48 □ {

49

decl i;

for(i = 0; i < listlen(map); ++i) {</pre>

50⊞

55

56

return(0);

```

## **Embedded syntax checkers**

```

- 2

calibrePEX.il

149 procedure(ihpArk comparePexQaVsGolden(runInfo, tool, errCount, rptFile, g lvsQaG

prog((data

151

cmpRes

152

diffFile

153

logPath

154

msq

155

goldenFile

156

summaryFile)

157

158⊟

if (g lvsQaGolden == nil then

159

return(errCount);

160

161

162

goldenFile = ihpArk getQrcQaGoldenFile(g lvsQaGolden, tool);

if(goldenFile == nil | | isFile(goldenFile) == nil then

163⊟

sprintf(msq, "[WARNING] No golden file exist to wave errors.\n");

164

165

ihpArk writeLog(msg, rptFile);

166

return(errCount);

167

Output Search results Log Bookmarks

HINT (EQUALT): /IIIp/projects/Design_Kit/teamcity/teamcity2018.2.3/bulldagent/work/a3b34c5c59d52030/QA/Arkona/skili/tests/calibre

HINT (EQUAL1): /ihp/projects/Design_Kit/teamcity/TeamCity2018.2.3/buildAgent/work/a3b54c5c59d52030/QA/Arkona/skill/tests/calibre

INFO (VAR5): Unrecognized global variables:

WARN GLOB (VAR8): ihpArkGlob_installPath

INFO (VAR): used: in function ihpArk_getPexQaGoldenFile from file /ihp/projects/Design_Kit/teamcity/TeamCity2018.2.3/buildAgent/wor

WARN GLOB (VAR8): tmpInfo

INFO (VAR): used: in function ihpArk_calibrePEX from file /ihp/projects/Design_Kit/teamcity/TeamCity2018.2.3/buildAgent/work/a3b54c

INFO (VAR): used: in function ihpArk_runCalibrePexExt from file /ihp/projects/Design_Kit/teamcity/TeamCity2018.2.3/buildAgent/work/a

INFO (IO): IQ score is 63 (best is 100).

INFO (IQ1): IQ score is based on 1 error messages, 6 general warning messages, and 10 top level forms.

INFO (REP110): Total enhancement : 0.

INFO (REP110): Total external global: 0.

INFO (REP110): Total package global: 0.

INFO (REP110): Total warning global: 2.

INFO (REP110): Total error global : 0.

INFO (REP110): Total unused vars : 2.

INFO (REP110): Total next release : 0.

INFO (REP110): Total alert

INFO (REP110): Total hint

INFO (REP110): Total suggestion : 9.

INFO (REP110): Total internal alert : 0.

INFO (REP110): Total information : 28

INFO (REP110): Total warning

INFO (REP110): Total error

INFO (REP110): Total internal error: 0.

INFO (REP110): Total fatal error : 0.

INFO (REP009): Program SKILL Lint finished on Feb 19 15:07:37 2020 with status FAIL

```

rEDActor supports syntax checkers for:

- SKILL (Cadence)

- AEL (Keysight)

- SVRF (Mentor)

- LAYTOOLS (TexEDA)

- XML.

On clicking on the line number when the error was found rEDActor automatically navigates to this line.

October2020

/ihp/projects/Design Kit/teamcity/TeamCity2018.2.3/buildAgent/work/a3b54c5c59d52030/QA/Arkona/skill/tests/calibrePEX.il

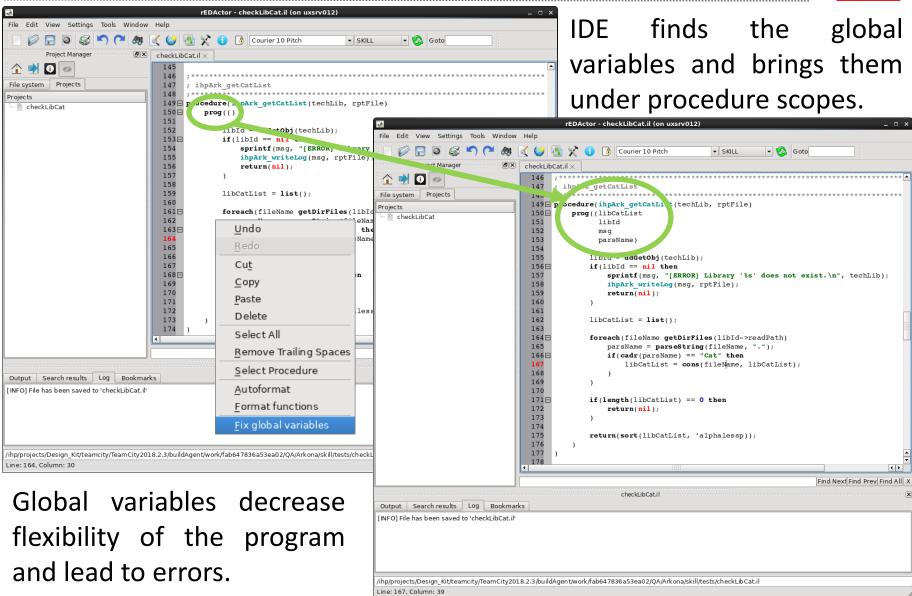

## Auto initialization of global variables

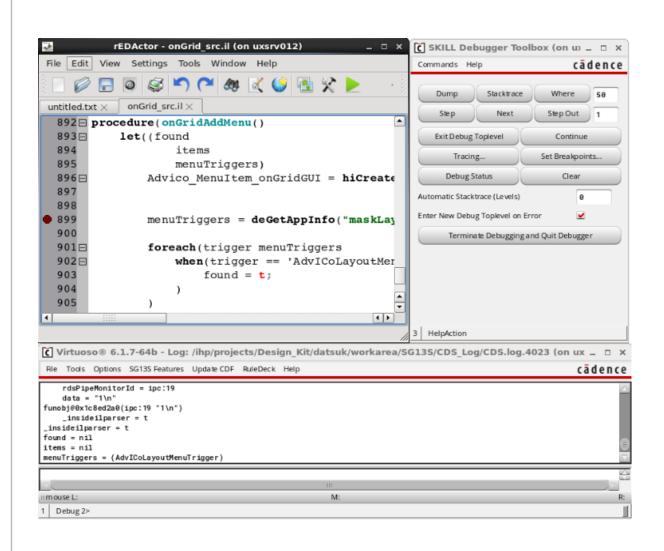

### Code debugging

If required a developer can set up break points and perform SKILL code debugging.

The debugger allows to output information for:

- Global and local variables

- Functions stack calls

#### SKILL to AEL code conversion

#### **SKILL**

#### **AEL**

```

when( metallization=="M4" || metallization=="M4M5"

bmlayer="Metal3")

; check minvalues

when(w < wmin-epsilon</pre>

w=wmin;

hiGetAttention()

printf("Width < %L\n" wmin)</pre>

when(l < lmin-epsilon</pre>

l=lmin;

hiGetAttention()

printf("Height < %L\n" lmin)</pre>

; how many vias?

xanz=fix((w-cont over-cont over+cont dist)/(cont size+cont dist)+epsilon)

; width for vias

wl=xanz*(cont size+cont dist)-cont dist+cont over+cont over

; offset to first via

xoffset=(w-w1)/2

xoffset=GridFix(xoffset)

yanz=fix((l-cont_over-cont_over+cont_dist)/(cont_size+cont_dist)+epsilon)

l1=yanz*(cont size+cont dist)-cont dist+cont over+cont over

yoffset=(l-l1)/2

yoffset=GridFix(yoffset)

ycont cnt=cont over+yoffset

; draw vias

while(ycont cnt+cont size+cont over <= l+epsilon</pre>

xcont cnt=cont over+xoffset

while (xcont cnt+cont size+cont over <= w+epsilon

dbCreateRect(pcCellView vialayer list(

list(xcont cnt ycont cnt)

list(xcont cnt+cont size ycont cnt+cont size))

xcont_cnt=xcont_cnt+cont_size+cont_dist

ycont cnt=ycont cnt+cont size+cont dist

```

```

if(metallization == "M4" || metallization == "M4M5") {

bmlaver = "Metal3";

if(w < wmin-epsilon) {</pre>

w = wmin;

hiGetAttention();

de info(sprintf("Width < %L\n", wmin));</pre>

if(1 < lmin-epsilon) {</pre>

l = lmin;

hiGetAttention();

de info(sprintf("Height < %L\n", lmin));</pre>

xanz = fix((w-cont_over-cont_over+cont_dist)/(cont_size+cont_dist)+epsilon);

w1 = xanz*(cont size+cont dist)-cont dist+cont over+cont over;

xoffset = (w-w1)/2;

xoffset = GridFix(xoffset);

yanz = fix((l-cont over-cont over+cont dist)/(cont size+cont dist)+epsilon);

11 = yanz*(cont size+cont dist)-cont dist+cont over+cont over;

yoffset = (1-11)/2;

yoffset = GridFix(yoffset);

ycont_cnt = cont_over+yoffset;

while(ycont cnt+cont size+cont over<= l+epsilon) {</pre>

xcont cnt = cont over+xoffset;

while(xcont cnt+cont size+cont over<= w+epsilon) {</pre>

dbCreateRect(pcCellView, vialayer,

list(xcont cnt, ycont cnt,

xcont cnt+cont size, ycont cnt+cont size));

xcont cnt = xcont cnt+cont size+cont dist;

ycont cnt = ycont cnt+cont size+cont dist;

```

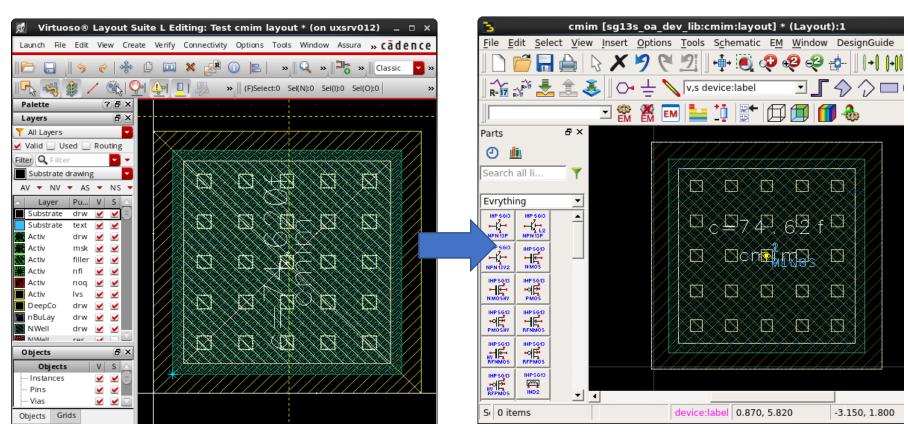

#### SKILL to AEL code conversion

SKILL

AEL

The converted AEL code for CMIM Pcell has been loaded into Keysight ADS environment without any additional modifications.

#### **SKILL to AEL code conversion**

The conversion works based on plug-ins.

For this the basic SKILL procedures (for ex. dbCreateRect, dbCreatePolygon, etc.), have been developed using Keysight AEL language.

User can extend the plug-in file on demand.

```

▼ AEL

defun dbCreateRect(g cxt, g lpp, g bbox)

2 ⊟ {

decl layerId = db_get_layerid(g cxt, nth(0, g lpp),

nth(1, g lpp));

db_add_rectangle(g_cxt, layerId, nth(0, g bbox),

nth(1, g bbox),

nth(2, g bbox),

nth(3, g bbox));

9

10

11

defun dbCreatePolygon(cxt, layer, points)

12 □ {

13

db add polygon(cxt);

14

15 □

if(is_string(layer)) {

16

layer = db get layerid(cxt, layer, "drawing");

17

18⊟

elseif(is list(layer)) {

19

layer = db_get_layerid(cxt, nth(0, layer), nth(1, layer));

20

21

22

decl i;

23 ⊟

for(i = 0; i < listlen(points); ++i) {</pre>

24

decl x = nth(i, points);

25

++i:

26

decl y = nth(i, points);

27

28

db add point(cxt, x, y);

29

30

31

decl polygon = db_end(cxt, layer);

32

33

return(polygon);

34

```

#### **Current Users**

The following companies are using IDE rEDActor:

#### **Conclusions and results**

- 1. rEDActor has been incorporated into the leading-edge software tools increasing efficiency of PDK development.

- 2. The IDE provides a functionality to perform code autoformating, folding, debugging etc.

- 3. The editor allows to convert SKILL code to AEL thus increasing productivity of Cadence interoperable PDKs.

- 4. The IDE rEDActor has been successfully applied for development of PDKs for 0.13 um and 0.25 um SiGe BiCMOS technologies resulting in highly reliable and robust PDK releases.

## Thank you for attention!

IHP – Leibniz-Institut für innovative Mikroelektronik

Im Technologiepark 25 15236 Frankfurt (Oder)

Phone: +49 (0) 335 5625 647 Fax: +49 (0) 335 5625 327

E-Mail: datsuk@ihp-microelectronics.com

www.ihp-microelectronics.com

innovations for high performance

microelectronics