# Синтез устройств управления объектами напольной автоматизации железнодорожного транспорта на программируемых логических интегральных схемах

А.В. Пашуков

Российский университет транспорта (РУТ (МИИТ), г. Москва art\_pash@mail.ru

Аннотация — Рассмотрены возможности применения программируемых логических интегральных схем в различных отраслях промышленности. Кратко рассмотрены сферы применения устройств на основе программируемых логических схем. Описывается возможность применения программируемых логических интегральных схем в железнодорожной отрасли на примере создания схемы управления проходным светофором. Показано что известные подходы к проектированию систем управления на релейной или микропроцессорной базе напрямую можно применять и для проектирования систем на программируемых логических схемах. Приведены примеры повышения безопасности в виде использования модульных кодов с суммированием и N-версионного программирования.

Ключевые слова — программируемая логическая интегральная схема, схема управления светофором, диверсионное программирование, коды с суммированием.

#### I. Введение

Устройства программируемой логики заняли в современной области автоматизации в промышленности и на транспорте свою собственную нишу. С их помощью решаются как простейшие задачи, так и самые сложные. Программируемые логические интегральные схемы применяются в различных отраслях промышленности для совершенно разных целей.

Так, в качестве контроллеров и процессоров обработки данных ПЛИС применяются в космической отрасли. Специально для этой цели были созданы микросхемы, устойчивые к радиации [1].

Благодаря своей гибкости и высокой скорости обработки данных, ПЛИС активно используют в системах цифровой радиосвязи [2].

ПЛИС применяются и в атомной промышленности. Здесь они обеспечивают фильтрацию входных сигналов, выполнение логических функций, а также используются в системах аварийной защиты. [3,4]

ПЛИС также применяются и на железных дорогах. Так в [5] рассмотрены методы синтеза логических устройств ЭЦ на базе ПЛИС. В частности, описан пример проектирования электронного реле с задержкой на отключение. Для реализации задержки времени на от-

ключение используется схема счетчика, схема контроля и управления триггера.

В [6] описана архитектура безопасных устройств, применяемых на железнодорожных переездах Чехии, где для обеспечения безопасности предложено применять систему с тройной модульной избыточностью и дублированием в каждом модуле. Другие способы обеспечения безопасности описаны в [7].

Однако данными сферами не ограничивается применение ПЛИС. Они также применяются в авиации и других отраслях [8].

Одним из самых сложных в работе с устройствами программируемой логики является не только решение задачи синтеза безопасного устройства с заданным алгоритмом функционирования, но и обеспечение отказоустойчивости устройства, простоты процедур тестового и рабочего (функционального) диагностирования, верификации реализуемых алгоритмов и пр. Другими словами, задачи технической диагностики по уровню важности находятся на одном уровне с задачами обеспечения выполнения заданного алгоритма.

Эволюция устройств с программируемой логикой берет начало с момента изобретения первой микросхемы, реализующей простейшую булеву функцию (логического вентиля), в середине XX столетия. С развитием мира микроэлектроники появляются не только логические вентили, а последовательно микросхемы с интеграцией нескольких вентилей, затем программируемые логические матрицы, полузаказные и заказные логические интегральные схемы и т.д. Растет сложность устройств, уменьшаются их габариты, меняются технологии изготовления и увеличивается число реализуемых ими функций. От простейших устройств осуществляется переход к гораздо более сложным, более восприимчивым к изменениям в окружающей среде и, несмотря на технологии изготовления, допускающим возникновение отказов [9]

Несмотря на свои преимущества, ПЛИС не применяется широко на российских железных дорогах. Их применение можно увидеть в аппаратуре тональных рельсовых цепей и в качестве каких-либо объектных контроллеров. Основная цель статьи — показать возможность применения программируемых логических

схем (ПЛИС) в схемах управления объектами напольной автоматизации железнодорожного транспорта.

II. Объекты напольной автоматизации железнодорожного транспорта

Одной из важнейших задач устройств сигнализации, централизации и блокировки на железных дорогах (далее СЦБ) является обеспечение безопасности движения поездов. Причем разрешение на движение поезда может быть дано только тогда, когда выполнены все условия безопасности.

Устройства СЦБ не должны допускать [10]:

- несоответствие контроля фактическому положению стрелки;

- неплотное прилегание остряка к рамному рельсу (более 4 мм);

- перевод стрелок под подвижным составом;

- изменение маршрута во время движения по нему;

- прием или отправление поезда на занятый путь;

- отправление поездов навстречу друг другу и др.

К напольным устройствам СЦБ относятся:

- стрелочные переводы

- светофоры

- рельсовые цепи

Стрелочный перевод — это устройство, служащее для перевода подвижного состава с одного пути на другой. Для перевода стрелки из одного крайнего положения в другое при ЭЦ используются схемы управления стрелочным переводом. Схемы управления стрелками электрической централизации должны осуществлять:

- перевод стрелки в нужное положение;

- замыкание прижатого остряка стрелки с проверкой плотности его прилегания к рамному рельсу;

- контроль фактического положения стрелки;

- запирание стрелки в маршруте, во избежание изменения маршрута во время движения и перевода стрелок под подвижным составом;

- осуществление непрерывного контроля положения стрелки с фиксацией взреза стрелки.

Перевод стрелок по маршруту осуществляется автоматически с контролем правильности положения и проверки запертого состояния стрелок. Для индивидуального перевода стрелки используется стрелочный коммутатор или соответствующие кнопки.

При отсутствии маршрутного набора (как правило, на малых станциях) каждая стрелка переводится разлельно.

При централизованном управлении стрелками и сигналами схема состоит из трех цепей: управляющей, рабочей и контрольной.

Управляющая цепь осуществляет включения с пульта пусковых приборов электропривода с проверкой условий безопасности. Рабочая цепь осуществляет подключение двигателя электропривода к источнику питания для перевода стрелки из одного положения в другое. Контрольная цепь осуществляет постоянный контроль положений стрелки [10-12].

Железнодорожный светофор — устройство для видимой сигнализации на железных дорогах, подающее сигналы в любое время суток только светом огней.

Управление светофором на станции выполняется при поступлении команды на открытие или закрытие с учетом получения информации о его текущем состоянии. В связи с этим в схемах управления светофорами можно выделить три функциональные цепи: сигнальных реле, светофорных ламп, контрольных реле.

Работу сигнальных реле можно разделить на два этапа: образования его первоначальной цепи возбуждения и перехода на цепь удержания или самоблокировки. При этом в цепи сигнальных реле контролируется все необходимые зависимости для обеспечения безопасности движения, а именно:

- надлежащее положение всех стрелок в маршруте;

- свободное состояние стрелочных и бесстрелочных путевых участков, входящих в маршрут;

- действительное замыкание стрелок, входящих в маршрут;

- отсутствие ранее установленных враждебных маршрутов, а также встречного направления движения в маршрутах отправления;

- отсутствие режима искусственного размыкания стрелок в установленном маршруте. (Пренебрежение этой зависимостью позволяет искусственно разомкнуть стрелки при открытом светофоре и не исключает возможности вступления поезда на разобранный маршрут, если конец размыкания приходится на момент нахождения поезда в непосредственной близости от светофора);

- отсутствие пригласительного огня на входном светофоре для маршрутов приема и на выходном для маршрутов отправления. (Отсутствие такой зависимости позволяет одновременно зажечь лампы разрешающих и пригласительного огней);

- отсутствие на перегоне хозяйственного поезда

или подталкивающего локомотива, имеющих право возвратиться на станцию с любой точки перегона после окончания своей работы с использованием ключа-жезла.

Цепи управления огнями светофоров относятся к наиболее ответственным в релейных централизациях и должны удовлетворять следующим требованиям:

- переключение светофорных огней должно осуществляться контактами реле класса надежности, причем разрешающие огни включаются фронтовыми контактами;

- если светофор имеет два и более разрешающих огней, которые могут гореть одновременно, то цепи ламп более разрешающего огня включаются фронтовым контактом реле, а менее разрешающего тыловым (например, в цепях ламп зеленого и желтого огней);

- схема включения огней светофоров должна обеспечивать контроль фактического горения ламп;

- в схеме должно применяться двухполюсное отключение разрешающих огней от источника питания, чтобы исключить вероятность ложного горения от посторонних источников переменного или постоянного тока вследствие сообщений между кабельными жилами. [10-12]

Рельсовые цепи (РЦ) в устройствах СЦБ являются основным элементом железнодорожной автоматики и телемеханики. Рельсовая цепь представляет собой электрическую цепь, в которой имеется источник питания и нагрузка (путевое реле), а проводниками электрического тока являются рельсовые нити железнодорожного пути.

При работе РЦ должны соответствовать следующим требованиям:

- при отсутствии подвижного состава на рельсовой цепи путевой приемник должен надежно фиксировать ее свободность;

- при шунтировании в любой точке рельсовой линии хотя бы одной колесной парой, а также при полном изломе рельса должно фиксироваться занятое состояние;

- в кодовых и кодированных рельсовых цепях с вступлением поезда на входной конец под приемными катушками должен обеспечиваться нормативный ток АЛС, необходимый для действия приемных локомотивных устройств [10-13].

Для реализации схем управления напольным оборудованием систем СЦБ на ПЛИС требуется логическое описание алгоритмов работы того или иного объекта.

#### III. АНАЛОГ СХЕМЫ УПРАВЛЕНИЯ ПРОХОДНЫМ СВЕТОФОРОМ

Программируемые логические интегральные схемы (ПЛИС или FPGA) — это электронный компонент (интегральная микросхема), используемый для создания конфигурируемых цифровых электронных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования [14].

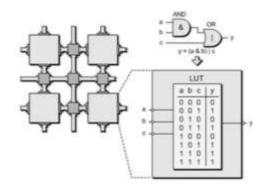

В простом варианте FPGA состоят из множества однотипных блоков (рис. 1), состояние которых отражается в таблицах LUT (Lookup Table). LUT размещается в небольшом программируемом фрагменте памяти, куда записывается логическая функция блока. Наиболее часто встречаются элементы LUT, позволяющие реализовывать с помощью одного блока одну функцию четырех переменных. Однако также встречаются LUT, которые имеют 5, 6, 7 или даже 8 выходов.

Применение ПЛИС обусловлено рядом преимуществ, среди которых можно выделить высокую производительность, быструю разработку проектов, простоту отладки и возможность параллельной работы по нескольким задачам.

На сегодняшний день ПЛИС выпускаются многими компаниями по всему миру. Среди таких компаний выделяются Actel, Altera, Atmel, Xilinx.

Основными способами повышения надежности устройств, реализованных на ПЛИС, являются схемотехнические способы. К ним относятся пространственное разнесение, дублирование и временная фильтрация сигналов. Также наряду со схемотехническими способами для повышения надежности применяются устойчивые к внешним помехам элементы [15,16].

Следует обратить внимание и на то, что надежность и безопасность находятся в некоторой зависимости: безопасность является частным свойством надёжности, которая напрямую зависит и от сбоеустойчивости. Некоторые методы обеспечения сбоеустойчивости устройств, реализованных на ПЛИС, приведены в [17].

Рис. 1. Структурная схема ПЛИС с элементом LUT с тремя входами

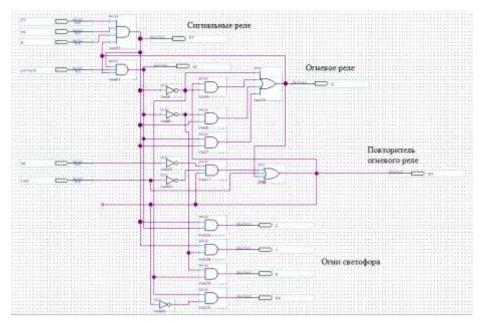

Для примера синтезируем схему управления железнодорожным светофором (рис. 2).

Рис. 2. Схема управления проходным светофором на логических элементах

На рисунке 2 присутствуют аналоги существующих элементов, таких как реле выбора направления (СНО, NP), огневые реле (О), повторитель огневого реле (Ороvtor), блокировочные реле (В), сигнальные реле (yellow, green, red), путевой приемник (РР), защитный участок (ZY) и сами огни светофора (G, Y, R).Для обеспечения временных параметров срабатывания элементов схема дополняется таймером.

Принцип работы схемы заключается в следующем: при вступлении поезда на блок-участок путевой приемник (или его аналог) этого блок-участка обесточивается, что приводит к прекрашению подачи питания на сигнальные реле и загоранию на светофоре красного показания. При занятии последующих блок-участков происходит аналогичная картина для устройств, относящихся к последующим огневым точкам. По прохождению первого блок-участка и последующего за ним защитного участка (можно отказаться от защитного участка) путевой приемник первого блок-участка становится под ток, тем самым коммутируя цепь питания сигнального реле «Ж», что приводит к загоранию желтого показания на светофоре. После освобождения второго блок-участка и последующего за ним защитного участка путевой приемник второго блок-участка становится под ток, коммутируя цепь питания сигнального реле «З», что приводит к загоранию зеленого показания на светофоре.

Следует отметить, что в данном варианте не требуется установка сигнальных и огневых реле, так как они указывают на исправность работы схемы. Исходя их этого, логично их заменить на более экономичные элементы, например, светодиоды.

Синтез схемы управления проходным светофором осуществляется в программной среде Quartus Prime на ПЛИС семейства «МАХ II» типа «EPM240T100C4».

### IV. СИНТЕЗ СХЕМЫ УПРАВЛЕНИЯ ПРОХОДНЫМ СВЕТОФОРОМ С ПОМОЩЬЮ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Синтезировать схему управления светофором будем с помощью программирования на языке Verilog HDL. Для увеличения параметров безопасности будет использоваться метод диверсионного программирования. Для этого запрограммируем заданную схему двумя различными способами.

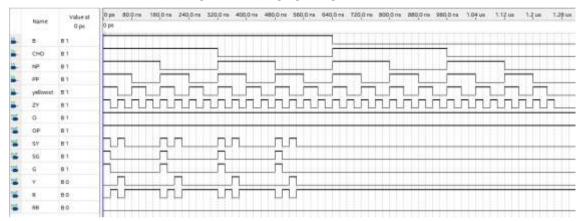

Первый способ заключается в задании булевых функций и представлен на рисунке 3.

В данном варианте присутствует аналог повторителя огневого реле. На рисунке 4 представлена симуляция работы спроектированной схемы.

В случае возникновения временных конфликтов в работе аналога огневого реле с помощью функции «#TIME» можно выставить задержку времени на его включение.

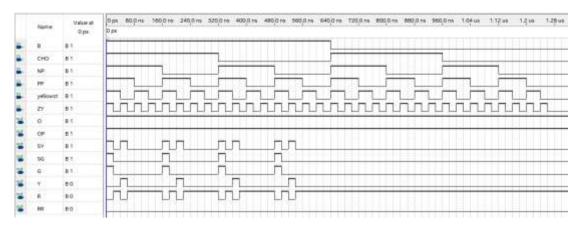

Второй способ задания схемы заключается в опросе входных данных и выводе тех или иных значений в зависимости от них. Код программы представлен на рисунке 5.

Результат работы такой схемы соответствует результату работы предыдущему варианту, что видно из рисунка 6.

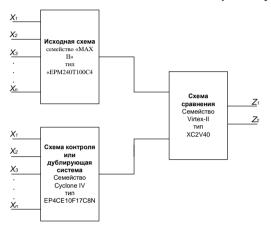

Для повышения безопасности каждая схема должна синтезироваться на отдельных кристаллах разных типов и семейств, а также выходные данные каждой из схем должны подаваться на схему сравнения, где они будут сравниваться и подаваться непосредственно на объект управления. Примерная структура такого устройства представлена на рис. 7.

```

Immodule svetofor (output Opovtor, output O, output yellow, output green, output G, output Y,

Loutput R, output RR, input NP, input CHO, input ZY, input PP, input B, input yellowst);

assign Opovtor=((~NP&(~CHO)&Opovtor)^CHO^O;

assign O=yellow&green^(~yellow)^yellow&(~green)^(~yellow&Opovtor);

assign O=yellow&green|

assign green=yellow&yellowst;

assign G=yellow&green;

assign Y=yellow&(~green);

assign R=(~yellow)&(~green);

assign RR=(~yellow)&(~O);

endmodule

```

Рис. 3. Первый способ программирования схемы

Рис. 4. Симуляция работы спроектированной схемы

```

adule s(output reg [0:0] OP, output reg [0:0] O, output reg [0:0] yellow, output reg [0:0] green, output reg [0:0] R, output reg [0:0] R, output reg [0:0] R, input NP, input NP

0 && yellow--0)

begin

D=01

yellowed; greened;

OP=0:

GeO:

Y=0:

R=0:

RR=1:

1 && CHO==1 && NP==1 && PP==1 && yellowst==1 && ZY==1)

op-i; yellow-i; green-i;

G-1:

ywo;

(8==1 && CHO==1 && NP==0 && PP==1 && yellowst==1 && ZY==1)

OP-1;

yellow-i; green-i;

G=1;

Y=0;

2=0;

OP-1; yellow-1; green-1;

G-1:

Y=0:

8+0;

(B--1 && CHO--0 && NP--0 && PP--1 && yellowst--1 && ZY--1)

OP-I:

yellow-1;

green-1;

6-1;

Y=0;

(B==1 && CHO==1 && NP==1 && PP==1 && yellowst==0 && ZY==1)

else

if (B-1 && CHO-D && NP-1 && PP-1 && yellowst-0 && ZY-1)

begin

Oli OP-I; yellow-I; green-0; G-0:

end

else

RR-Ot

if (8--1 && CHO--1 && NP--0 && PP--1 && yellowst--0 && ZY--1)

begin

0P-11

yellow-1:

green-0;

6-0:

Y=1;

8-0;

RR-01

end

else

if (8--1 && CHO--D && NP--D && PP--1 && yellowst--D && ZY--1)

begin

OP-1; yellow-1; green-D; G-0; Y-1; R-D;

99-0:

OP-I:

yellow-0; green-0;

R-1;

```

Рис. 5. Второй способ программирования схемы

Рис. 6. Симуляция работы спроектированной схемы

Рис. 7. Структура системы

### V. МЕТОДЫ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ СИСТЕМ, РЕАЛИЗОВАННЫХ НА ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМАХ

Для повышения вероятности обнаружения искажений в схемах, реализованных на ПЛИС, можно применять те же способы и решения, что и для микропроцессорных систем.

Для реализации внутреннего контроля можно применять избыточное кодирование. В большинстве случаев для этой цели применяются классические и модульные коды с суммированием [18-23] или линейные коды [24-26].

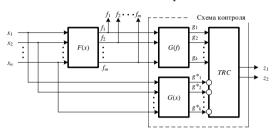

Система технического диагностирования реализуется на основе структурной схемы, представленной на рис. 8 [18, 19]. В ней исходное устройство F(x) снабжается схемой контроля, образованной тремя блоками: G(t), G(x) и TRC. Блок G(t) представляет собой преобразователь информационных векторов в контрольные векторы (является кодером выбранного кода). Блок G(x) также является преобразователем, однако в нем входным векторам сопоставляются контрольные векторы. Блок TRC позволяет сравнивать одноименные сигналы, формируемые на выходах блоков G(t) и G(x) и реализуется, как правило, в виде схемы сжатия на основе элементарных модулей сжатия парафазных сигналов. По этой причине выходы блока G(x) (либо блока G(t)) перед поступлением на входы блока TRC

предварительно инвертируются. Альтернативой такому подходу является предварительное инвертирование значений контрольных разрядов, вычисляемых блоком G(x) (либо блоком G(f)), на этапе синтеза соответствующих компонентов схемы контроля.

Рис. 8. Структурная схема системы диагностирования комбинационного устройства

Помимо широко используемых модульных кодов с суммированием можно использовать метод N-версионного программирования, как это было показано выше.

Цель данного метода заключается в обнаружении и маскировке возникающих ошибок для предотвращения опасных отказов и продолжения корректной работы системы. Для этого используется две и более программ, выполняющих одну и ту же функцию, после чего сравниваются результаты всех программ и выбирается нужный.

При диверсионном программировании (разрабатывается две программы) при расхождении результатов правильный результат определяется по дополнительным критериям, в то время как при многоверсионном программировании правильный результат определяется по мажоритарному признаку (выбирается тот результат, который наблюдается в большинстве вариантов программы).

N-версионное программирование ведет к увеличению времени выполнения программы и затрачиваемых ресурсов для реализации. В связи с этим разработчики применяют модифицированное диверсионное программирование, при котором применяется основная наиболее точная и сложная программа и более простая резервная программа [27 – 29].

#### VI. ЗАКЛЮЧЕНИЕ

Программируемые логические интегральные схемы с каждым днем внедряются в промышленность все больше и больше. Это связано с тем, что устройства на ПЛИС имеют меньшие габариты, по сравнению со своими аналогами, а также позволяют сократить расходы электроэнергии для своего функционирования. Однако, стоит отметить, что одиночные проекты на ПЛИС, не смотря на все свои преимущества, требуют больших финансовых затрат, по сравнению с микропроцессорными системами.

ПЛИС за время своего существования показали себя надежными и безопасными элементами, которые могут применяться как в простых схемах, не требующих высоких показателей надежности и безопасности, так и в ответственных системах, сбой которых может привести к катастрофическим последствиям.

Описанный в статье пример показывает, что их можно применять и в системах автоматики и телемеханики на железных дорогах. К тому же, фирмапроизводитель ПЛИС Xilinx в начале 2020 года начала производство микросхем специально для железнодорожного транспорта [30].

Аналогично приведенному примеру со светофором, на ПЛИС можно реализовать любые блочные системы с осуществлением всех закономерностей их работы, что будет соответствовать требованиям безопасности на железных работах.

Гибкая логика ПЛИС позволяет вносить изменения в программный код практически в любое время, что позволит значительно сократить расходы на модернизацию тех или иных объектов железнодорожной отрасли.

#### ЛИТЕРАТУРА

- [1] Berg M. Field Programmable Gate Array (FPGA) Single Event Effect (SEE) Radiation Testing. - NASA Electronic Parts and Packaging (NEPP) and Defense Threat, 2012. – 53p.

- [2] Желтов П.В. Применение FPGA в системах цифровой радиосвязи. Введение. РГРТУ 6с.

- [3] Кудрявцев А.В., Карцев К.П., Сергеев И.А., Федоров В.А., Якушев А.Г. Проект цифровой управляющей системы безопасности для энергоблоков АЭС с реакторами ВВЭР. Москва, Национальный исследовательский ядерный университет «МИФИ», 2012 144с.

- [4] Zaikin A.A., Zhemov V.S., Miroshnik Y.M., Pronyakin A.V., Sokolov I.V. New control systems for emergency protection of power reactors. «Ядерные измерительноинформационные технологии» №3, 2005 С. 30-55.

- [5] Кабецкий А.Г., Марков Д.С. Методы и инструментальные средства построения логических устройств электрической централизации на базе программируемых логических интегральных схем // Известия Петербургского университета путей сообщения. 2010. №2. С. 168-173.

- [6] Dobiáš R., Kubátová H. FPGA Based Design of Railway's Interlocking Equipment, Proceedings of EUROMICRO Symposium on Digital System Design, 2004, P. 467–473.

- [7] Бестемьянов П.Ф. Методы обеспечения безопасности аппаратных средств микропроцессорных систем управления движением поездов // Электротехника 2020 №9 сс.2-8.

- [8] Малиновский М.Л., Аленин Д.А., Барсов В.И, Коноваленко Н.В. Перспективы использования FPGА-технологий в системах железнодорожной автоматики // Вісник Харківського національного технічного університету сільського господарства імені Петра Василенка. Технічні науки. Харьков, 2012, Вип. 130: «Проблеми енергозабезпечення та енергозбереження в АПК України», С. 79-81.

[9] Максфилд К. Проектирование на ПЛИС. Курс

- [9] Максфилд К. Проектирование на ПЛИС. Курс молодого бойца. М.: Издательский дом «Додэка-ХХІ», 2007. - 408

- [10] Станционные системы автоматики и телемеханики: Учеб. для вузов ж.-д. трансп. / В. В. Сапожников, Б. М. Елкин, И. М. Кокурин и др.; Под ред. В. В.Сапожникова. - М.: Транспорт, 2000 - 432 с.

- [11] Виноградова В.Ю., Воронин В.Л., Казаков Е.А., Швалов Д.В., Шухина Е.Е. Перегонные системы автоматики: учебник для техникумов и колледжей ж.-д. транспорта / Под ред. В.Ю. Виноградовой. М.: Маршрут, 2005. 292 с.

- [12] Кондратьева Л.А., Ромашкова О.Н. Системы регулирования движения на железнодорожном транспорте: учебник для техникумов и колледжей ж.-д. транспорта. М.: Маршрут, 2003. 432 с.

- [13] Швалов Д.В. Приборы автоматики и рельсовые цепи: учебное пособие. — М.: ГОУ «Учебно-методический центр по образованию на железнодорожном транспорте», 2008. — 190 с.

- [14] Navabi Z. Embedded Core Design with FPGAs. McGrawHill Education, 433p.

- [15] Katz, R., Wang, J.J., Reed, R. et.al. (1999). The Effects of Architecture and Process on the Hardness of Programmable Technologies. – IEEE Transactions on Nuclear Science, NS-46.

- [16] Цыбин С., Быстрицкий А.. Интерфейсная ПЛИС повышенной надежности. // Электроника: наука, технология, бизнес. 2006 №6 С. 60-65.

- [17] Рухлов В.С., Соловьев Р.А., Кустов А.Г. Программноаппаратные решения повышения сбоеустойчивости комбинационных схем в базисе ПЛИС с учётом межсоединений и блоков ввода-вывода. // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2020. Вып.1. С. 113-118. DOI 10.31114/2078-7707-2020-1-113-118.

- [18]Сапожников В.В., Сапожников Вл.В., Ефанов Д.В. Коды с суммированием для систем технического диагностирования. Том 1: Классические коды Бергера и их модификации. М.: Наука, 2020. 383 с.

- [19] Сапожников В.В., Сапожников Вл.В., Ефанов Д.В. Коды с суммированием для систем технического диагностирования. Том 2: Взвешенные коды с суммированием. – М.: Наука, 2021. – 456 с.

- [20] Труды по теории синтеза самопроверяемых схем встроенного контроля на основе двоичных избыточных кодов: Т. 1 / Под ред. проф. Сапожникова Вал.В., Сапожникова Вл.В., Ефанова Д.В. – Москва: Издательство «Наука», 2020. – 611 с.

- [21] Труды по теории синтеза самопроверяемых схем встроенного контроля на основе двоичных избыточных кодов: Т. 2 / Под ред. проф. Сапожникова Вал.В., Сапожникова Вл.В., Ефанова Д.В. Москва: Издательство «Наука», 2021. 527 с.

- [22] Das D. Synthesis of Circuits with LowCost Concurrent

- Error Detection Based on Bose-Lin Codes / Das D., Touba N.A. // Journal of Electronic Testing: Theory and Applications. 1999. Vol. 15. Issue 1-2. Pp. 145-155. DOI: 10.1023/A:1008344603814.

- [23] Göessel M., New Methods of Concurrent Checking: Edition 1 / Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D // Dordrecht: Springer Science+Business Media B.V., 2008, 184 p.

- [24] Тельпухов Д.В., Жукова Т.Д., Деменева А.И., Гуров С.И. Схема функционального контроля для комбинационных схем на основе R-кода // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2018. Вып.4. С. 98-104. doi: 10.31114/2078-7707-2018-4-98-104.

- [25] Telpuhov D.V., Zhukova T.D., Demeneva A.I., Gurov S.I. Automatic Synthesis of Fault-Tolerant CED Circuits Based on R-Code // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2019. Вып. 3. С. 54-59. doi: 10.31114/2078-7707-2019-3-54-59.

- [26] Сапожников В.В., Сапожников Вл.В., Ефанов Д.В. Коды Хэмминга в системах функционального контроля логических устройств: монография. – СПб.: Наука, 2018. – 151 с.

- [27] Шубинский И.Б. Методы обеспечения функциональной надежности программ. Надежность. 2014;(4): С.87-101.

- [28] Ковалев, И. В. Оценка надежности мультиверсионной программной архитектуры систем управления и обработки информации Текст. / И. В. Ковалев, А. В. Новой, А. В. Штенцель // Вестник СибГАУ. 2008. № 3(20).-С. 50-52

- [29] Новой А.В. N-версионная программная архитектура с динамической структурой // Международный журнал экспериментального образования. — 2011. — № 5. — С. 131-133

- [30] Trains & Railways [Электронный ресурс] URL: https://www.xilinx.com/applications/industrial/railway.html #overview (Дата обращения 19.01.2021).

## Synthesis of control devices for objects of floor automation of railway transport on FPGA

#### A.V. Pashukov

#### Russian university of transport

#### art\_pash@mail.ru

Abstract — The possibilities of using FPGA in various industries are considered. The scope of application of devices based on programmable logic circuits is briefly considered. The possibility of using FPGAs in the railway industry is described by the example of creating a traffic light control scheme. It is shown that the known approaches to the design of control systems based on a relay or microprocessor base can be directly applied to the design of systems based on programmable logic circuits. Examples of improving security in the form of using modular codes with summation and N-version programming are given.

Keywords — field-programmable gate array, traffic light control system, N-version programming, codes with summation.

#### REFERENCES

- Berg M. Field Programmable Gate Array (FPGA) Single Event Effect (SEE) Radiation Testing. - NASA Electronic Parts and Packaging (NEPP) and Defense Threat, 2012. – 53p.

- [2] Zheltov P.V. Application of FPGA in digital radio communication systems. Introduction. RGTU 6p.

- [3] Kudryavtsev A.V., Kartsev K. P., Sergeev I. A., Fedorov V A., Yakushev A. G. Project of digital safety control system for NPP power units with VVER reactors. – Moscow, National Research Nuclear University " MEPhI», 2012 – 144p.

- [4] Zaikin A.A., Zhemov V.S., Miroshnik Y.M., Pronyakin A V., Sokolov I.V. New control systems for emergency protection of power reactors. – «Nuclear measurement and information technologies» №3, 2005 – p. 30-55.

- [5] Kabetsky A. G., Markov D. S.. Methods and tools for constructing logic devices of electric interlocking based on programmable logic integrated circuits // News of the St. Petersburg University of Railway Transport. – 2010. - №2. – p. 168-173.

- [6] Dobiáš R., Kubátová H. FPGA Based Design of Railway's Interlocking Equipment, Proceedings of EUROMICRO Symposium on Digital System Design, 2004, p. 467–473.

- [7] Bestemyanov P. F. Methods of ensuring the safety of hardware of microprocessor-based train traffic control systems// Electrotehnica-2020 No. 9 p. 2-8.

- [8] Malinovsky M. L., Alenin D. A., Barsov V. I., Konovalenko N V. Prospects of using FPGA technologies in railway automation systems // Bulletin of the Petro Vasilenko Kharkiv National Technical University of Agriculture. Technical sciences. - Kharkiv, 2012, Issue 130: "problems of energy supply and energy saving in the agroindustrial complex of Ukraine», p. 79-81.

- [9] Maxfield K. Design on FPGA. The course of a young fighter. Moscow: Publishing house "Dodeka-XXI", 2007. -408 p.

- [10] Station systems of automation and telemechanics: Textbook for universities of railway transport / V. V. Sapozhnikov, B. M. Elkin, I. M. Kokurin, etc.; Ed. by V. V. Sapozhnikov. - M.: Transport, 2000-432 p.

- [11] Vinogradova V. Y., Voronin V. L., Kazakov E. A., Shvalov D. V., Shukhina E. E. Automatic systems on the stage: textbook for technical schools and colleges of railway transport / Edited by V. Yu. Vinogradova. - M.: Marshrut, 2005 — - 292 p.

- [12] Kondratieva L. A., Romashkova O. N. Systems of traffic regulation in railway transport: textbook for technical schools and colleges of railway transport. - M.: Marshrut, 2003 — - 432 p.

- [13] Shvalov D. V. Automation devices and rail chains: a textbook. - M.: State Educational Institution "Educational and Methodological Center for Education in railway transport", 2008. - 190 p.

- [14] Navabi Z. Embedded Core Design with FPGAs. McGraw-Hill Edu-cation, 433p.

- [15] Katz, R., Wang, J.J., Reed, R. et.al. (1999). The Effects of Architecture and Process on the Hardness of Programmable Technologies. – IEEE Transactions on Nuclear Science, NS-46.

- [16] Tsybin S., Bystritsky A. Interface FPGA of increased reliability. // Electronics: science, technology, business. 2006 No. 6, p. 60-65.

- [17] Rukhlov V. S., Solovyov R. A., Kustov A. G. Software and hardware solutions for improving the fault tolerance of combinational circuits in the FPGA basis, taking into account interconnects and input-output blocks // Problems of Perspective Micro- and Nanoelectronic Systems Development. 2020. Issue 1. P. 113-118. doi: 10.31114/2078-7707-2020-1-113-118.

- [18] Sapozhnikov V. V., Sapozhnikov VI. V., Efanov D. V. Codes with summation for technical diagnostics systems. Volume 1: Classical Berger codes and their modifications. -Moscow: Nauka, 2020. - 383 p.

- [19] Sapozhnikov V. V., Sapozhnikov VI. V., Efanov D. V. Codes with summation for technical diagnostics systems. Volume 2: Weighted codes with summation. - Moscow: Nauka, 2021 - - 456 p.

- [20] Proceedings on the theory of synthesis of self-checking embedded control schemes based on binary redundant codes: Vol. 1 / Ed. prof. Sapozhnikov V. V., Sapozhnikov Vl. V., Efanov D. V.-Moscow: Publishing house "Nauka", 2020 – - 611 p.

- [21] Proceedings on the theory of synthesis of self-checking embedded control schemes based on binary redundant codes: Vol. 2 / Ed. prof. Sapozhnikov V. V.,

- Sapozhnikov VI. V., Efanov D. V.-Moscow: Publishing house "Nauka", 2021. 527 p.

- [22] Das D. Synthesis of Circuits with Low-Cost Concurrent Error Detection Based on Bose-Lin Codes / Das D., Touba N A. // Journal of Electron-ic Testing: Theory and Applications. – 1999. – Vol. 15. – Issue 1-2. – p. 145-155. – DOI: 10.1023/A:1008344603814.

- [23] Göessel M., New Methods of Concurrent Checking: Edition 1 / Göes-sel M., Ocheretny V., Sogomonyan E., Marienfeld D // Dordrecht: Springer Science+Business Media B.V., 2008, 184 p.

- [24] Telpuhov D.V., Zhukova T.D., Demeneva A.I., Gurov S.I. Circuit of Functional Control for Combinational Circuits Based on R-Code // Problems of Perspective Micro- and Nanoelectronic Systems Development. 2018. Issue 4. P. 98-104. doi: 10.31114/2078-7707-2018-4-98-104.

- [25] Telpuhov D.V., Zhukova T.D., Demeneva A.I., Gurov S.I. Automatic Synthesis of Fault-Tolerant CED Circuits Based on R-Code // Problems of Perspective Micro- and Nanoelectronic Systems Development. 2019. Issue 3, P. 54-59. doi: 10.31114/2078-7707-2019-3-54-59.

- [26] Sapozhnikov V. V., Sapozhnikov VI. V., Efanov D. V. Hamming codes in systems of functional control of logical devices: monograph. - St. Petersburg: Nauka, 2018. - 151 p.

- [27] Shubinsky I. B. Methods of ensuring the functional reliability of programs. Reliability. 2014;(4): p. 87-101.

- [28] Kovalev, I. V. Evaluation of the reliability of multiversion software architecture of control systems and information processing Text. / I. V. Kovalev, A.V. Novoi, A.V. Shtenzel // Bulletin of SibGAU. 2008. № 3(20).-p. 50-52

- [29] Novoy A.V. N-version software architecture with dynamic structure // International Journal of Experimental Education. - 2011. - No. 5. - p. 131-133

- [30]URL:https://www.xilinx.com/applications/industrial/railway. html#overview (access date:19.01.2021).