# Методика расчета зависимых временных ограничений для библиотек стандартных цифровых ячеек

С.А. Ильин $^{1,3}$ , О.В. Ласточкин $^{1}$ , Н.А. Ищенко $^{2,3}$

<sup>1</sup> НИИ молекулярной электроники (АО «НИИМЭ»), г. Москва, silin@niime

$^2$ ООО «Эн-Экс-Пи Семикондакторс», г. Москва, nikita.ishchenko@nxp.com

<sup>3</sup> Национальный Исследовательский Университет «МИЭТ»

Аннотация Увеличение тактовой частоты функционирования по-прежнему остается одним из важнейших требований к современным Системам-на-Кристалле (СнК). Существуют различные способы решения данной проблемы. Особую роль в формировании тактового сигнала играют временные ограничения. В данной статье рассмотрены различные способы определения временных ограничений setup и hold для последовательностных схем. Приведена методика, позволяющая уменьшить пессимизм при расчете зависимых временных ограничений.

Ключевые слова — триггер, последовательностная схема, частота функционирования, временные ограничения, цифровая библиотека, библиотека стандартных ячеек, маршрут проектирования; нанометровая технология, система на кристалле (СнК).

### І. Введение

Частота функционирования Систем-на-Кристалле (СнК) постоянно растёт [1]. Рабочие частоты в диапазоне 1 ГГц широко распространены современных интегральных схемах определении максимальных тактовых частот в проекте важным фактором является точность синхронизации данных. Проверка эффективности построения дерева сверхбольших интегральных синхронизации В схемах (СБИС) выполняется с помощью инструментов статического временного анализа (CBA, STA). Специализированные методы статического временного анализа обеспечивают полноту и надежность анализа быстродействия, однако не гарантируют достоверности результата [5].

Инструменты статического временного анализа используют для расчета данные, содержащиеся в комплекте поставки библиотеки стандартных ячеек. В настоящее время промышленным стандартом для статического временного анализа является формат Liberty, получаемый в автоматизированном режиме с использованием специализированных САПР характеризации - Synopsys SiliconSmart, Cadence Liberate и др. Liberty-файл позволяет точно моделировать быстродействие, мощность и шумы [4].

Характеризация отдельных ячеек в библиотеке очень важна с точки зрения точности результатов статического временного анализа. Неточная характеризация временных ограничений приводит к тому, что результаты статического временного анализа либо чрезмерно оптимистичны, либо пессимистичны. Следует избегать обоих случаев, так как наилучший случай может привести к отказу уже изготовленной схемы, тогда как наихудший — излишне снизить характеристики схемы, затрудняя достижение целевой частоты функционирования СБИС.

На практике применяются два основных метода характеризации временных ограничений: независимый и зависимый. Независимая характеризация временных ограничений показывает заметно более оптимистичные результаты, в то время как зависимый метод может быть излишне пессимистичен. В данной работе описывается комплексная методика нахождения сбалансированных и реалистичных значений временных ограничений setup и hold.

Раздел II содержит теоретические основы определения временных ограничений и статического временного анализа временным ограничениям. В разделе III описываются современные подходы к характеризации временных ограничений, представлена концепция зависимости временных ограничений и формально определяется проблема. Предлагаемые методика и алгоритм характеризации приведены в Разделе IV. Выводы и заключение представлены в разделе V.

#### II. Справочная информация

Основная справочная информация о последовательностных схемах представлена в разделе II-А. Основы статического временного анализа, а также информация о временных ограничениях setup и hold рассматриваются в разделах II-В и II-С.

#### А. Последовательностные схемы

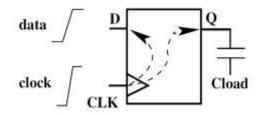

Типовая последовательностная схема (показана на рис.1) содержит вход данных D, вход тактового сигнала CLK и выход Q. Базовыми последовательностными схемами являются триггеры по фронту и уровню.

Рис. 1. Общий вид базовой последовательностной схемы

Последовательностная схема имеет два временных пути: первый - от входа CLK к входу D для определения временных ограничений setup и hold, второй — от входа CLK к выходу Q для определения задержки переключения выхода по фронту / срезу тактового сигнала.

#### В. Статический временной анализ

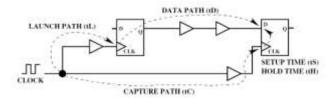

Входными данными для САПР статического временного анализа являются список элементов и их соединений, библиотека стандартных ячеек и файл с временными ограничениями в формате .sdc (Synopsys Design Constraint) информация из которого используется для расчёта запаса по времени предустановки (setup slack или SS) и запаса по времени удержания (hold slack HS) для наихудшего случая. Общая схема вычисления параметров показана на рис. 2. Значения параметров вычисляются следующим образом:

$$SS = min(tC + T) - max(tL + tD + tS), \tag{1}$$

$$HS = min(tL + tD) - max(tC + tH), \tag{2}$$

где tC — задержка пути захвата, tL — задержка пути запуска, tD — задержка передачи по входу данных, tS — время предустановки, tH — время удержания.

Рис. 2. Вычисление запасов по времени установки / удержания на примере синхронной передачи данных

Отрицательное значение *slack* считается нарушением. В случае нарушения *setup slack* схема может функционировать корректно, на более низкой частоте, при нарушении *hold slack* схема функционировать правильно не может [5].

# С. Временные ограничения setup и hold

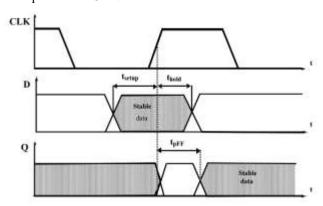

Последовательностные характеризуется схемы тремя важными временными параметрами, показанными на рис. 3. Временем установки (setup) называется временной интервал, в течение которого входные данные D должны оставаться стабильными до переключения синхросигнала CLK. Временем удержания (hold) называется временной интервал, в течение которого входные данные D

оставаться стабильными после переключения синхросигнала CLK.

Рис. 3. Определение временных ограничений и задержки распространения сигнала в последовательностных схемах

В соответствии с требованием отсутствия нарушений по параметру slacks выражения (1) и (2) могут быть представлены в следующем виде:

$$min(tC + T) - max(tL + tD) \ge max(tS),$$

(3)

$$min(tL + tD) - max(tC) \ge max(tH).$$

(4)

Неравенства (1) и (2) требуют, чтобы разница, называемая *skew*, была больше или равна значению временного ограничения. Поэтому данные неравенства могут быть преобразованы к следующем виду:

$$min(setupskew) \ge max(setuptime),$$

(5)

$$min(holdskew) \ge max(holdtime).$$

(6)

Следует обратить внимание на важное различие: параметры setup и hold skews относятся к любой разнице во времени между входными данными D и синхросигнала CLK, тогда как параметры setup и hold times относятся к разнице во времени, необходимой для надежного захвата и хранения данных. Согласно (1) и (2), чем меньше значения параметров setup и hold times, тем больше значения параметров setup slack slack

## III. СУЩЕСТВУЮЩИЕ ПОДХОДЫ К ХАРАКТЕРИЗАЦИИ ВРЕМЕННЫХ ОГРАНИЧЕНИЙ

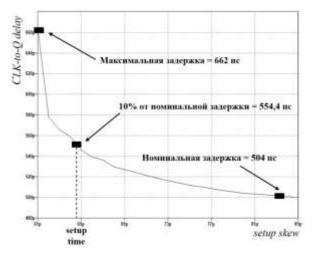

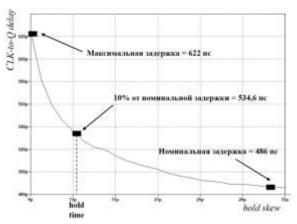

Наиболее распространенный подход к определению значения параметра setup time состоит в анализе взаимовлияния параметров setup skew и задержки CLK-to-Q при фиксированном hold skew (аналогично для hold time). Общий принцип такого подхода показан на рис. 4 для setup time и на рис. 5 для hold time. Согласно [8] для обоих графиков могут быть определены три области: стабильная, метастабильная и область отказа.

Стабильная область определяется как область, в которой задержка CLK-to-Q не зависит от setup или hold skew. По мере уменьшения skew задержка CLK-to-Q начинает расти экспоненциально. Если значение

skew слишком мало, схема не сможет зафиксировать данные. Эта область называется областью отказа. Область между стабильной областью и областью отказа называется метастабильной областью.

Рис. 4. Зависимость задержки *CLK-to-Q* от *setup skew* для последовательностных схем (independent mode)

Puc. 5. Зависимость задержки CLK-to-Q от hold skew для последовательностных схем (dependent mode)

Времена *setup* и *hold* не могут быть в области отказа, так как в этом случае последовательностная схема не сможет записать данные. Время *setup* (*hold*) обычно устанавливается на *setup* (*hold*) *skew*, когда стабильная область переходит в метастабильную область. В некоторых подходах может допускаться определенное ухудшение задержки перехода *CLK-to-Q* [6]. Например, на рис. 4 и рис. 5 предполагается 10%ное ухудшение. В некоторых других подходах *setup* (*hold*) *time* — это точка на графике, когда минимизируется сумма *setup* (*hold*) *skew* и задержка *CLK-to-Q*.

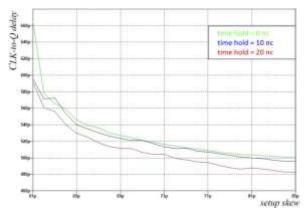

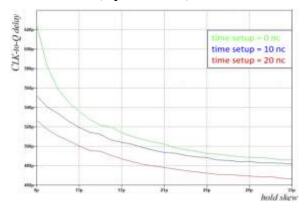

Времена *setup* и *hold* являются зависимыми. Эти ограничения являются функцией противоположных *skews* (*hold skew* для *setup time* и *setup skew* для *hold time*), как показано на рис. 6,7.

Важно отметить, что *setup* уменьшается по мере увеличения *hold skew*, а *hold* уменьшается с увеличением *setup skew*. Таким образом, наименьшие

setup и hold times можно получить при наибольших противолежащих skews.

Puc. 6. Зависимость задержки CLK-to-Q от setup skew при разных hold skew для последовательностных схем (dependent mode)

Puc. 7. Зависимость задержки *CLK-to-Q* от *hold skew* при разных *setup skew* для последовательностных схем (dependent mode)

Данную зависимость между временами setup и hold можно объяснить следующим образом. Так как задержка CLK-to-Q зависит как от setup skew, так и от hold skew, она может быть преимущественно определена либо стороне setup, либо стороне hold. Например, если setup skew маленькое, то именно этот skew доминирует над ухудшением задержки CLK-to-Q; следовательно, hold skew должно быть относительно большим. То же самое относится и к hold skew.

Существующие подходы характеризации последовательностных элементов обычно игнорируют зависимость времен *setup* и *hold*. Эта стратегия приводит к двум основным проблемам:

Проблема 1. Если предполагается, противоположные setup skews и hold skews излишне велики, итоговые значения времен setup и hold будут оптимистичными. В случае, если форма сигнала большим ланных Dне удовлетворяют противоположным skews, оптимистичные времена setup и hold приведут к отказу схемы, несмотря на то нарушаются какие-либо отдельные ограничения. В качестве альтернативы, предполагается, что соответствующие setup skews и hold skews излишне малы, результирующие времена setup и hold будут пессимистичными. Следует избегать обоих случаев, поскольку оптимистичный случай может вызвать сбои схемы после изготовления, тогда как пессимистический случай может вызвать ложные нарушения во время статического временного анализа.

**Проблема 2.** Если зависимость времен setup / hold учитывается при характеризации, но не используется для минимизации суммы «setup+hold», упускается возможность уменьшить количество временных нарушений, а также улучшить ожидаемый slack.

Предлагаемая в статье методика позволяет решить данные проблемы.

#### IV. ПРЕДЛАГАЕМАЯ МЕТОДИКА

В ходе исследования установлено, что зависимый фронт (setup edge для dependent-setup и hold edge для dependent-hold) чувствителен К положению противоположного зафиксированного фронта (restrained edge) относительно положения синхросигнала CLK. Если зафиксированный фронт (hold edge для dependent-setup и setup edge для несколько dependent-hold) изменить всего на пикосекунд, как показано на рис. 8, это позволит зависимому фронту сократиться лесятки пикосекунд на этапе оптимизации.

Рис. 8. Изменение зафиксированного фронта входа данных D относительно положения синхросигнала CLK

Таким образом, изменяя положение зафиксированного фронта, можно найти минимальное значение суммы setup+hold. Значение, которое прибавляется к зафиксированному фронту называется margin. В САПР характеризации Synopsys SiliconSmart, помимо базовых Independent и Dependent режимов, поддерживаются также режимы Dependent-Setup и Dependent-Hold для расчёта временных ограничений [7]. Например, в Dependent-Setup зафиксированным фронтом является фронт, связанный с hold, именно к нему и прибавляется margin. Фронт входа данных D, связанный с setup, является зависимым.

Предлагаемая методика состоит их четырех этапов:

- 1. Расчет временных ограничений в режиме Independent и Dependent для определения границ области поиска значения margin;

- 2. Отдельно находятся значения margin для setup из режима Dependent-Hold;

- 3. Отдельно находятся значения margin для hold, из режима Dependent-Setup;

4. Для каждого из режимов выбирается *margin*, соответствующий минимальной сумме *setup+hold*.

Кроме того, данный алгоритм выполняется дважды для суммы  $rise\ setup\ +\ fall\ hold\$ и суммы  $fall\ setup\ +\ rise\ hold\$ .

Так как при разработке стандартных ячеек применяются общие базовые схемотехнические решения основных узлов [8], авторы считают возможным использование единого значения *margin* для всех последовательностных ячеек.

Рассмотрим более детально данную методику на примере синхронного D-триггера, тактируемого передним фронтом. Для упрощения расчетов были выбраны значения, соответствующие центральным индексам длительностей входного фронта. Временные ограничения, полученные независимым и зависимым режимами характеризации, указаны в таблице 1. В таблице 2 приведены рассчитанные суммы setup+hold для обоих режимов.

Таблица 1 Временные ограничения для разных режимов характеризации на примере ячейки dffp

| Режим          | Независимый | Зависимый |

|----------------|-------------|-----------|

| hold_fall, πc  | -3,213      | 4,609     |

| hold_rise, пс  | -11,523     | 0,693     |

| setup_fall, пс | 24,617      | 36,832    |

| setup_rise, пс | 21,402      | 29,224    |

Таблица 2

Сумма setup+hold для разных режимов характеризации на примере ячейки dffp

| Режим                         | Независимый | Зависимый |

|-------------------------------|-------------|-----------|

| hold_fall<br>+ setup_rise, пс | 18.189      | 33.833    |

| hold_rise +<br>setup_fall, пс | 13.094      | 37.525    |

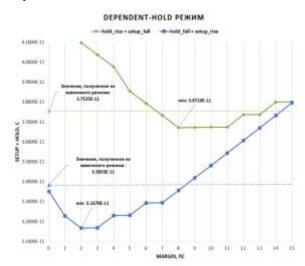

Как было отмечено ранее, независимый режим является чрезмерно оптимистичным, тогда как зависимый пессимистичным. Полученные значения могут служить границами поиска суммы *margin* для уменьшения суммы *setup+hold*.

Далее выполняется характеризация в Dependent-Hold и Dependent-Setup режимах, результаты для которых показаны на рис. 9 и рис. 10 соответственно. По умолчанию для входа данных D ширина окна временных ограничений рассчитывается следующим образом,

$$window_{Data} = (iS + mS) + dH, \tag{7}$$

где iS — независимый setup, mS — margin для независимого setup, dH — зависимый hold, что для данного случая соответствует «Dependent-Hold» режиму.

Puc. 9. График изменения суммы setup+hold в зависимости от margin в Dependent-Hold режиме

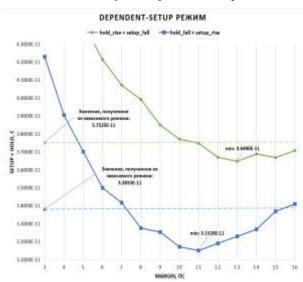

Рис. 10. График изменения суммы setup+hold в зависимости от margin в Dependent-Setup режиме

Для сканирующих входов расчёт ширины окна временных ограничений, следующий:

$$window_{Scan} = (iH + mH) + dS, \qquad (8)$$

где iH — независимый hold, mH — margin для независимого hold, a dS — зависимый setup. Dependent-Setup режим полностью соответствует данному случаю.

Для случаев, когда рассматриваются  $rise\ setup + fall\ hold$ ,  $fall\ setup\ +\ rise\ hold\$ одновременно, можно варьировать суммой setup+hold, находя значение margin, которое уменьшает ширину окна временных

ограничений для обоих переключений относительно значения, полученного из зависимого режима характеризации. Возвращаясь к представленному примеру, для способа расчета *Dependent-Setup* видно, *что* значение *margin* равное 12 пикосекундам, подходит для уменьшения суммы *setup+hold*.

#### V. ЗАКЛЮЧЕНИЕ

В данной статье рассмотрены основные особенности методик характеризации временных ограничений последовательностных ячеек, проанализированы их преимущества и недостатки. Проведено сравнение режимов характеризации на примере синхронного D-триггера, тактируемого передним фронтом с использованием САПР Synopsys SiliconSmart.

В результате анализа различных методов расчета временных ограничений, была предложена методика расчёта временных ограничений с использованием запаса по времени (margin). Данная методика позволяет получать более реалистичные значения временных ограничений.

#### Поддержка

Статья подготовлена в рамках госзадания МИЭТ (тема 0719-2020-0017/FSMR-2020-0017).

#### ЛИТЕРАТУРА

- [1] Красников Г.Я. Конструктивно-технологические особенности субмикронных МОП-транзисторов // В 2-х частях / Москва, 2004. Часть 2.

- [2] Красников Г.Я., Зайцев Н.А., Красников А.Г. Современное состояние разработок в области энергонезависимой памяти// Нано-и микросистемная техника. 2015.No4(177). С. 60-64.

- [3] Гаврилов С.В., Гудкова О.Н., Северцев В.Н. Интервальный статический временной анализ КМОП-схем с учетом логических корреляций // Проблемы разработки перспективных микро- и наноэлектронных систем 2012. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2012. С. 113-118.

- [4] А.Л. Стемпковский, С.В. Гаврилов, А.Л. Глебов. Методы логического и логико-временного анализа цифровых КМОП СБИС// Москва, Наука, 2007. 220 с.

- [5] Emre Salman, Ali Dasdan, Feroze Taraporevala, Kayhan Kucukcakar, Eby G. Friedman Pessimism Reduction In Static Timing Analysis Using Interdependent Setup and Hold Times // International Symposium on Quality Electronic Design − 2006. № 7.

- [6] V. Stojanovic and V.G. Oklobdzija Comparative Analysis of Master-Slave Latches and Flip-Flops for High-Performance and Low-Power Systems // IEEE Journal of Solid-State Circuits 1999. V. 34. № 4. P. 536–548.

- [7] "SiliconSmart ACE User Guide" in Synopsys Inc, Mountain View, CA, vol. 2016, no. 09, 2016.

- [8] С.А. Ильин "Поиск базовых схемотехнических решений для проектирования библиотек цифровых ячеек". «Электроника. Известия вузов», 2015, том 20, №1, стр. 44-49

# Methodology of calculating dependent timing constraints for libraries of standard digital cells

S.A. Ilyin<sup>1,3</sup>, O.V. Lastochkin<sup>1</sup>, N.A. Ischenko<sup>2,3</sup>

<sup>1</sup> Research Institute of Molecular Electronics (JSC "NIIME"), Moscow, silin@niime

<sup>2</sup> LLC NXP Semiconductors, Moscow, nikita.ishchenko@nxp.com

<sup>3</sup> National Research University "MIET"

Abstract — One of the most important problems of modern Systems-on-Chip (SoC) is increasing the clock frequency. There are various ways to solve this problem. This article discusses various ways to define setup and hold timing constraints for sequential circuits. Presented technique allows to reduce pessimism when calculating dependent timing constraints. The study found that the dependent edge (setup edge for dependent-setup and hold edge for dependent-hold) is sensitive to the position of the restrained edge relative to the position of the clock CLK. If the fixed edge (hold edge for dependent-setup and setup edge for dependent-hold) is changed by just a few picoseconds, this will allow the dependent edge to be reduced by dozens of picoseconds during the optimization stage. Thus, by changing the position of the locked edge, you can find the minimum value of the setup + hold sum. The value that was added to the fixed edge is called margin. Synopsys SiliconSmart has Independent and Dependent modes, the Dependent-Setup and Dependent-Hold modes are supported for calculating timing constraints. For example, in Dependent-Setup, the fixed edge is the front associated with hold, and it is to this edge that the margin is added. The proposed technique consists of four stages:

- 1. Calculation of timing constraints in the Independent and Dependent modes to determine the boundaries of the search area for the margin value;

- 2. Margin values for setup from the Dependent-Hold mode are calculated separately;

- 3. Values for the hold margin from the Dependent-Setup mode are calculated separately:

- 4. For each of the modes, a margin is selected that corresponds to the minimum amount of setup + hold.

Algorithm is executed twice for the amount of rise setup + fall hold and the amount of fall setup + rise hold. Since when developing standard cells common basic circuit solutions of the main nodes are used [8], the authors consider it possible to use the same margin value for all sequential cells. This article discusses the main features of the methods for characterizing timing constraints, analyzes their advantages and disadvantages. Comparison of the characterization modes was carried out using the example of a synchronous D-flip-flop clocked by the leading edge using the Synopsys SiliconSmart CAD system. This technique allows you to get more realistic values of timing constraints.

Keywords — flip-flop, frequency, timing constraints, digital library, standard cell library, design flow; nanometer technology, system-on-a-chip (SoC).

#### REFERENCES

- [1] Krasnikov G.Ya. Konstructivno-technologicheskie osobennosti submikronnikh MOP-tranzistorov (Design and technological features of submicron MOS transistors) // v 2-kh chastyakh / Moskva, 2004. Chast 2

- [2] Krasnikov G.Ya, Zaytsev N.A., Krasnikov A.G. Sovremennoye sostoyaniye razrabotok v oblasti energonezavisimoy pamyati// Nano-i mikrosistemnaya tekhnika (The current state of developments in the field of non-volatile memory) // Nano-and microsystem technology 2015.No4(177). C. 60-64.

- [3] Gavrilov S.V., Gudkova O.N., Severtsev V.N. Interval'nyy staticheskiy vremennoy analiz KMOP-skhem s uchetom logicheskikh korrelyatsiy (Interval static time analysis of CMOS circuits taking into account logical correlations) // Problems of the development of promising micro- and nanoelectronic systems - 2012. Proceedings / edited by academician A.L.Stempkovsky. Moscow: IPPM RAS, 2012. 113-118.

- [4] A.L.Stempkovsky, S.V.Gavrilov, A.L.Glebov. Metody logicheskogo i logiko-vremennogo analiza tsifrovykh KMOP SBIS (Methods of logical and logical-time analysis of digital CMOS VLSI) // Moscow, Nauka, 2007. 220 p.

- 5] Emre Salman, Ali Dasdan, Feroze Taraporevala, Kayhan Kucukcakar, Eby G. Friedman Pessimism Reduction In Static Timing Analysis Using Interdependent Setup and Hold Times // International Symposium on Quality Electronic Design 2006. № 7.

- [6] V. Stojanovic and V.G. Oklobdzija Comparative Analysis of Master-Slave Latches and Flip-Flops for High-Performance and Low-Power Systems // IEEE Journal of Solid-State Circuits – 1999. V. 34. № 4. P. 536–548.

- [7] "SiliconSmart ACE User Guide" in Synopsys Inc, Mountain View, CA, vol. 2016, no. 09, 2016.

- [8] S.A.Ilyin Poisk bazovykh skhemotekhnicheskikh resheniy dlya proyektirovaniya bibliotek tsifrovykh yacheyek ("Search for basic circuit solutions for the design of libraries of digital cells") "Electronics. Izvestiya vuzov ", 2015, volume 20, No. 1, pp. 44-49