# Алгоритм оптимизации энергопотребления стандартных ячеек на основе методологии Logical Effort

М. А. Заплетина<sup>1,2</sup>, С. А. Ильин<sup>1,3</sup>, О. В. Ласточкин<sup>3</sup>

<sup>1</sup>НИУ «Московский институт электронной техники»,

<sup>2</sup>Институт проблем проектирования в микроэлектронике РАН (ИППМ РАН),

<sup>3</sup>AO «Научно-исследовательский институт молекулярной электроники», г. Зеленоград, silin@mikron.ru

Аннотация — Задержка и потребляемая мощность являются одними из ключевых характеристик, учитываемых при проектировании стандартных цифровых элементов. В работе предлагается метод оптимизации размеров транзисторов. использует произведение этих величин (Power-Delay Product, PDP) в качестве целевой функции. Для минимизации PDP за счёт масштабирования размеров построена специальная математическая модель. Результаты её применения получены в базисе КМОП-технологии 28 нм на примере цепочки из трёх и пяти инверторов, комбинационной схемы и схемы однобитного сумматора.

*Ключевые слова* — PDP, Logical Effort, библиотека стандартных элементов, оптимизация.

#### I. Введение

Поиск оптимального соотношения между ключевыми характеристиками (в первую очередь, задержками и потребляемой мощностью) цифровых ячеек представляет собой неотъемлемый этап в разработке библиотек стандартных цифровых для современных полупроводниковых технологий [1,2]. Важность соотношения мощности и задержки особенно отмечалась в исследованиях [6-8], где оптимизация выполнялась за счёт снижения производительности.

Одним из популярных методов минимизации задержек логических вентилей путем масштабирования их размеров является метод Logical Effort (LE) [3]. Основные положения этого метода изложены в разделе II.

Распространенной техникой снижения мощности с учетом ограничения производительности является подбор напряжения питания и порогового напряжения транзисторов [1,4,5,10,11]. В одном из предыдущих исследований [9] выполнялся поиск оптимального напряжения питания для получения максимальных показателей энергоэффективности. Кроме того, для достижения своей цели авторы [9] использовали алгоритмы подбора размеров транзисторов [6].

В данной работе представлена математическая модель для оптимизации мощности и задержки за счёт масштабирования размеров вентилей. Предлагаемый на её основе метод позволяет снизить потребляемую мощность за счёт приемлемых потерь производительности.

Дальнейшее содержимое статьи организовано следующим образом. В разделе II в краткой форме даны основы исходного метода. Раздел III посвящен формированию целевой функции предложенного метода и математическому моделированию. Раздел IV содержит результаты применения метода и их обсуждение. Выводы и заключение представлены в разделе V.

## II. Основные положения метода Logical Effort

Назначение метода LE состоит в быстрой оценке быстродействия КМОП-схемы и размеров вентилей, необходимых для его достижения, без схемотехнического моделирования. В этом методе задержка представляется в виде двухкомпонентной величины и определяется по формуле (1):

$$D = f + p, (1)$$

где f - ёмкостный компонент относительно базового инвертора с аналогичной нагрузочной способностью, p - нормализованная паразитная задержка вентиля.

В свою очередь переменная f разделяется на две составляющие: логическую g и электрическую h. Параметр д представляет собой отношение входной ёмкости рассматриваемого вентиля и базового инвертора, обладающего такой же нагрузочной способностью. Значение этого параметра является конкретного класса вентилей, константой для одну логическую реализующих функцию, определяется внутренними свойствами вентилей. Электрическая составляющая h содержит отношение выходной и входной ёмкостей вентиля. Так, формулу (1) можно записать в виде (2):

$$D = gh + p \tag{2}$$

Задержка логического вентиля может быть представлена следующим образом (3):

$$t_{nd} = D \times \tau, \tag{3}$$

где *т* — внутренняя задержка базового инвертора.

В соответствии с методом LE [3], минимальная задержка цепи может быть получена в случае, когда все входящие в неё вентили имеют одинаковое значение параметра f, определяемое следующим образом (4):

$$f = g_i \times h_i = F^{1/n},\tag{4}$$

$$D_{min} = n \times F^{1/n} + P, \tag{5}$$

где n — количество логических элементов в цепи, F — значение компонента f для полного пути, а P — полная паразитная задержка.

## III. ОБЩИЙ ВИД ЦЕЛЕВОЙ ФУНКЦИИ

В качестве целевой функции было выбрано произведение средней задержки вентиля и средней потребляемой им мощности. Формализация целевой функции дана далее.

Компромисс между уменьшением мощности или задержки при проектировании стандартных ячеек может быть найден посредством изменения размеров вентилей или, в терминах LE подхода, путем изменения значения величины h. Согласно разделу II, минимальная задержка цепи может быть получена в случае, когда все входящие в неё вентили имеют одинаковое значение параметра f, определяемое по формуле (4).

Предполагается, что за счет изменения значений параметров h, входящих в выражение для целевой функции, можно будет найти размеры вентилей, для которых значение целевой функции будет минимальным. Скорректированное значение параметра h представляется в виде h+x, где x — поправка, необходимая для минимизации значения целевой функции.

Поиск минимума целевой функции осуществлялся относительно вносимой поправки х. Предлагаемое решение основано на предположении, что поправка х идентична для всех вентилей. Предлагаемый вид поправки (в виде слагаемого к параметру h) используется для простоты преобразований уравнения и, по мнению авторов, даёт приемлемый результат в сравнении с традиционными методами масштабирования, в основном ориентированными на быстродействие.

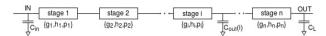

Рассмотрим цепь из n вентилей (рис. 1), где  $\mathbf{C}_{out}^i$  — ёмкость между элементами i и i+1, исполняющая роль нагрузки для элемента i и описывающаяся в терминах LE следующим образом:

$$C_{out}^{n} = C_{L}$$

$$C_{out}^{n-1} = \frac{c_{L}}{h_{rr}}$$

(6)

Рис. 1. Каскад из п вентилей

Здесь электрическая нагрузка вентиля включает в себя компоненту h, взятую из теории LE для минимальной задержки, и поправку x.

$$C_{out}^{n-1} = \frac{c_L}{h_n + x_n} \tag{7}$$

$$C_{out}^{n-2} = \frac{C_{out}^{n-1}}{h_{n-1} + x_{n-1}}$$

(8)

В общем виде  $C_{out}$  для каждого узла между вентилями рассчитывается следующим образом:

$$C_{out}^{i} = \frac{c_L}{\prod_{i+1}^{n-1}(h_i + x_i)},$$

(9)

где  $h_i$  и  $x_i$  — электрическая нагрузка и поправка для вентиля i, соответственно. Далее рассмотрим общий вид формул для задержки и потребляемой мощности в терминах методики LE.

## А. Представление мощности

Суммарная мощность для n вентилей рассчитывается следующим образом [12]:

$$P_{total} = \sum_{i=1}^{n} f \times V^2 \times C_{out}^i , \qquad (10)$$

где f — частота функционирования вентиля, а V — напряжение питания.

Подстановка  $C_{out}^i$  из (9) в (10) приводит (10) к виду:

$$P_{total} = fV^{2} \left( \sum_{i=1}^{n-1} \frac{c_{L}}{\prod_{i=1}^{n} (h_{i} + x_{i})} + C_{L} \right)$$

(11)

# В. Представление задержки

Полная задержка вентиля:

$$D_{total} = (\sum_{i=1}^{n} g_i(h_i + x_i) + \sum_{i=1}^{n} p_i)\tau$$

(12)

Выделяя из (12) часть, соответствующую выражению (2), получаем:

$$D_{total} = ((\sum_{i=1}^{n} g_i h_i + \sum_{i=1}^{n} p_i) + \sum_{i=1}^{n} (g_i x_i))\tau$$

(13)

$$D_{total} = (D_{min} + \sum_{i=1}^{n} (g_i x_i))\tau$$

(14)

С. Представление целевой функции

$$PDP = \left( fV^{2} \left( \sum_{i=1}^{n-1} \frac{c_{L}}{\prod_{i+1}^{n} (h_{i} + x_{i})} + C_{L} \right) \right) \left( D_{min} + \sum_{i=1}^{n} g_{i} x_{i} \right) \tau$$

(15)

$$PDP = \left( fV^2 \tau C_L \left( \sum_{i=1}^{n-1} \frac{1}{\prod_{i=1}^n (h_i + x_i)} + 1 \right) \right) \left( D_{min} + \sum_{i=1}^n g_i x_i \right)$$

(16)

Нормализованное значение PDP определяется как отношение абсолютного PDP исследуемой схемы к PDP базового инвертора и рассеянию мощности на нагрузке  $C_1$ , как показано в (17):

$$PDP_{normalized} = \left( \left( \sum_{i=1}^{n-1} \frac{1}{\prod_{i=1}^{n} (h_i + x_i)} + 1 \right) \right) (D_{min} + \sum_{i=1}^{n} g_i x_i)$$

(17)

### IV. Результаты моделирования

Если принять допущение, что величина поправки x одинакова для всех  $i \in \mathbb{N}: 2 \le i \le n$ , тогда целевая функция для n-ступенчатой схемы, получаемая из выражения (17), может быть представлена в следующем виле:

$$F_n(x) = \left( \left( \sum_{i=1}^{n-1} \frac{1}{\prod_{i=1}^n (h_i + x)} + 1 \right) \right) \left( D + \sum_{i=1}^n g_i x \right),$$

где  $h_i$  и  $g_i$ - параметры, связанные с i-той ступенью, n – количество ступеней в исследуемой схеме.

Построение графика и поиск минимума целевой функции на интервале выполнялись средствами среды MATLAB. Используемый для этой цели m-код отображен на рис. 2.

```

% Main function

function answ = pdpNormalized(x)

% 5 invertors chain

H = [2, 2, 2, 2, 2]; G = [1, 1, 1, 1, 1];

Dmin = 15; n = length(H); jarr = zeros(1, n - 1);

for i = 2 : n

ind = j : n; arr = H(ind) + x;

jarr(j-1) = 1/prod (arr);

end

FstBrck = sum(jarr)+1; GmXind = 1:n;

ScndBrck = Dmin + x * sum(G(GmXind));

answ = FstBrck * ScndBrck;

% Plot PDP graph

fun = @pdpNormalized;

xcoord = 0:0.01:0.6; ycoord = arrayfun(fun, xcoord);

figure; plot(xcoord, ycoord);

xlabel('x'); ylabel('PDP'); grid on;

% Minimum search

xboundary = [0, 0.6];

options =

optimset('Display','iter','PlotFcns',@optimplotfval);

[x fval] = fminbnd(fun, xboundary(1), xboundary(2), options);

grid on; x, fval

```

## Рис.2. М-код основной программы метода

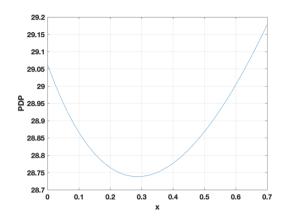

График нормализованного PDP для цепочки из пяти инверторов, полученный в результате симуляции MATLAB посредством решения уравнения (18) показан на рис. 3. Для инверторов в цепочке ширины каналов *п*-и *p*- транзисторов равны 340 нм и 280 нм, для нагрузочного инвертора — 10,88 мкм и 8,96 мкм.

Входная ёмкость прямо пропорциональна отношению ширины к длине канала транзистора. Таким образом, отношение выходной и входной ёмкостей для описанных выше примеров равно 32. В соответствии с методологией LE, оптимальная задержка достигается, ступеней когда нагрузка всех одинакова. Следовательно, минимальная задержка кажлого элемента должна быть равна 2 и 3,1748 для цепочки из трёх и пяти инверторов, соответственно. Согласно методике LE, параметр g для инвертора равен 1, тогда с учетом вышеперечисленных значений при p = 1, решение уравнения (18) в MATLAB даст значения x, равные -1,4 и 0,3, для трёх и пяти ступеней, соответственно.

Рис. 3. Зависимость величины целевой функции от величины поправки  $\boldsymbol{x}$  для цепочки из пяти инверторов

Со всеми значениями масштабированных размеров, определёнными с учетом значений x(i) и h(i), проведена симуляция средствами Cadence Spectre в базисе технологической библиотеки для технологии КМОП 28 нм. Результаты измерений характеристик, полученные для частоты входного сигнала 1  $\Gamma\Gamma$ ц, представлены в табл. 1.

Таблица 1 Результаты моделирования цепи из трёх инверторов

| Параметр        | Logical<br>Effort | Предлагаемый метод | diff, % |

|-----------------|-------------------|--------------------|---------|

| x               | 0                 | -1,4055            | -       |

| h               | 3,1748            | 1,7693             | -       |

| Задержка 01, пс | 19,42             | 20,49              | +5,5    |

| Задержка 10, пс | 19,84             | 21,39              | +7,9    |

| Мощность, мкВт  | 19,38             | 13,96              | -27,9   |

| PDP             | 376,4             | 285,9              | -24,0   |

В табл. 1 показаны значения задержки, мощности и целевой функции для цепи из трёх инверторов с использованием метода LE и предлагаемого метода. Ширины *p*- и *n*-канальных транзисторов базового инвертора составляют 340 нм и 280 нм соответственно.

Таблица 2 Результаты моделирования пяти инверторов

| Параметр        | LE    | Предлагаемый метод | diff, % |

|-----------------|-------|--------------------|---------|

| X               | 0     | 0,287              | -       |

| h               | 2     | 2,287              | -       |

| Задержка 01, пс | 23,34 | 27,54              | +17,9   |

| Задержка 10, пс | 24,34 | 28,61              | +17,5   |

| Мощность, мкВт  | 27,76 | 19,29              | -30,5   |

| PDP             | 648   | 531,4              | -17,9   |

В табл. 2 показаны значения задержки, мощности и целевой функции для цепи из пяти инверторов с использованием метода LE и предложенного метода. Ширины каналов р-МОП и п-МОП транзисторов аналогичны предыдущим. Как видно из табл. 1 и 2, предложенный метод позволил уменьшить величину PDP на 24% и 18%, по сравнению с классическим методом Logical Effort.

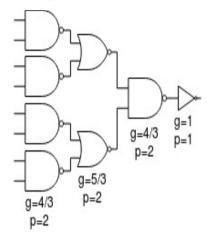

Далее предлагаемый метод был применён к схеме «8И» (рис. 4) с нагрузкой H=32. На первом этапе схема была преобразована в многоступенчатую, в соответствии с методологией LE. Затем была проведена оптимизация ширин транзисторов в соответствии с предлагаемым алгоритмом. Результаты моделирования показаны в табл. 3.

Рис. 4. Многокаскадная схема логического вентиля «8И»

Таблица 3

Результаты моделирования элемента «8И»

| Параметр             | LE    | Предлагаемый метод | diff, % |

|----------------------|-------|--------------------|---------|

| Средняя задержка, пс | 29,23 | 28,6               | -2      |

| Мощность, мкВт       | 43,22 | 33,79              | -21     |

| PDP                  | 1263  | 967                | -23     |

Также алгоритм был применён для однобитного сумматора (табл. 4). В качестве нагрузки был использован инвертор с ширинами каналов, равными 2,72 мкм и 2,24 мкм для *n*- и *p*-канальных транзисторов, соответственно, значение электрической нагрузки H=8.

Таблица 4

Результаты моделирования однобитного сумматора

| Параметр        | LE    | Предлагаемый метод | diff, % |

|-----------------|-------|--------------------|---------|

| Задержка 01, пс | 21,25 | 23,04              | +8      |

| Задержка 10, пс | 18,52 | 20,59              | +11     |

| Мощность, мкВт  | 54,31 | 36,29              | -33     |

| PDP             | 818,8 | 690,4              | -15     |

### ЗАКЛЮЧЕНИЕ

В работе предлагается методика определения размеров вентилей средствами оптимизации MATLAB на основе модификации методики Logical Effort, для уменьшения величины PDP в статической логической КМОП-схеме. Целью работы была демонстрация метода, эффективности предложенного заключающегося в том. что переопределением ступеней может электрической нагрузки быть уменьшена потребляемая мощность с увеличением задержки переключения. Показан способ минимизации PDP. В терминах PDP и мощности было достигнуто улучшение. Снижение мощности на 28% и 30%, PDP на 24% и 18% для 3 и 5 элементов наблюдалось при возрастании задержки на 6,7% и 17% соответственно. Для схемы однобитного сумматора предложенная модель продемонстрировала уменьшение мощности на 33% и PDP на 15% с увеличением средней задержки на 9%.

#### Поддержка

Статья подготовлена в рамках госзадания МИЭТ (тема 0719-2020-0017/FSMR-2020-0017).

#### Литература

- [1] Красников Г.Я. Конструктивно-технологические особенности субмикронных МОП-транзисторов / В 2-х частях // Москва, 2004. Ч. 2. 536 с.

- [2] Красников Г.Я., Зайцев Н.А., Красников А.Г. Современное состояние разработок в области энергонезависимой памяти // Нано-и микросистемная техника, 2015. №4 (177). С. 60-64.

- [3] Sutherland I., Sproull B., Harris D. Logical Effort: Design Fast CMOS Circuits // Morgan Kaufmann publishers, 1999. 256p.

- [4] Frustaci F., Alioto M., Corsonello P. Tapered-Vth Approach for Energy-Efficient CMOS Buffers // IEEE Transactions on circuits and systems-I, 2011. Vol 58, Is. 11, pp. 1-10.

- [5] Gao F., Hayes J.P. Total Power Reduction in CMOS Circuits via Gate Sizing and Multiple Threshold Voltages // DAC-2005. PP.31-36.

- [6] Penzes P., Nystrom M., Martin A. J. Transistor sizing of energy-delay-efficient circuits // Timing Issues in the Specification and Synthesis of Digital Systems (TAU), 2002. PP. 126–133.

- [7] Alioto M., Consoli E., Palumbo G. Metrics and Design Considerations on the Energy-Delay Tradeoff of Digital Circuits // IEEE International Symposium on Circuits and Systems, 2009. PP. 3150 - 3153.

- [8] Dao H.Q., Zeydel B.R., Oklobdzija V.G. Energy minimization method for optimal energy-delay extraction // Proceedings of IEEE Solid-State Circuits Conference, 2003. PP. 177–180.

- [9] Ильин С.А., Коршунов А.В., Гарбулина Т.В. Сравнительный анализ энергоэффективности библиотек по технологии FinFET 7 нм // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2020. Выпуск 4. С. 169-173. doi:10.31114/2078-7707-2020-4-169-173

- [10] Ильин С. А., Копейкин Д. Ю., Ласточкин О. В., Шипицин Д. С. Сравнительный анализ параметров стандартных цифровых элементов на примере библиотек в базисе технологии КМОП 28 нм // Наноиндустрия, 2020. Т. 13. №S4(99). С. 268- 271.

- [11] Ilin S.A., Korshunov A.V., Ryzhova D.I. Comparative Analysis of Standard Cells Performance for 7nm FinFET and

28nm CMOS Technologies with Considering for Parasitic Elements» // Proceeding of 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), 2018. PP. 1360-1363.

[12] Ilin S.A., Korshunov A.V. The Technique of Fast Power Analysis for FinFET Standard Cells // Proceeding of 2018 IEEE East-West Design & Test Symposium (EWDTS), 2018. PP. 1-5.

# Optimization of Standard Cells Power Consumption: Logical Effort Based Algorithm

M.A. Zapletina<sup>1,2</sup>, S.A. Ilyin<sup>1,3</sup>, O.V. Lastochkin<sup>3</sup>

<sup>1</sup>NRU Moscow Institute of Electronic Technology,

<sup>2</sup>Institute for Design Problems in Microelectronics RAS (IPPM RAS),

<sup>3</sup>JSC Research Institute of Molecular Electronics, Zelenograd, Moscow, silin@mikron.ru

Abstract — Latency and power consumption are the key controlled characteristics in a digital design flow for standard cells. The paper proposes a method that uses the Power-Delay Product (PDP) as an objective function. A mathematical model is built to minimize PDP by scaling the gates sizes. The results are obtained for the CMOS 28 nm technology on the example of a net of three and five inverters, a combinational circuit and a one-bit adder circuit. Both parts of the objective function were presented in terms of the Logical Effort methodology. The search for the minimum of the objective function was performed. The proposed solution is based on the assumption that the correction value is identical for all circuit gates. The proposed method is used to simplify solving the optimization equation and to give an acceptable result in comparison with traditional scaling methods with a focus on the performance.

The main aim of the work is to show that redefining the electrical load of the gates makes possible to reduce the power consumption with an increase in the delay. An achieved decrease in power was 28% and 30%, PDP decrease was 24% and 18% for 3 and 5 gates length circuits with an increase in delay of 6.7% and 17%, respectively. For a single-bit adder circuit, the proposed model demonstrated a 33% reduction in power and 15% in PDP with a 9% increase in average latency.

**Keywords** — Power Delay Product, Logical Effort, Standard Cell Library, Optimization.

### REFERENCES

- [1] Krasnikov G. Ya. Konstructivno-technologicheskie osobennosti submikronnikh MOP-tranzistorov (Design and technological features of submicron MOS transistors) / v 2kh chastyakh // Moscow, 2004. P.2. 536 p.

- [2] Krasnikov G.Ya, Zaytsev N.A., Krasnikov A.G. Sovremennoye sostoyaniye razrabotok v oblasti energonezavisimoy pamyati // Nano-i mikrosistemnaya tekhnik(The current state of developments in the field of nonvolatile memory) // Nano- and microsystem technology 2015.No4(177). C. 60-64.

- [3] Sutherland I., Sproull B., Harris D. Logical Effort: Design Fast CMOS Circuits // Morgan Kaufmann, 1999. 256 p.

- [4] Frustaci F., Alioto M., Corsonello P. Tapered-Vth Approach for Energy-Efficient CMOS Buffers // IEEE Transactions on circuits and systems-I, 2011. Vol 58, Is. 11, pp. 1-10.

- [5] Gao F., Hayes J.P. Total Power Reduction in CMOS Circuits via Gate Sizing and Multiple Threshold Voltages // DAC, 2005. PP.31-36.

- [6] Penzes P., Nystrom M., Martin A. J. Transistor sizing of energy-delay-efficient circuits // Timing Issues in the Specification and Synthesis of Digital Systems (TAU), 2002. PP. 126–133.

- [7] Alioto M., Consoli E., Palumbo G. Metrics and Design Considerations on the Energy-Delay Tradeoff of Digital Circuits // IEEE International Symposium on Circuits and Systems, 2009. PP. 3150 - 3153.

- [8] Dao H.Q., Zeydel B.R., Oklobdzija V.G. Energy minimization method for optimal energy-delay extraction // Proceedings of IEEE Solid-State Circuits Conference, 2003. PP. 177–180.

- [9] Ilin S.A., Korshunov A.V., Garbulina T.V. Benchmarking Energy Efficiency of Libraries on FinFET 7nm // Problems of Perspective Micro- and Nanoelectronic Systems Development - 2020. Issue 4. P. 169-173. doi:10.31114/2078-7707-2020-4-169-173

- [10] Ilin S.A., Lastochkin O.V., Novikov A.A., Shipitsin D.S. Sravnitel'nyy analiz bibliotek po tekhnologii CMOS 28 nm (Comparative analysis of libraries by CMOS 28 nm technology) // Nanoindustriya, 2020. Vol. 13. №S4(99). PP. 268-271

- [11] Ilin S.A., Korshunov A.V., Ryzhova D.I. Comparative Analysis of Standard Cells Performance for 7nm FinFET and 28nm CMOS Technologies with Considering for Parasitic Elements // Proceeding of 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), 2018. PP. 1360-1363.

- [12] Ilin S.A., Korshunov A.V. The Technique of Fast Power Analysis for FinFET Standard Cells // Proceeding of 2018 IEEE East-West Design & Test Symposium (EWDTS), 2018. PP. 1-5.