# Расширение возможностей SPICE-подобных программ за счет учета эффектов старения в МОП схемах, обусловленных эффектами горячих носителей, пробоя диэлектрика и электромиграции

# И.А. Харитонов

Национальный исследовательский университет «Высшая школа экономики» (Московский институт электроники и математики), г. Москва, ikharitonov@hse.ru

Аннотация — Описаны дополнения к стандартным SPICE моделям МОП элементов схем, учитывающие эффекты их старения, обусловленные влиянием горячих носителей, пробоя диэлектрика и электромиграции. Наборы таких моделей вместе со средствами определения их параметров и средствами SPICE моделирования объединены в подсистему SPICE моделирования КМОП схем с учетом факторов старения и оценки параметров надежности и времени бессбойной работы. Приведены примеры моделирования характеристик аналоговых и цифровых фрагментов КМОП схем с учетом указанных эффектов старения.

Ключевые слова — КМОП схемы, эффекты старения, горячие носители, NBTI, PBTI, HCI, TDDD, электромиграция, надежность, время бессбойной работы, SPICE модели, эквивалентные схемы, схемотехническое моделирование, аналоговые схемы, цифровые схемы

#### I. Введение

Хорошо известно, что процесс уменьшения размеров МОП транзисторов и проводников БИС сопровождается увеличением электрических полей в структурах МОПТ и плотностей токов в проводниках. Увеличение электрических полей в МОПТ приводит к усилению эффектов «горячих» носителей внутри структур транзисторов, изменяющих параметры МОПТ со временем, т.е. к «старению» МОПТ и схем.

Традиционно выделяют следующие эффекты в МОПТ, приводящие к их «старению»:

- генерация «горячих» электронов и дырок («hot carriers», HC, «hot carriers injection», HCI) в канале транзистора у стокового перехода при достижении горизонтальным электрическим полем в канале значений, необходимых для ионизации носителей (электронов в п-МОП или дырок в р-МОП);

- генерация «горячих» носителей из-за температурной нестабильности вследствие отрицательного смещения («Negative Bias Temperature Instability», NBTI) в р-канальных МОПТ или положительного смещения («Positive Bias Temperature Instability», PBTI) в п-канальных МОПТ в подзатворном

- диэлектрике под действием *вертикального* поля затвора;

- эффекты пробоя подзатворного диэлектрика со временем («Time Dependent Dielectric Breakdown», TDDB). При этом выделяют «мягкий» (soft, при котором ток через затвор растет плавно или увеличивается до конкретной величины и дальше не растет) и «жесткий» (hard, когда ток через затвор растет скачкообразно и достигает достаточно больших величин).

Возникшие при описанных выше процессах высокоэнергетичные носители заряда попадают в подзатворный диэлектрик и на границу раздела «диэлектрик затвора - полупроводник», формируя поверхностные состояния  $\Delta N_{it\_stress}(t)$  на границе раздела «диэлектрик-полупроводник», зависящие от времени и влияющие на пороговое напряжение, уменьшающие подвижность носителей в канале и приводящие к уменьшению наклона предпороговой сток-затворной ВАХ и , как результат, спаду максимального тока стока транзистора ([2], [4] и др.).

Эффекты, связанные с пробоем диэлектрика, приводят к возникновению токов утечки через подзатворный диэлектрик и также к последующему сдвигу порогового напряжения и спаду крутизны МОПТ ([3], [19] и др.) за счет наведенных при пробое поверхностных состояний в подзатворном диэлектрике.

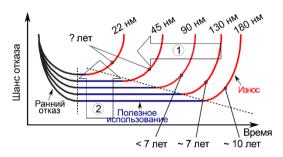

Использование многослойных подзатворных диэлектриков (с высокой диэлектрической проницаемостью) в глубоко субмикронных (проектные нормы менее 45 нм) МОП транзисторах с переходными (дефектными) областями между слоями с одной стороны увеличивает физическую толщину изолятора, с другой стороны, снижает электрическую прочность подзатворного диэлектрика и повышает вероятность туннелирования через него и развития пробоя ([2], [9], [10] и др.). При этом, хотя вероятность пробоя отдельного транзистора обычно пренебрежимо мала, вероятностью пробоя в схемах, содержащих миллиарды транзисторов, вероятностью пробоя уже пренебрегать нельзя для типового срока службы схемы 10 лет ([1], [3], [9], [6] и др.).

Уменьшение сечений проводников БИС приводит к усилению эффектов электромиграции в них, утончению проводников, росту их сопротивления и даже к обрыву ([2], [31] и др.).

Специалисты-проектировщики интегральных схем и электронных устройств понимают, что деградация устройства вследствие «горячих» носителей и других механизмов старения становится ограничивающим фактором при масштабировании ИС и серьезной проблемой для современных систем с нанометровыми размерами транзисторов ([1], [2] и др.). Оценка надежности схем до изготовления становится важным этапом в процессе проектирования схем. Появился даже термин «Проектирование обеспечения для надежности» (Design for reliability). Количество работ, посвященных исследованию и вопросам моделирования эффектов старения в КМОП транзисторах и схемах при различных проектных нормах, весьма велико и продолжает увеличиваться при переходе к меньшим проектным нормам.

Рис. 1. Уменьшение времени работы КМОП схем при масштабировании их размеров ([3])

Одними из первых пакетов SPICE моделирования схем с учетом эффектов старения, были: BERT, RELY и др. Подходы и маршруты, заложенные в этих пакетах, были затем использованы в ряде коммерческих SPICE симуляторов крупных компаний: Cadence Spectre/UltraSim, Mentor Graphics Eldo, Synopsys MOSRA и др. Затем появились и более новые пакеты моделирования схем с учетом эффектов старения ([4], [5][13], и др.)

Однако, несмотря на большое количество работ по исследованию и моделированию эффектов старения в КМОП схемах, можно сказать, что отечественные проектировщики КМОП схем редко проводят анализ влияния эффектов старения на работу и надежность схем. В числе прочих, это можно объяснить следующими факторами:

- 1) большим объемом имеющейся информации по этим вопросам,

- 2) использованием в статьях повышенных напряжений и температур (для ускорения процесса тестирования) для исследования эффектов горячих носителей и пробоя диэлектрика в МОПТ и связанной с этим необходимостью пересчета параметров деградации МОПТ из более «жестких» условий тестирования в параметры для нормального режима работы,

- 3) недостаточно подробным описанием используемых моделей старения в системах проектирования схем, где эти модели присутствуют

- 4) практически отсутствием готовых наборов SPICE моделей компонентов схем с учетом эффектов старения для различных проектных норм, факторов старения и режимов работы.

Все это говорит об актуальности создания наборов SPICE моделей КМОП транзисторов с учетом эффектов старения с различными проектными нормами для расширения возможностей широко используемых систем SPICE моделирования схем.

# II. ПОДСИСТЕМА SPICE МОДЕЛИРОВАНИЯ ХАРАКТЕРИСТИК КМОП СХЕМ С УЧЕТОМ ЭФФЕКТОВ СТАРЕНИЯ

В результате проведенной нами работы по анализу и обработке большого количества (литературных) данных по деградации и моделированию характеристик МОП транзисторов со временем, вызванной эффектами «горячих» носителей, пробоя диэлектрика, электро-миграции в проводниках, при уменьшении минимальных размеров транзисторов от единиц микрометров до десятков нанометров, сформирована подсистема схемотехнического моделирования характеристик МОП схем, с учетом упомянутых эффектов.

Ранее нами была отработана и описана SPICE модель КМОПТ для учета эффектов NBTI и HCI [12]. В модели был использован применяемый нами подход, при котором параметры модели МОПТ зависят от плотностей наведенных в подзатворном окисле заряда носителей  $\Delta$ Not(t) и поверхностных состояний на границе раздела изолятор-кремний  $\Delta$ Nit(t). Это дало возможность свести в одну модель эффекты NBTI, HC и радиации [11].

В данной работе модель доработана и дополнительно учитывает эффекты пробоя подзатворного диэлектрика. Обобщённая SPICE макромодель МОПТ для учета эффектов PBTI, HCI, TDDB приведена настроена для различных проектных норм – от долей микрометров до десятков нанометров.

В результате разработана подсистема учета факторов старения, включающая:

- набор схемотехнических макромоделей МОПТ на базе стандартных моделей, в которых учтены эффекты старения КМОП схем: вследствие «горячих» носителей (NBTI, PBTI, HCI), процессов пробоя подзатворного диэлектрика (TDDB), электромиграции;

- пакет SPICE моделирования с включенными моделями МОПТ с учетом эффектов старения;

- набор специальных скриптов, обеспечивающих расчет основных параметров SPICE моделей МОПТ, учитывающих факторы старения, в зависимости от параметров структуры транзистора, величины и продолжительности электрического стресса, условий окружающей среды, используя

имеющиеся литературные или экспериментально полученные данные по деградации МОПТ под действием стресса;

набор скриптов, обеспечивающих расчет времени работы МОП транзистора до наступления пробоя диэлектрика и времени работы до сбоя схемы за счет эффектов электромиграции;

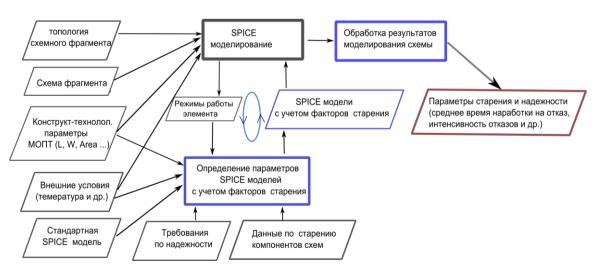

Сам процесс SPICE моделирования работы схем с учетом эффектов старения, как и в других работах, состоит из нескольких этапов (см. рис. 2):

1. Анализ работы схемы в рабочем режиме в течение определенного количества тактов работы схемы. Определение степени проявления эффектов HCI, BTI, TDDB за этот период. Расчет коэффициентов деградации для каждого вида эффектов с учетом электрического режима, температуры и др.

Для учета эффектов электромиграции во время первого этапа SPICE моделирования оцениваются токи потребления схем.

- 2. Корректировка параметров SPICE моделей МОПТ с учетом полученных на предыдущем этапе коэффициентов деградации по каждому фактору старения и моделирование работы схемы через продолжительное время работы.

- 3. Определение времени наработки схемы на отказ по каждому из факторов старения по критерию выхода критического параметра схемы (коэффициента усиления, времени задержки, сопротивления и др.) за допустимые пределы. Определение результирующего времени наработки схемы на отказ и вероятности бессбойной работы.

Для основного МОП транзистора макромодели ([11], [12]) основные параметры его SPICE модели: пороговое напряжение (Vth), подвижность (Uo), коэффициент, описывающий предпороговый наклон сток-затворных BAX (nfactor) зависят от накопленных в подзатворном диэлектрике плотностей зарядов  $\Delta$ Not(t) и на

границе кремний-диэлектрик поверхностных состояний  $\Delta \mathrm{Nit}(t)$ , которые, в свою очередь, зависят от времени стресса (работы схемы) tstress, электрического режима работы МОПТ и условий окружающей среды. Указанные значения плотностей зарядов пересчитываются через традиционно рассчитываемые сдвиги порогового напряжения в зависимости от времени работы/стресса (tstress) (для удобства обработки литературных данных):

$$V_{th}(t_{stress}) = V_{th_{-0}} + \Delta V_{th_{-}PBTI}(t_{stress}) + + \Delta V_{th_{-}HCI}(t_{stress}) + \Delta V_{th_{-}TDDR}(t_{BreakDown}),$$

(1)

$$Uo(t_{stress}) = \frac{Uo_0}{1 + \alpha \cdot (N_{ii\_PBTI}(t_{stress}) + N_{ii\_HCI}(t_{stress}) + N_{ii\_TDDB}(T_{BreakDown}))},$$

(2)

где  $V_{th0}$  — пороговое напряжение транзистора в начале работы;

$\Delta V_{th\_PBTI}$ ,  $\Delta V_{th\_HCI,}$ ,  $\Delta V_{th\_TDDB}$ — сдвиги порогового напряжения МОПТ, вызванные, соответственно, эффектами РВТІ, HCI, TDDB;

$t_{sress}$  — время нахождения МОПТ под действием данного вида стресса,

Для описания упомянутых выше сдвигов пороговых напряжений  $\Delta V th(t)$  вследствие эффектов старения нами используются скорректированные и настроенные на конкретные проектные нормы зависимости для учета данного вида эффектов, основанные на достаточно распространенных выражениях, приведенных ниже.

Для учета эффектов NBTI используются зависимости из [17], [7] и др. работ:

$$\Delta V_{th}(t_{stress}) = (K_{v} \cdot t_{stress}^{0.5})^{2n}, \qquad (3)$$

Рис. 2 Маршрут моделирования работы схем с учетом эффектов старения

$$K_{v} = \left(\frac{q}{C_{ox}}\right)^{3} \cdot K^{2} \cdot C_{ox} \cdot (V_{gs0} - V_{th}) \cdot \sqrt{C} \cdot \exp\left(\frac{2 \cdot E_{ox}}{E_{0}}\right) \times \left(1 - \frac{V_{ds}}{\alpha_{NBTI}(V_{gs} - V_{th})}\right), \tag{4}$$

$$C = T_0 \cdot \exp\left(\frac{-E_{a\_NBTI}}{kT}\right),\tag{5}$$

где:  $t_{stress}$  — время работы схемы;

K,  $E_0$  – подгоночные коэффициенты;

n — показатель степени зависимости от времени,

$V_{th0}$  – пороговое напряжение МОПТ до начала его работы;

$E_{ox}$  – поле в подзатворном окисле;

$E_{a\ HCI}$  – энергия активации физического процесса NBTI;

k — постоянная Больцмана;

Для учета эффектов HCI в качестве основы выражений используются зависимости из [5], [8] и др.:

$$\Delta V_{th}(t_{stress}) = A_1 \cdot \left( \left( V_{gs} - V_{th0} \right) \cdot K_v \right)^{\frac{n_x}{1 + n_x}} \cdot \left( \frac{I_{ds}}{W} \right)^{K_I} \cdot \left( \frac{n_x}{l} \cdot t_{stress} \right)^{\frac{1}{1 + n_x}}, \tag{6}$$

$$K_{v} = \exp\left(\frac{E_{ax}}{E_{0}}\right) \cdot \exp\left(\frac{-\varphi_{it}}{q \cdot \lambda \cdot E_{m}}\right) \cdot \exp\left(\frac{-E_{a}}{k \cdot T}\right), \tag{7}$$

$$E_m = \frac{V_{ds} - V_{ds\_sat}}{l}, \qquad (8)$$

где:  $A_I$ ,  $K_I$ ,  $\lambda$  – подгоночные коэффициенты;

$n_x$  – коэффициент модели, по умолчанию, 1.21;

l — длина канала транзистора;

$\phi_{it}$  – минимальная энергия ударной ионизации, 3.7 эВ;

$V_{ds\ sat}$  напряжение сток-исток насыщения.

Дополнительные сопротивления Rgs, Rgd макромодели между затвором и, соответственно, истоком и стоком, описывают токи утечки через затвор МОПТ после наступления пробоя диэлектрика. Их величины зависят от степени пробоя диэлектрика и места расположения точки пробоя в канале транзистора ([19] и др.). В областях, близких к стоку или истоку, сопротивления меньше, ток затвора больше, чувствительность схемы к эффектам пробоя диэлектрика больше.

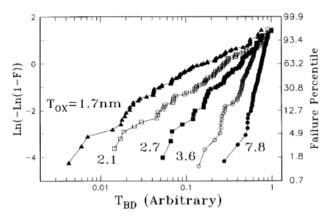

При оценке времени работы МОПТ до пробоя подзатворного диэлектрика за счет коэффициента F учитывается расширение кривой распределения вероятности пробоя от времени при уменьшении толщины диэлектрика (см. рис. 3).

При оценке влияния эффектов электромиграции время безопасной работы оценивается в соответствии с общепринятыми критериями, учитывающими

вероятностный характер этого процесса: увеличением сопротивления проводника на 10% для 0.1% межсоединений при заданной температуре [20]:

Рис. 3. Пример изменение ширины нормализованного распределения вероятности пробоев диэлектрика от времени работы схемы при уменьшении толщин подзатворного изолятора от 7,8 нм до 1,7 нм (данные работы [10] и др. работ)

$$t_{50} = \frac{A_2}{j^n} \cdot \exp\left(\frac{E_{a_-em}}{k \cdot T}\right) \cdot F, \qquad (9)$$

где  $t_{50}$  – время работы до наступления вышеописанных критериев с вероятностью 50%;

$A_2$  – подгоночный коэффициент;

n – степень зависимости от плотности тока (~2)

j — плотность тока через проводник;

$E_{a\_HCI}$  – энергия активации физического процесса электромиграции,

F — коэффициент, учитывающий ширину нормализованного распределения вероятности пробоев диэлектрика от времени работы схемы (аналогично рис. 3).

После расчета времен наработки схемы на отказ по каждому из факторов старения рассчитывается результирующее время работы до сбоев и частоты сбоев схемы по стандартным выражениям.

## III. ПРИМЕРЫ МОДЕЛИРОВАНИЯ ХАРАКТЕРИСТИК КМОП СХЕМ С УЧЕТОМ ЭФФЕКТОВ СТАРЕНИЯ

## А. Аналоговые КМОП схемы

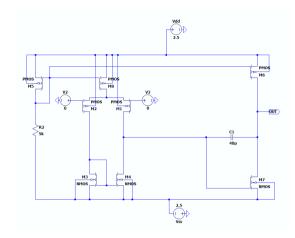

В качестве примеров моделирования аналоговых схем мы приводим ниже результаты моделирования характеристик типовых 2-х каскадных КМОП операционных усилителей (ОУ) при уменьшении проектных норм от 180 нм до 28 нм с учетом факторов NBTI, PBTI и TDDB. Схема ОУ для 180 нм представлена на рис. 4. Поскольку в схемах ОУ обычно используются МОПТ с размерами длин канала, большими минимальных проектных норм примерно в 5 раз (с целью уменьшения эффектов горячих носителей в стоковом переходе), то

эффекты HCI в стоковом переходе, для используемых схем ОУ, сказываются незначительно.

Рис. 4. Схема 2-х каскадного КМОП ОУ (для 180 нм)

Деградация параметров и характеристик ОУ с проектными нормами 180, 90, 45 и 28 нм проводилась в предположении года его непрерывной работы на синусоидальном сигнале с размахом выходного сигнала, близким к напряжению питания.

Результаты нашего моделирования и данные других работ ([14], [16] и др.) показали, что наибольшее влияние на деградацию параметров ОУ со временем оказывает увеличение напряжения смещения нуля, вызванное разбалансом сдвигов пороговых напряжений транзисторов М1 и М2 входного дифференциального каскада из-за эффектов NBTI. Это связано с тем, что они работают при различных напряжениях на стоках, соответственно, деградируют в разной степени (М2 деградирует сильнее).

При масштабировании размеров транзисторов проявление эффектов NBTI и PBTI становится меньше, (при условии неизменных физических свойств подзатворного диэлектрика) ([7] и др.). При этом для моделируемых схем ОУ поле в подзатворном диэлектрике остается примерно одинаковым, рабочие напряжения в схемах снижаются, поэтому абсолютная величина сдвига порогового напряжения и его разбаланса уменьшается с уменьшением размеров транзисторов. Это

приводит к незначительному уменьшению абсолютного значения напряжения смещения нуля ОУ при уменьшении размеров МОПТ (см. табл. 1). Предполагая, что схема ОУ используется в составе 10-разрядного ЦАП с требованиями по напряжению смещения нуля не более 75% от Епит/210 (для младшего разряда), можно рассчитать время работы схемы ОУ ([10]) до достижения допустимого сдвига нуля (см. табл. 1). В этом случае получается максимальный разбаланс пороговых напряжений входных транзисторов, т.к. на базе одного транзистора – входное напряжение, а на базе другого – опорное напряжение.

При уменьшении размеров транзисторов ОУ уменьшаются толщины подзатворного окисла, площади транзисторов, расширяется кривая распределения вероятности пробоя от времени (рис. 3). Эти факторы в сумме приводят к уменьшению времени работы схемы ОУ до пробоя диэлектрика tTDDB (для 5% вероятности пробоя) для меньших проектных норм (см. табл. 1).

Величина, обратная к времени бессбойной работы (time to failure) схемы ОУ с учетом нескольких факторов старения (см. табл. 1) считается по стандартным выражениям, как сумма величин, обратных к временам бессбойной работы по каждому из факторов. Из табл. 1 видно, что неучет фактора пробоя диэлектрика для размеров 45 и 28 нм в работах [14], [15], [16], где анализировалось только влияние эффектов NBTI и HCI на работу схем ОУ, приводит к заметной погрешности оценки возможного результирующего времени бессбойной работы ОУ.

Полученные результаты моделирования хорошо согласуются с имеющимися работами по моделированию характеристик КМОП ОУ с различными проектными нормами с учетом факторов старения ([9], [10], [13], [14]).

Поскольку данные схемы ОУ работают при малых потребляемых токах, то эффектами электромиграции в проводниках схемы можно в данном случае пренебречь.

# В. Цифровые КМОП схемы

В качестве иллюстрации использования моделей КМОПТ с учетом факторов старения для цифровых схем ниже на рис. 5 приведены результаты SPICE

Таблица 1 Смоделированное изменение параметров КМОП ОУ при уменьшении проектных норм транзисторов (через год непрерывной работы)

| Проект.<br>норма,<br>нм | Т <sub>ох</sub> ,<br>нм | Епит, В     | Изменен. напряжен.<br>смещ. нуля вследст.<br>эфф. NBTI, PBTI,<br>HCI через год , мВ | Изменен. напряж. смещ. нуля в $\%$ от $E_{\text{пит}}$ | Время работы до допусти-<br>мого смеще-<br>ния нуля, сек | Время работы до наступл пробоя $t_{TDDB}$ (5%), сек | Результ.<br>время безот-<br>каз. работы,<br>сек |

|-------------------------|-------------------------|-------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|

| 180                     | 4                       | ±2.5        | 1.4                                                                                 | 0.025                                                  | 1.2*108                                                  | 1.9*10 <sup>9</sup>                                 | 1.1*108                                         |

| 90                      | 2                       | ±1.2        | 1.2                                                                                 | 0.05                                                   | $7.6*10^7$                                               | 1.6*10 <sup>9</sup>                                 | $7.4*10^7$                                      |

| 45                      | 1.7                     | ±1.0        | 1.0                                                                                 | 0.052                                                  | $6.8*10^7$                                               | 1.3*109                                             | $6.5*10^7$                                      |

| 28                      | 1.5                     | $\pm 0.9/0$ | 0.85                                                                                | 0.063                                                  | $6.1*10^7$                                               | 1.1*109                                             | $5.8*10^7$                                      |

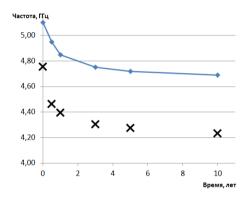

моделирования изменения частоты генерации кольцевого генератора (КГ) из 13 КМОП инверторов с L=65 нм ширинами каналов 150 нм для n-МОП и 200 нм для p-МОП, 1В питанием, в зависимости от времени его работы при температуре 300К с учетом эффектов NВТІ, PВТІ, HCІ.

Из рис. 7 видно, что результаты моделирования по деградации частоты генерации КГ хорошо согласуются с результатами работ ([6], [17], [18] и др.). Незначительное различие в измеренных и смоделированных частотах можно объяснить различиями в используемых SPICE моделях МОПТ: нами использовались модели с сайта http://ptm.asu.edu.

Для примера оценки времени работы схемы с учетом эффектов электромиграции в ее проводниках питания нами моделировалась схема аналогичного КГ с уменьшенными проектными нормами 28 нм. В этом случае, учитывая проектные нормы 28 нм, период колебаний 200 пс (аналогично работе [20]), средний потребляемый ток 35 мкА, ширину проводников для данных проектных норм, получаем время работы, ограниченное электромиграцией, около 15 лет. Это время достаточно близко к оценкам времени работы из работы [20] для аналогичной схемы КГ с аналогичными проектными нормами.

Рис. 5. Смоделированное по нашим моделям (линии) и измеренное в работе [18] (крестики) изменение частоты кольцевого генератора из 13 КМОП инверторов с L=65 нм в зависимости от времени его работы с учетом эффектов NBTI, PBTI, HCI

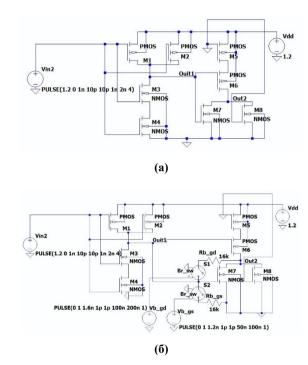

Моделирования влияния эффектов пробоя подзатворного диэлектрика МОПТ на характеристики цифровых КМОП схем проиллюстрировано на рис. 6 (а), где приведена схема из элементов 2И-НЕ и 2ИЛИ-НЕ, а на рис. 6 (б) - эта же схема с учетом эффектов «мягкого» пробоя диэлектрика в транзисторе М7. Проектные нормы 45 нм, длины каналов n- и p-канальных МОПТ также по 45 нм (аналогично работе [19]).

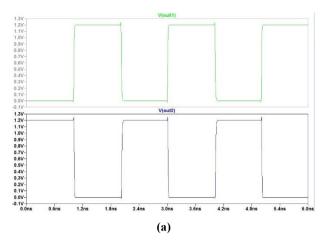

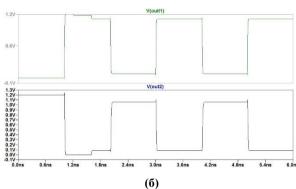

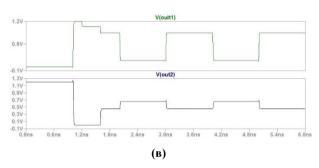

На рис. 7 приведены смоделированные переходные характеристики исходной схемы, (а) и этой же схемы при сопротивлениях пробоя через диэлектрик 30 кОм («мягкий» пробой в районе центральной части канала МОПТ), (б) и 16 кОм («мягкий» пробой в районе канала около стока или истока МОПТ, [19]), (в). Использованы данные по пробою диэлектрика из работы [19].

Видно, что при сопротивлении пробоя порядка 30 кОм схема остается работоспособной, а при сопротивлении пробоя порядка 16 кОм работоспособность схемы нарушается.

Рис. 6. Исходная схема из элементов 2И-НЕ и 2ИЛИ-НЕ (а) и вариант этой же схемы с учетом эффектов пробоя диэлектрика в транзисторе М7 (б)

#### IV. Выводы

- 1. В отечественную САПР, базирующуюся на SPICE-подобных платформах, встроена модель МОП транзистора, учитывающая эффекты старения МОПТ, вызванные следующими механизмами: влиянием «горячих» носителей (NBTI, PBTI, HCI), процессов пробоя подзатворного диэлектрика (TDDB), электромиграции.

- 2. Разработана и реализована на практике процедура расчета времени бессбойной работы (*time to failure*) аналоговых и цифровых КМОП схем.

- 3. На конкретных примерах КМОП ИС проведено сравнение полученных результатов расчета параметров старения с данными известных зарубежных работ. Показано, что для аналоговых КМОП схем с размерами элементов 45, 28 нм неучет (в ряде зарубежных работ) эффектов пробоя подзатворного диэлектрика может приводить к заметным погрешностям в оценках времени бессбойной работы КМОП схем приводить к переоценке времени бессбойной работы КМОП ИС.

- 4. Для цифровых КМОП схем показано существенное влияние на характеристики схем местонахождения точки пробоя внутри канала МОПТ.

# Поддержка

Данная работа выполнена при финансовой поддержке РФФИ в рамках гранта № 20-57-53004.

Рис. 7. Смоделированные переходные характеристики исходной схемы (рисунок 6,а) (а) и этой же схемы при сопротивлениях пробоя через диэлектрик 30 кОм (рисунок 6,б) (б) и 16 кОм (в)

# Литература

- [1]. B. Bailey. Chip Aging Becomes Design Problem // Semiconductor Engineering, August 9th, 2018. https://semiengineering.com/chip-aging-becomes-design-problem. (accessed 05.06.2021).

- [2]. T. Mak. Is CMOS More Reliable with Scaling? // Proceedings of the Online Testing Workshop, 2002.

- [3]. Natalia RUIZ. Multilevel aging phenomena analysis in complex ultimate CMOS designs // Thèse pour obtenir le grade de Docteur de L'université De Grenoble. 2012.

- [4]. Pfost, J. Joos, M. Stecher. Compact Modeling and Simulation for Digital Circuit Aging. // Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy. Arizona state university, 2012.

- [5]. E. Maricau, P. De Wit, G. Gielen. An analytical model for hot carrier degradation in nanoscale CMOS suitable for the simulation of degradation in analog IC applications // Microelectronics Reliability, 2008, 48. Pp. 1576-1580.

- [6]. Wenping Wang, Vijay Reddy, Anand T. Krishnan, Rakesh Vattikonda, Srikanth Krishnan, and Yu Cao, Compact Modeling and Simulation of Circuit Reliability for 65-nm CMOS Technology// IEEE Trans On Device And Mater. Reliability, VOL. 7, NO. 4, December 2007, p. 509.

- [7]. R. Vattikonda, Wenping Wang and Yu Cao, "Modeling and minimization of PMOS NBTI effect for robust nanometer design," // Proc of. 43rd ACM/IEEE Design Automation Conference, 2006, pp. 1047-1052.

- [8]. W. Wang, V. Reddy, An.T. Krishnan, R. Vattikonda, Srikanth Krishnan, Yu Cao. An Integrated Modeling Paradigm of Circuit Reliability for 65nm CMOS Technology// Proc. of IEEE 2007 Custom Intergrated Circuits Conference (CICC), 2007, pp.511-516.

- [9]. A. Avellán and W. H. Krautschneider. Impact of Soft and Hard Breakdown on Analog and Digital Circuits // IEEE Trans. on Device and Materials Reliability, vol. 4, No. 4, 2004, pp. 677-683.

- [10]. Neeraj K. Jha, P. Sahajananda Reddy, Dinesh K. Sharma, NBTI Degradation and Its Impact for Analog Circuit Reliability// IEEE Trans. on Electron Devices, Vol. 52, N. 12, 2005, pp,2609-2616.

- [11].Petrosyants K.O., Kharitonov I.A. SPICE Simulation of Total Dose and Aging Effects in MOSFET Circuits// Proc. of IEEE East-West Design and Test Simp., 2018, pp. 760-.

- [12]. И.А. Харитонов, SPICE модели МОПТ, учитывающие эффекты старения // Наноиндустрия. Специальный выпуск. 96, 2020. С. 300-307.

- [13]. Tan, Weidong Liu, Frank Lee. An accurate MOSFET aging model for 28 nm integrated circuit simulation // Microelectronics Reliability, 52 . 2012. Pp. 1565–1570.

- [14].R. Thewes et al., Device reliability in analog CMOS applications // Intern. Electron Devices. Meeting 1999. Technical Digest (Cat. No.99CH36318), 1999, pp. 81-84.

- [15].M. Agostinelli, S. Lau, S. Pae, P. Marzolf, H. Muthali and S. Jacobs. PMOS NBTI-induced circuit mismatch in advanced technologies // Proc. of 2004 IEEE Intern. Reliab. Physics Symposium. Proc., 2004, pp. 171-175.

- [16]. Abhishek Bhattacharjee, Sambhu Nath Pradhan, Impact of Transistor Aging on the Reliability of the Analog Circuit // Proc. of 2020 Intern. Conference on Comput. Performance Evaluation (ComPE), 2020, pp.212-217.

- [17].S. Bhardwaj, W. Wang, R. Vattikonda, Y. Cao and S. Vrudhula, Predictive Modeling of the NBTI Effect for Reliable Design // Proc. of IEEE Custom Integrated Circuits Conference 2006, pp. 189-192.

- [18]. W. Wang, S. Yang, S. Bhardwaj, S. Vrudhula, F. Liu and Y. Cao. The Impact of NBTI Effect on Combinational Circuit: Modeling, Simulation, and Analysis // IEEE Trans. on Very Large Scale Integration (VLSI) Systems, vol. 18, no. 2, 2010, pp. 173-183.

- [19].I. Jianxin Fang and S. S. Sapatneka. Scalable methods for the analysis and optimization of gate oxide breakdown // Proc. of 2010 11-th International Symposium on Quality Electronic Design (ISQED), 2010, pp. 638-645.

- [20].F. Wolff, D. Weyer a, Ch. Papachristou, S.Clay.Design for reliability Tradeoffs between lifetime and performance due to electromigration // Microel. Reliab., 117. 2021. pp. 1-12.

# Expansion of SPICE Simulation Tools Abilities by Taking into Account MOS Circuits Aging Effects Caused by Hot Carriers, Gate Dielectric Breakdown and Electromigration

# I.A. Kharitonov

National Research University "Higher School of Economics" (Moscow Institute of Electronics and Mathematics), ikharitonov@hse.ru

Abstract — Modified SPICE models for MOS FETs with account for aging effects caused by hot carriers and gate dielectric breakdown and electromigration are described. The SPICE simulation tools, modified models and special scripts for model parameters definition are integrated into special subsystem for CMOS circuits reliability analysis and simulation. Examples of SPICE simulation of analog and digital CMOS circuits with account for aging effects are presented.

**Keywords** — CMOS circuits, aging effects, reliability, NBTI, PBTI, HCI, TDDD, electromigration, SPICE models, circuit simulation.

#### REFERENCES

- [1]. B. Bailey. Chip Aging Becomes Design Problem // Semiconductor Engineering, August 9th, 2018 . https://semiengineering.com/chip-aging-becomes-design-problem. (accessed 05.06.2021).

- [2]. T. Mak. Is CMOS More Reliable with Scaling? // Proceedings of the Online Testing Workshop, 2002.

- [3]. Natalia RUIZ. Multilevel aging phenomena analysis in complex ultimate CMOS designs // Thèse pour obtenir le grade de Docteur de L'université De Grenoble. 2012.

- [4]. Pfost, J. Joos, M. Stecher. Compact Modeling and Simulation for Digital Circuit Aging. // Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy. Arizona state university, 2012.

- [5]. E. Maricau, P. De Wit, G. Gielen. An analytical model for hot carrier degradation in nanoscale CMOS suitable for the simulation of degradation in analog IC applications // Microelectronics Reliability, 2008, 48. Pp. 1576-1580.

- [6]. Wenping Wang,, Vijay Reddy, Anand T. Krishnan, Rakesh Vattikonda, Srikanth Krishnan, and Yu Cao, Compact Modeling and Simulation of Circuit Reliability for 65-nm CMOS Technology// IEEE Trans On Device And Mater. Reliability, VOL. 7, NO. 4, December 2007, p. 509.

- [7]. A. Avellán and W. H. Krautschneider. Impact of Soft and Hard Breakdown on Analog and Digital Circuits // IEEE Trans. on Device and Materials Reliability, vol. 4, No. 4, 2004, pp. 677-683.

- [8]. Neeraj K. Jha, P. Sahajananda Reddy, Dinesh K. Sharma, NBTI Degradation and Its Impact for Analog Circuit Reliability// IEEE Trans. on Electron Devices, Vol. 52, N. 12, 2005, pp.2609-2616.

- [9]. R. Vattikonda, Wenping Wang and Yu Cao, "Modeling and minimization of PMOS NBTI effect for robust nanometer design," 2006 43rd ACM/IEEE Design Automation Conference, 2006, pp. 1047-1052.

- [10].A. Avellán and W. H. Krautschneider. Impact of Soft and Hard Breakdown on Analog and Digital Circuits // IEEE Trans. on Device and Materials Reliability, vol. 4, No. 4, 2004, pp. 677-683.

- [11].Petrosyants K.O., Kharitonov I.A. SPICE Simulation of Total Dose and Aging Effects in MOSFET Circuits// Proc. of IEEE East-West Design and Test Simp., 2018, p. 760-765.

- [12]. I.A. Kharitonov, SPICE models for MOSFETS with account for the aging effects // Nanoindustry. Special Issue, 96, 2020. pp. 300-307 (in Russian).

- [13]. Tan, Weidong Liu, Frank Lee. An accurate MOSFET aging model for 28 nm integrated circuit simulation // Microelectronics Reliability, 52 . 2012. Pp. 1565–1570.

- [14].R. Thewes et al., Device reliability in analog CMOS applications // International Electron Devices. Meeting 1999. Technical Digest (Cat. No.99CH36318), 1999, pp. 81-84.

- [15].M. Agostinelli, S. Lau, S. Pae, P. Marzolf, H. Muthali and S. Jacobs. PMOS NBTI-induced circuit mismatch in advanced technologies // Proc. of 2004 IEEE Intl. Reliability Physics Symposium. Proc., 2004, pp. 171-175.

- [16]. Abhishek Bhattacharjee, Sambhu Nath Pradhan, Impact of Transistor Aging on the Reliability of the Analog Circuit // Proc. of 2020 Intern. Conference on Comput. Performance Evaluation (ComPE), 2020, pp.212-217.

- [17].S. Bhardwaj, W. Wang, R. Vattikonda, Y. Cao and S. Vrudhula, Predictive Modeling of the NBTI Effect for Reliable Design // Proc. of IEEE Custom Integrated Circuits Conference 2006, pp. 189-192.

- [18]. W. Wang, S. Yang, S. Bhardwaj, S. Vrudhula, F. Liu and Y. Cao. The Impact of NBTI Effect on Combinational Circuit: Modeling, Simulation, and Analysis // IEEE Trans. on Very Large Scale Integration (VLSI) Systems, vol. 18, no. 2, 2010, pp. 173-183.

- [19].I. Jianxin Fang and S. S. Sapatneka. Scalable methods for the analysis and optimization of gate oxide breakdown // Proc. of 2010 11-th International Symposium on Quality Electronic Design (ISQED), 2010, pp. 638-645.

- [20].F. Wolff, D. Weyer a, Ch. Papachristou, S.Clay. Design for reliability: Tradeoffs between lifetime and performance due to electromigration // Microelectronics Reliability/ 117. 2021. pp. 1-12.