# Арсенид-галлиевые операционные усилители с умножителями крутизны входных дифференциальных каскадов

Н.Н. Прокопенко $^{1,2}$ , О.В. Дворников $^3$ , В.Е. Чумаков $^1$ , Д.В. Клейменкин $^1$

<sup>1</sup> Донской государственный технический университет, г. Ростов-на-Дону, prokopenko@sssu.ru

<sup>2</sup> Институт проблем проектирования в микроэлектронике РАН, г. Зеленоград

<sup>3</sup> ОАО «Минский научно-исследовательский приборостроительный институт», г. Минск

Рассматриваются базовые Аннотаиия схемотехнические решения операционных усилителей (ОУ), ориентированные на изготовление на одном GaAs кристалле полевых транзисторов (field effect transistor, FET) со встроенным каналом n-типа и транзисторов. Предлагается перспективная архитектура трехкаскадного ОУ на основе рНЕМТ (pseudo morphic high electron mobility transistor) и p-n-р НВТ (hetero junction bipolar transistor), в которой реализуются малые значения систематической составляющей напряжения смещения нуля, обусловленной влиянием токов базы ртранзисторов температурными его радиационными изменениями. Исследуется варианта построения входных каскадов, в которых предусмотрено увеличение на 1-2 порядка крутизны усиления при работе рНЕМТ в микроамперных диапазонах токов (10-100 мкА).

Ключевые слова — операционный усилитель, GaAs pHEMT, GaAs p-n-p HBT, напряжение смещения нуля, крутизна усиления дифференциального каскада.

#### I. Введение

Анализ тенденций создания совершенствования существующих технологических маршрутов изготовления аналоговых микросхем перспективность арсенид-галлиевых показывает обеспечивающих работоспособность технологий. широком аналоговых микросхем В диапазоне температурных и радиационных воздействий [1-5].

Совмещенные в рамках одной технологии арсенидгаллиевые FET и p-n-p/n-p-n транзисторы созданы несколькими фирмами [6-9]. В настоящее время Минский НИИ радиоматериалов Академии наук Белоруссии разрабатывает подобный технологический процесс (https://mniirm.by/).

При работе GaAs FET в микрорежиме, т.е при токах стока 10-100 мкА, приходится принимать специальные меры по повышению крутизны усиления входного дифференциального каскада (ДК), в т.ч. описанные в статьях [10, 11]. Традиционное последовательное включение двух-трех классических ДК для увеличения разомкнутого коэффициента усиления ОУ по напряжению не всегда реализуемо при малых напряжениях питания [12].

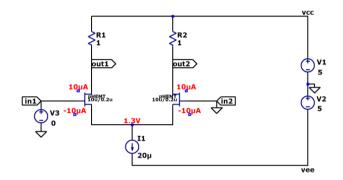

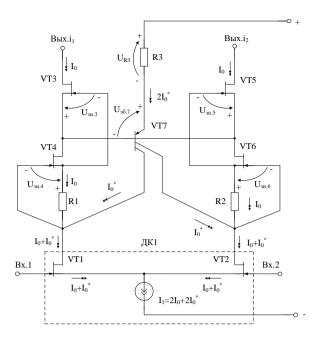

На рис. 1 представлена проходная характеристика классического дифференциального каскада на рНЕМТ GaAs транзисторах при токах стока 10 мкA.

Рис. 1. Статический режим GaAs дифференциального каскада в среде LTSpice при  $I_1$ =20 мкA (а) и зависимость выходных токов ДК от входного напряжения (б)

Как следует из графиков на рис. 16, при токе стока входных транзисторов 10 мкА крутизна дифференциального каскада не превышает  $0.2 \cdot 10^{-3}$  А/В, а при токе общей истоковой цепи в 200 мкА она увеличивается до  $0.7 \cdot 10^{-3}$  А/В. Кроме этого, диапазон активной работы данного FET ДК (напряжение ограничения  $U_{\rm rp}$  [12]), существенно влияющий на максимальную скорость нарастания выходного напряжения ОУ, составляет порядка  $U_{\rm rp}$ =90 мВ. Это практически совпадает с  $U_{\rm rp}$  каскадов на биполярных транзисторах [12].

Цель и новизна настоящей статьи состоит в рассмотрении перспективной архитектуры ОУ на GaAs FET и p-n-р транзисторах, а также новых (в сравнении с [13-15]) примеров построения входных ДК, в которых предусмотрены интегральные схемотехнические решения классического входного параллельно-балансного каскада и специальных схем умножения его крутизны.

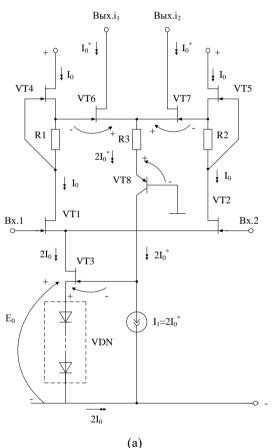

#### II. Типовая архитектура GaAs операционного усилителя

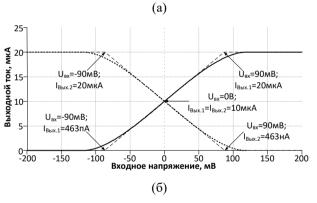

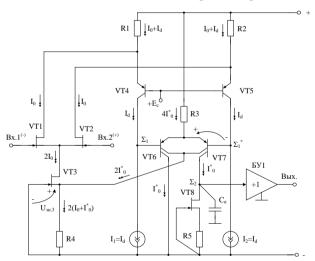

Перспективная обобщенная схема ОУ на GaAs FET и р-п-р транзисторах приведена на рис. 2. Операционный усилитель содержит классический входной дифференциальный каскад ДК1, вместо которого желательно применение специальных ДК с умножением крутизны усиления, в т.ч. предложенных нами в [13-15]. ДК1 имеет токовые выходы (Вых.і1, Вых.і2), согласованные с положительной шиной источника питания. Промежуточный каскад ОУ реализован на транзисторе VT6, а источники опорного тока в схеме рис. 2 выполнены на FET транзисторах VT3, VT7.

Рис. 2. Рекомендуемая архитектура операционного усилителя на GaAs FET и p-n-p транзисторах

Замечательная особенность схемы на рис. 2, в отличие от многих других известных архитектур ОУ с другими промежуточными каскадами и другими токовыми зеркалами (ПТ1), состоит в том, что здесь систематическая составляющая напряжения смещения нуля ( $U_{cm}$ ) может не зависеть от абсолютных значений коэффициента усиления по току базы  $\beta$  идентичных биполярных транзисторов VT4, VT5, VT6, а также от их идентичных температурных и радиационных изменений. Действительно, для высокоимпедансного узла  $\Sigma_1$  ОУ (рис. 2) можно составить следующие уравнения по первому закону Кирхгофа

$$I_{\kappa 4} = I_0 - 2I_{6n}, I_{34} = I_{35} = I_0 - I_{6n}, I_{\kappa 5} = I_0 - 2I_{6n}, I_p = I_{\kappa 5} + 2I_{6n} - I_0 \approx 0,$$

(1)

где  $I_{\kappa i} \left( I_{\ni i} \right)$  — ток коллектора (эмиттера) і-го транзистора,

$I_{6n}$  — статический ток базы p-n-p транзисторов при  $I_{n}=I_{0}$ .

$I_p$  — разностный ток в узле  $\Sigma_1$ , определяющий уровень систематической составляющей напряжения смещения нуля, обусловленный влиянием  $\beta$  транзисторов. Причем  $U_{\rm cm} = I_{\rm p}/G_{\rm ДK}$ , где  $G_{\rm ДK}$  - крутизна усиления входного каскада.

Таким образом, в высокоимпедансном узле  $\Sigma_1$  ОУ на рис. 2 обеспечивается взаимная компенсация выходного тока токового зеркала ПТ1, тока базы транзистора VT6 и выходного тока ДК1. Если в схеме с высокой точностью обеспечить  $U_{\kappa 6} \approx 0$  для транзистора VT5, то это станет первым необходимым условием минимизации  $U_{\rm cm}$ , которое при идентичных VT4, VT5, VT6 сводится к идентичному построению источников опорного тока (ИОТ) на транзисторах VT3, VT7, для которых сопротивления резисторов R1 и R2 должны быть идентичными.

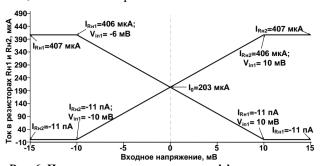

#### III. ОСНОВНЫЕ МОДИФИКАЦИИ ВХОДНЫХ КАСКАДОВ С УМНОЖИТЕЛЕМ КРУТИЗНЫ

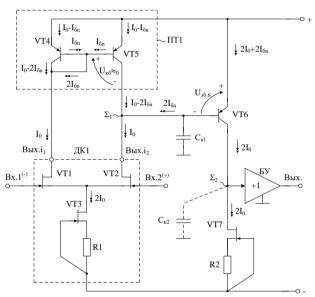

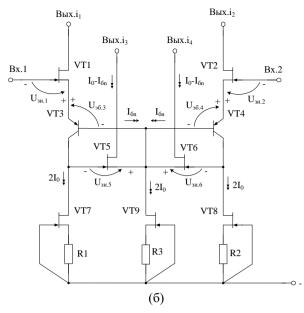

В схеме ДК на рис. З введена отрицательная обратная связь (ООС) по синфазному сигналу, которая обеспечивается транзистором VT7. За счет выбора источника опорного напряжения Е<sub>0</sub> (стабилитрона, р-п переходом, нескольких или простейших устанавливается транзисторных стабилизаторов) постоянной заданный уровень составляющей напряжения на базе VT7:

$$U_{67} = V_{dd} - U_{96.7} - E_0. (2)$$

Резисторы R1 и R2 определяют статический ток стока транзисторов VT1 и VT2 ( $I_c = I_0 = U_{3и.4}/R_1$ ). В качестве источника опорного тока  $I_1$  целесообразно использовать три параллельно включенных каскодных ИОТ с R3=R2=R1 (рис. 36).

Изменение напряжения на входе Bx.1 схемы рис. За на величину  $u_{\text{вх}}$  преобразуется в приращение тока стока VT1, который создает в первом высокоимпедансном узле  $\Sigma_1$  приращение напряжения

$$u_{\Sigma 1} = R_{i\Sigma 1} G_{\text{JK}},\tag{3}$$

где  $R_{i\Sigma 1}$  — эквивалентное сопротивление в высокоимпедансном узле  $\Sigma_1$ ;

$G_{\text{ДК}}$  — эквивалентная крутизна усиления входного ДК на транзисторах VT1, VT2.

Напряжение  $u_{\Sigma 1}$  с единичным коэффициентом передается в цепь истока VT4 и далее вызывает изменения тока стока VT3 и выходного тока ДК:

$$i_{\text{BMX},1} \approx i_{c3} \approx u_{\Sigma 1} / (S_3^{-1} + S_5^{-1}),$$

(4)

где  $S_3$ ,  $S_5$  - крутизна стоко-затворных характеристик VT3, VT5.

Как следствие эффективная крутизна  $G_{\rm JK}^*$  входного каскада на рис. За существенно превышает крутизну  $G_{\rm JK}$  простейшего ДК на GaAs транзисторах (рис. 1)

$$G_{\text{ДК}}^* = R_{i\Sigma 1} G_{\text{ДK}} \frac{S_3 S_5}{S_3 + S_5} = \frac{i_{\text{ВЫХ.1}}}{u_{\text{BX}}}.$$

(5)

Причем

$$R_{i\Sigma 1} \approx (S_1^{-1} + S_2^{-1})\mu_1^{-1},$$

(6)

где  $\mu_1^{-1}=10^{-2}\div 10^{-3}$  - коэффициент внутренней обратной связи транзистора VT1 в схеме с общим затвором, учитывающий влияние его напряжения затвор-сток на смещение стоко-затворной характеристики при токе истока  $I_s$ = $I_0$ =const.

Рис. 3. GaAs входной ДК с умножителем крутизны (a) и схема источника опорного тока  $\mathbf{I}_1$  (б)

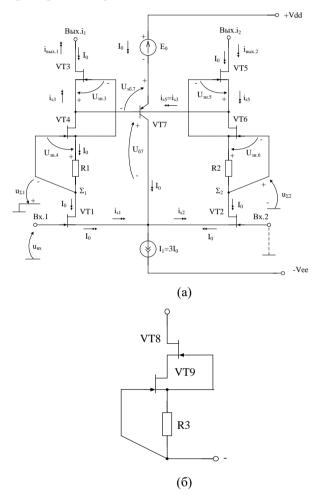

Основное отличие схемы ДУ на рис. 4 от схемы ДК на рис. 3 - несколько другое введение ООС - в цепь стока транзисторов VT1, VT2 с помощью транзисторов VT7, а также применение в качестве  $E_0$  резистора R3. В данной схеме входной дифференциальный каскад может быть выполнен по другим более сложным параллельно-балансным структурам [12].

Рис.4. Входной дифференциальный каскад с ООС по цепям стока входных транзисторов VT1, VT2

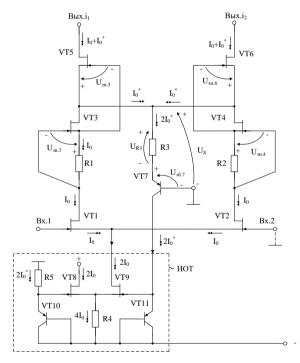

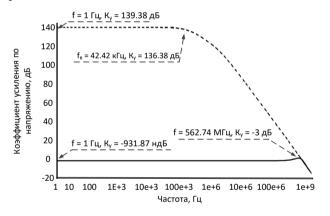

В схеме на рис. 5 ООС, стабилизирующая уровень постоянного напряжения на истоках транзисторов VT5 и VT6 ( $U_S$ ), вводится через ИОТ в общей истоковой цепи. Причем  $U_S = U_{96.7} + 2I_0^*R_3$ , где  $U_{96.7}$  – напряжение эмиттер-база VT7,  $2I_0^*$  - выходной ток ИОТ.

Рис. 5. Входной ДК с ООС по цепи источника опорного тока ИОТ

На рис. 6 показана проходная характеристика ДК рис. 5, из которого следует, что крутизна  $G^*_{\ \ ДK}$  в модифицированной схеме при идентичных токах стока

$(I_c=200 \ {\rm MkA})$  увеличивается с 0,7·10<sup>-3</sup> A/B до 67,6·10<sup>-3</sup> A/B, т.е. почти в 100 раз.

Рис. 6. Проходные характеристики дифференциального каскада на рис. 5

схеме на рис. 7a используется другой схемотехнический введения OOC прием синфазному сигналу, необходима которая ДЛЯ обеспечения заданного статического режима. Здесь в качестве источника опорного напряжения Е<sub>0</sub>>U<sub>3и,3</sub> могут использоваться прямосмещенные р-п переходы простейшие транзисторные стабилизаторы напряжения.

Рис. 7. Дифференциальные усилители с умножителями крутизны

## IV. GAAS ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ С ПОВЫШЕННЫМ РАЗОМКНУТЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ

В тех случаях, когда в ОУ необходимо получить повышенные значения Ку необходимо применять схемы с несколькими высокоимпедансными узлами, например, схему на рис. 8.

Рис. 8. GaAs операционный усилитель с повышенным коэффициентом усиления по напряжению

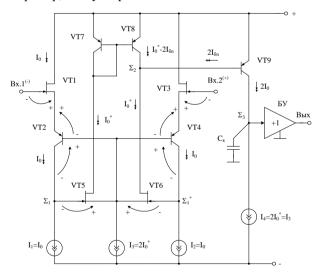

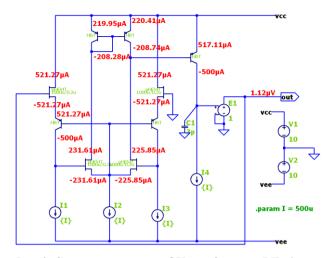

Рис. 9. Статический режим ОУ рис. 8 в среде LTspice с использованием моделей GaAs pHEMT и p-n-p HBT при  $I_1=I_2=I_3=I_4=500~{\rm m}{\rm \kappa}A$

Особенность схемы ОУ – малый уровень систематической составляющей напряжения смещения нуля (1,12 мкB), что обеспечивается рассмотренным ранее эффектом взаимной компенсации токов базы р-n-р биполярных транзисторов в высокоимпедансном узле  $\Sigma 1$  (рис. 2, формулы (1)).

Логарифмическая амплитудно-частотная характеристика (ЛАЧХ) коэффициента усиления по напряжению разомкнутого ОУ рис. 9 приведена на рис. 10.

Рис. 10. ЛАЧХ коэффициента усиления по напряжению ОУ на рис. 9

Таким образом, рассмотренная схема ОУ на рис. 9 обеспечивает экстремально высокие значения коэффициента усиления (около 140 дБ), что достаточно для многих применений.

#### V. ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ С УМНОЖИТЕЛЯМИ КРУТИЗНЫ В ПРОМЕЖУТОЧНЫХ КАСКАДАХ

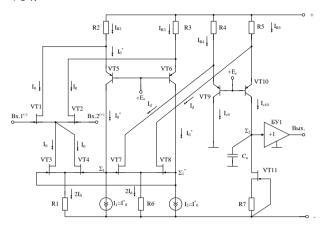

Предлагаемая ниже схема ОУ (рис. 11) содержит умножитель крутизны усиления в промежуточном «перегнутом» каскоде, который выполнен на транзисторах VT7, VT8. Второй промежуточный «перегнутый» каскод реализован на биполярных транзисторах VT9, VT10, а также источнике опорного

тока на транзисторе VT11. Схема ОУ на рис. 11 имеет два высокомпедансных узла  $\Sigma_1$  ( $\Sigma_1^*$ ) и  $\Sigma_2$ , что позволяет получить повышенный коэффициент усиления по напряжению. Отрицательная обратная связь по выходному синфазному сигналу первого «перегнутого» каскода вводится для стабилизации статического режима с помощью транзисторов VT3, VT4.

Рис. 11. GaAs операционный усилитель на двух «перегнутых» каскодах

В схеме на рис. 12 отрицательная обратная связь по выходному синфазному сигналу «перегнутого» каскода вводится через источник опорного тока на транзисторе VT3. Источники опорного тока  $\rm I_1$  и  $\rm I_2$  в данном ОУ выполняются на FET транзисторах.

Рис. 12. Операционный усилитель с двумя высокоимпедансными узлами

Особенность схем ОУ на рис. 11 и рис. 12 состоит в том, что в них не применяются токовые зеркала, реализация которых на FET со встроенным каналом затруднена.

#### VI. ЗАКЛЮЧЕНИЕ

Рассмотрены перспективные схемотехнические решения арсенид-галлиевых операционных усилителей на FET с встроенным каналом n-типа и p-n-p

биполярных транзисторах, которые рекомендуются для построения аналоговых микросхем с малым статическим током потребления и повышенным коэффициентом усиления по напряжению.

Компьютерное моделирование дифференциальных каскадов с умножителями крутизны показывает, что данный схемотехнический прием более перспективен, чем последовательное включение нескольких классических ДК, которые часто используются для увеличения разомкнутого коэффициента усиления.

#### Поддержка

Исследование выполнено за счет гранта Российского научного фонда (проект No. 18-79-10109- $\Pi$ ).

#### Литература

- [1] Hibi Y. et al. Cryogenic ultra-low power dissipation operational amplifiers with GaAs JFETs //Cryogenics. 2016. T. 73. C. 8-13

- [2] Fujiwara M., Sasaki M. Performance of GaAs JFET at a cryogenic temperature for application to readout circuit of high-impedance detectors //IEEE transactions on electron devices. 2004. T. 51. №. 12. C. 2042-2047

- [3] Fujiwara M., Sasaki M., Akiba M. Reduction method for low-frequency noise of GaAs junction field-effect transistor at a cryogenic temperature //Applied physics letters. – 2002. – T. 80. – №. 10. – C. 1844-1846

- [4] Shur M. S. GaAs devices and circuits. Springer Science & Business Media, 2013.

- [5] Кульчицкий Н. А., Наумов А. В., Старцев В. В. Новые тенденции развития рынка приборов на арсениде галлия //Успехи прикладной физики. – 2020. – Т. 8. – №. 2. – С. 137.

- [6] J. Y. Yang, F. J. Morris, D. L. Plumton, and E. N. J. Jeffrey, "GaAs BIJFET technology for linear circuits," in Dig. 1989 GaAs IC Symp., pp. 341–344

- [7] F.J. Morris, D. L. Plumton, J.-Y. Yang, H.-T. Yuan, "Integrated circuit composed of group III-V compound field effect and bipolar semiconductors", US Patent 5.068.756, Nov. 26, 1991

- [8] D.L. Plumton, F. J. Morris, J.-Y. Yang, "Method to integrate HBTs and FETs", US Patent 5.077.231, Dec. 31, 1991

- [9] Brian Moser, W. Wohlmuth, S. Nedeljkovic, W. Clausen, D. Halchin, R. Vass, and M. Fresina, "An InGaP/GaAs HBT/JFET BiFET technology for PA bias circuit applications", CS MANTECH Conference, April 14-17, 2008, Chicago, Illinois, USA, pp.1-4

- [10] Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. Арсенидгаллиевый аналоговый базовый кристалл // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2021. Выпуск 2. С. 47-54. doi:10.31114/2078-7707-2021-2-47-54

- [11] О.В. Дворников, А.А. Павлючик, Н.Н. Прокопенко, В.А. Чеховский, А.В. Кунц, В.Е. Чумаков. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем // Известия высших учебных заведений. Электроника. Т.27. №4, 2022 г.

- [12] Н.Н.Прокопенко. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222 с.

- [13] N. N. Prokopenko, V. E. Chumakov, I. V. Pakhomov, A. V. Bugakova, R. K. Khubiev and A. V. Avilov, "Circuit Design of CJFET OPA Based on the Differential Stage with a Slope Multiplier," 2021 29th Telecommunications Forum (TELFOR), 23-24 November 2021, Belgrade, Serbia, pp. 1doi: 10.1109/TELFOR52709.2021.9653418 (Схемотехника **CJFET** OPA Основе на Дифференциального Каскада Умножителем Крутизны)

- [14] N. N. Prokopenko, V. E. Chumakov, I. V. Pakhomov, A. V. Bugakova, D. Y. Denisenko and I. L. Vialikov, "Gallium-Arsenide JFET Op-Amp with High Open-Loop Gain," 2021 29th Telecommunications Forum (TELFOR), 23-24 November 2021, Belgrade, Serbia, pp. 1-4, doi: 10.1109/TELFOR52709.2021.9653228 (Gallium-Arsenide JFET Op-Amp с повышенным разомкнутым усилением)

- [15] Савченко Е.М., Прокопенко Н.Н., Чумаков В.Е., Пронин А.А., Дроздов Д.Г. Арсенид-галлиевый дифференциальный каскад с умножителем крутизны усиления: заявка на патент № 2022107168; заявл. 17.03.2022 (1000в)

### Gallium Arsenide Operational Amplifiers with Transconductance Multipliers of Input Differential Stages

N.N. Prokopenko<sup>1,2</sup>, O.V. Dvornikov<sup>3</sup>, V.E. Chumakov<sup>1</sup>, D.V. Kleimenkin<sup>1</sup>

<sup>1</sup> Don State Technical University (Rostov-on-Don, Russia), prokopenko@sssu.ru

<sup>2</sup>Institute for Design Problems in Microelectronics RAS (Zelenograd, Russia)

<sup>3</sup> Minsk Research Instrument-Making Institute JSC (MNIPI JSC) (Minsk, Republic of Belarus)

Abstract — The basic circuit solutions of operational amplifiers (Op-Amps), focused on the production of field effect transistors (FET) with integrated n-type channel and p-n-p transistors on a GaAs chip, are considered. A perspective three-cascade Op-Amp based on pHEMT (pseudo morphic high electron mobility transistor) and p-n-p

HBT (hetero junction bipolar transistor) in which small systematic components of input offset voltage caused by the influence of base currents of p-n-p transistors and its temperature and radiation variations are realized are proposed. Three variants of construction of input cascades are investigated, in which an increase by 1-2 orders of

magnitude of transconductance of amplification during pHEMT operation in microampere ranges of currents (10-100  $\mu A)$  is provided. A mathematical analysis of the recommended operational amplifier architecture on GaAs FETs and p-n-p transistors is given. The mathematical analysis of the main modifications of the input stages with a transconductance multiplier is described. The results of computer simulation of GaAs operational amplifier with increased gain using GaAs pHEMT and p-n-p HBT models are presented. The logarithmic amplitude-frequency response of the voltage gain of the proposed op-amp is studied.

Keywords — operational amplifier, GaAs pHEMT, GaAs pn-p HBT, input offset voltage, the transconductance of the differential cascade gain.

#### REFERENCES

- [1] Hibi Y. et al. Cryogenic ultra-low power dissipation operational amplifiers with GaAs JFETs //Cryogenics. – 2016. – T. 73. – C. 8-13

- [2] Fujiwara M., Sasaki M. Performance of GaAs JFET at a cryogenic temperature for application to readout circuit of high-impedance detectors //IEEE transactions on electron devices. – 2004. – T. 51. – №. 12. – C. 2042-2047

- [3] Fujiwara M., Sasaki M., Akiba M. Reduction method for low-frequency noise of GaAs junction field-effect transistor at a cryogenic temperature //Applied physics letters. – 2002. – T. 80. – №. 10. – C. 1844-1846

- [4] Shur M. S. GaAs devices and circuits. Springer Science & Business Media, 2013.

- [5] N. A. Kulchitsky, A. A. Naumov. V., Startsev V. V. Novye tendencii razvitiya rynka priborov na arsenide galliya (New tendencies of development of gallium arsenide devices market) // Proc. of Applied Physics. - 2020. - T. 8. - №. 2. p. 137. (in Russian)

- [6] J. Y. Yang, F. J. Morris, D. L. Plumton, and E. N. J. Jeffrey, "GaAs BIJFET technology for linear circuits," in Dig. 1989 GaAs IC Symp., pp. 341–344

- [7] F.J. Morris, D. L. Plumton, J.-Y. Yang, H.-T. Yuan, "Integrated circuit composed of group III-V compound field effect and bipolar semiconductors", US Patent 5.068.756, Nov. 26, 1991

- [8] D.L. Plumton, F. J. Morris, J.-Y. Yang, "Method to integrate HBTs and FETs", US Patent 5.077.231, Dec. 31, 1991

- [9] Brian Moser, W. Wohlmuth, S. Nedeljkovic, W. Clausen, D. Halchin, R. Vass, and M. Fresina, "An InGaP/GaAs HBT/JFET BiFET technology for PA bias circuit applications", CS MANTECH Conference, April 14-17, 2008, Chicago, Illinois, USA, pp.1-4

- [10] Dvornikov O.V., Pavlyuchik A.A., Prokopenko N.N., Chekhovsky V.A., Kunz A.V., Chumakov V.E. Arsenidgallievyj analogovyj bazovyj kristall (Arsenide Gallium Analog Base Crystal) // Problems of Advanced Micro- and Nanoelectronic Systems Development (MES). 2021. Issue 2. p. 47-54. doi:10.31114/2078-7707-2021-2-47-54 (in Russian)

- [11] O.V. Dvornikov, A.A. Pavlyuchik, N.N. Prokopenko, V.A. Chehovsky, A.V. Kuntz, V.E. Chumakov Unificirovannye skhemotekhnicheskie resheniya analogovyh arsenidgallievyh mikroskhem (Unified circuit solutions for analog arsenide-gallium microcircuits) // Proceedings of higher educational institutions. Electronics. Vol. 27. №4, 2022. (in Russian)

- [12] N.N. Prokopenko. Nelinejnaya aktivnaya korrekciya v precizionnyh analogovyh mikroskhemah: monografiya (Nonlinear Active Correction in Precision Analog Microcircuits: Monograph) / Rostov-on-Don: North Caucasus Research Center of Higher School, 2000. 222 p. (in Russian)

- [13] N. N. Prokopenko, V. E. Chumakov, I. V. Pakhomov, A. V. Bugakova, R. K. Khubiev and A. V. Avilov, "Circuit Design of CJFET OPA Based on the Differential Stage with a Slope Multiplier," 2021 29th Telecommunications Forum (TELFOR), 23-24 November 2021, Belgrade, Serbia, pp. 1-4, doi: 10.1109/TELFOR52709.2021.9653418 (CJFET OPA circuitry based on a differential cascade with a multiplier)

- [14] N. N. Prokopenko, V. E. Chumakov, I. V. Pakhomov, A. V. Bugakova, D. Y. Denisenko and I. L. Vialikov, "Gallium-Arsenide JFET Op-Amp with High Open-Loop Gain," 2021 29th Telecommunications Forum (TELFOR), 23-24 November 2021, Belgrade, Serbia, pp. 1-4, doi: 10.1109/TELFOR52709.2021.9653228 (Gallium-Arsenide JFET Op-Amp with increased open amplification)

- [15] Savchenko E.M., Prokopenko N.N., Chumakov V.E., Pronin A.A., Drozdov D.G. Arsenid-gallievyj differencial'nyj kaskad s umnozhitelem krutizny usileniya (Arsenide-gallium differential cascade with a gain steepness multiplier): Patent application No. 2022107168; applied for patent No. 2022107168. 17.03.2022 (1000v). (in Russian)